关于处理FPGA输出时钟和数据的方法介绍

FPGA/ASIC技术

211人已加入

描述

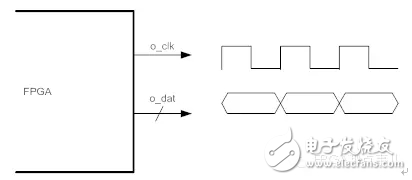

在FPGA的源同步的系统设计中,常常我们会碰到把随路时钟和数据一同输出的情形,如同下面的系统:

在这样的系统中,要求输出时钟o_clk和o_dat要由严格的相位对齐关系,一般是边沿对齐或者中心对齐。

那么如何才能保证上述相位对齐关系呢?

(1) 第一种做法(这样用的人不少)。

对于数据,通常用系统时钟打一拍或者不打拍,组合逻辑直接输出。

对于时钟,通常直接把FPGA内部的系统时钟赋值到IO PAD的输出管脚上。

如下所示:

assign O_CLK = sys_clk;

always@(posedge sys_clk)

o_dat= data_i;

// or assign O_dat =data_i;

这样的处理方式,需要约束文件里面通过offset out(UCF,SDC类似)约束输出时钟和数据的相位关系。

上面的处理方式其实对于FPGA不是最优选择。而且对于时钟直接赋值输出的处理方式,在某些器件上还会产生错误!更好的处理方式是下面第2中:

(2) 第二种做法

对于输出的数据,无论如何都要做到最终送到IO PAD时,是寄存器输出。这样我们可以把寄存器约束到IOPAD里面的IO LOGIC里面,保证所有数据输出延迟的一致性。

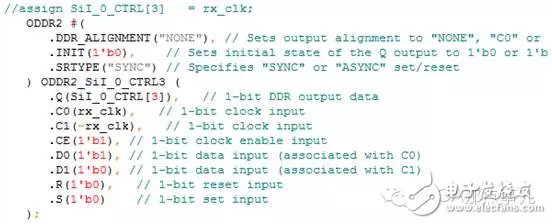

对于时钟,通过类似ODDR2的元件来产生一个时钟镜像输出:

这样的处理方式,不管是数据,还是时钟,实际上都是寄存器输出,而且都可以把它们放置到IO PAD里面,保证了时钟和所有数据相对相位关系的一致性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 5265

-

关于跨时钟域信号的处理方法2022-10-09 8545

-

FPGA设计中有多个时钟域时如何处理?2012-02-24 3624

-

简谈异步电路中的时钟同步处理方法2018-02-09 6554

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2396

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 2390

-

三种跨时钟域处理的方法2021-01-08 2342

-

FPGA初学者的必修课:FPGA跨时钟域处理3大方法2021-03-04 3939

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1717

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14832

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2661

-

介绍3种方法跨时钟域处理方法2021-09-18 23583

-

FPGA跨时钟域处理方法(二)2023-05-25 1863

-

关于FPGA设计中多时钟域和异步信号处理有关的问题2023-08-23 1622

-

FPGA异步信号处理方法2024-07-17 2756

全部0条评论

快来发表一下你的评论吧 !