关于赛灵思FPGA实现高效并行实时上采样的分析和介绍

FPGA/ASIC技术

211人已加入

描述

许多信号处理应用都需要上采样。从概念上来讲,最简单的方法是,对一组向量数据进行M倍上采样可以将该向量数据的离散傅里叶变换(DFT)进行补零处理,插入实际频率分量的(M-1)倍个零后再将补零的向量数据变换回时域。这种方法的计算代价较高,在FPGA中实现时效率也不高。这里提出了一种高效、并行的实时上采样电路,每个ADC时钟生成M个上采样值,其中M是所期望的上采样因子。我们在赛灵思公司的Virtex-6 XC6VLX75T FPGA上实现了一个M为4的上采样,以作为这种通用技术的一个示例。

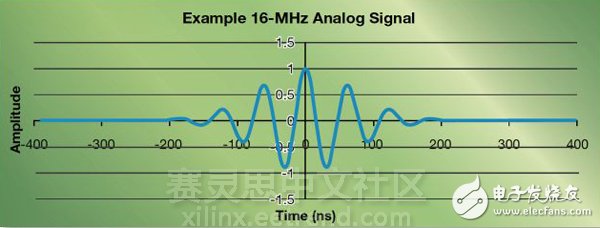

我们的并行上采样技术基于称为“加窗Sinc插值”的概念,有一些优秀文献对其作了详细描述。为便于说明,考虑图1示例子中的16 MHz模拟信号。

图1——用于说明该上采样过程的16-MHz信号示例

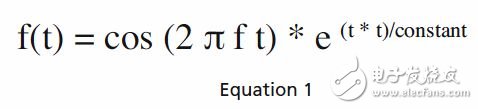

该信号可以用下式表示:

如果对图1所示的信号进行采样/量化,在80Mhz时使用驱动到其满量程输入范围97.7%的一个12位ADC,每个信号周期只采样5次,生成如图2所示的样本数据序列。以因子4对该示例数据序列进行上采样,达到320MHz的有效采样率,可在每一信号周期内提供20个样本。虽然这里描述的方法可以采用更大的上采样因子,但为便于说明,这里的上采样因子M = 4。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

790.赛灵思被并入AMD对中国FPGA厂商有什么意义?小凡 2022-10-05

-

采用FPGA实现DisplayPort详细教程【赛灵思内部资料】2012-03-01 11249

-

玩转FPGA,赛灵思FPGA设计大赛开赛啦2012-04-23 24065

-

赛灵思Verilog(FPGACPLD)设计小技巧2012-08-19 2567

-

玩转FPGA 赛灵思(xilinx)FPGA设计大赛获奖名单!!!2012-09-06 12002

-

FPGA是用altera多还是赛灵思的多呢2016-01-09 16257

-

基于赛灵思FPGA的卷积神经网络实现设计2019-06-19 4245

-

怎么利用赛灵思FGPA实现降采样FIR滤波器?2019-08-15 2872

-

如何使用赛灵思FPGA加速包处理?2021-04-30 1813

-

赛灵思Spartan FPGA高清视频参考设计,轻松实现“即2010-01-29 1046

-

基于赛灵思Spartan-3A的视频分析2012-05-16 1635

-

使用Virtex-6器件和免费WebPACK工具实现实时四倍上采样的方法2017-11-18 1947

-

从赛灵思FPGA设计流程看懂FPGA设计2018-02-20 17083

-

关于赛灵思FPGA简述2019-07-27 7102

-

使用FPGA实现高效并行实时上采样2023-06-08 2575

全部0条评论

快来发表一下你的评论吧 !