ROM存储1/4周期正弦信号构造DDS详解

电子说

描述

Matlab仿真

注意:由于采用了1/4周期存储,要求整个周期的数值是中心对称的,半个周期的数值是轴对称的。这就意味着采样点中不应该有0值得存在。

Matlab仿真——ROM表存储数据

%% ROM产生 (无符号数)

ROM_N=2^10; %ROM表深度

DATA_L=14; %ROM位宽

t=1:ROM_N;

y=(2^DATA_L-1)*(sin(2*pi*(t-0.5)/ROM_N/4));%-0.5保证对称性

ROM_DATA=round(y);

Matlab仿真——DDS程序(请原谅我没有用case……)

%% 正弦波dds产生

F_CLK=10*10^6; %时钟频率10M

PINC_IN_L=32; %增量长度

DDS_CLK=10*10^3; %dds输出频率10k

PHASE_IN=0; %初始相位

pinc=round(DDS_CLK*2^PINC_IN_L/F_CLK); %相位增量

SIM_L=4000; %仿真长度

phase=PHASE_IN+pinc*(0:SIM_L-1);

addr=mod((floor(phase/2^PINC_IN_L*ROM_N)),ROM_N*4);

flag=floor(addr/ROM_N);

dds_out=1:SIM_L;

for i=1:SIM_L

if(flag(i)==0)

dds_out(i)=ROM_DATA(addr(i)+1);

else if(flag(i)==1)

dds_out(i)=ROM_DATA(2047-addr(i)+1);

else if(flag(i)==2)

dds_out(i)=-ROM_DATA(addr(i)-2048+1);

else

dds_out(i)=-ROM_DATA(4095-addr(i)+1);

end

end

end

end

plot(dds_out);

3.DDS的解释

Xilinx的DDS核的User Guide中队DDS做了很详细的说明,本节不再重复此内容,本节将叙述一种全新的DDS理解方式。这种理解方式解决了频率控制字长于ROM表深度时DDS的理解上的问题。

连续还是离散?

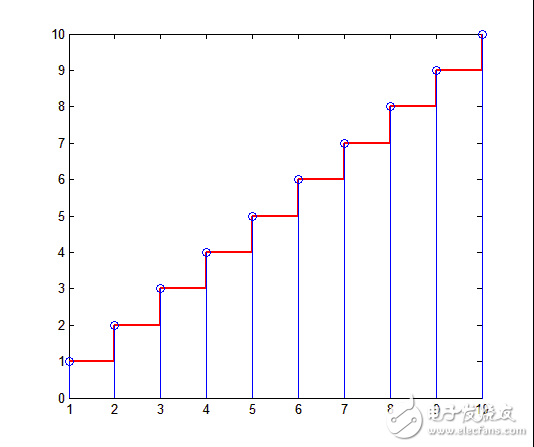

连续还是离散,在于我们用什么眼光去看待。如下图所示,我们可以理解蓝色的图是离散的,而红色的线是连续的。然而,对于我们要获取的信息而言,这两幅图是完全没有区别的。抽样定理中有理想抽样和平顶抽样(采样保持电路)之分,然而在频域效果上,是并没有很大区别的。

ROM表存储的是连续的数值

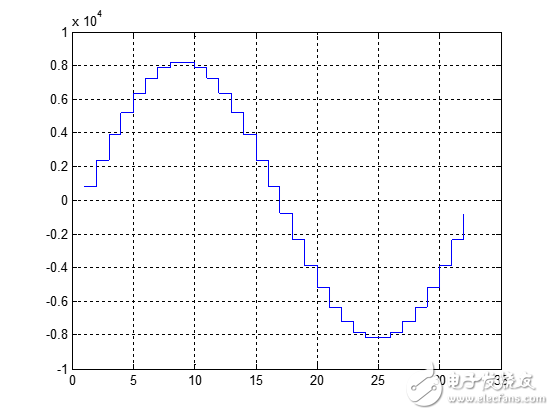

按照上面的理论,可以认为ROM表中存储的是正弦信号的平顶采样结果。如下图所示(一个全周期的ROM表,对称性满足1/4周期存储的要求)

上图的频谱在信号与系统中有提及,上述波形的形成方式可以认为是在乘以周期为T的冲击函数,之后卷积一个宽度为T的窗函数。对应可以求得其频域。(具体可参考平顶抽样)

频率控制字

频率控制字控制对上述的阶梯函数的采样,如果这样理解的话,就没有所谓的相位截取取ROM表的值的疑惑了。频谱图能够清晰的表现这一过程,然而由于blog表达不便,此处不做详细说明。

此处能够解释DDS产生的杂散。

4.Verilog实现

老师教导我们,Verilog和Matlab代码应该是完全一致的,也就是说程序的思路,命名是一样的。但是下面的程序没有做到一致性……

`timescale 1ns / 1ps

module DDS_10k(

input clk_10M,

input rst,

output[13:0] D_SIN,

output[13:0] D_COS

);

parameter pinc=32‘d4294967; //10k

reg[31:0] addr_temp=32’d0;

reg[9:0] addra,addrb;

reg mark_a,mark_b;

always@(posedge(clk_10M)) //复位

begin

if(rst==0)

addr_temp《=32‘d0;

else

addr_temp《=addr_temp+pinc;

end

always@(posedge(clk_10M)) //1/4周期控制

begin

case(addr_temp[31:30])

2’b00:

begin

addra《=addr_temp[29:20];

mark_a《=0;

addrb《=~addr_temp[29:20];

mark_b《=0;

end

2‘b01:

begin

addra《=~addr_temp[29:20];

mark_a《=0;

addrb《=addr_temp[29:20];

mark_b《=1;

end

2’b10:

begin

addra《=addr_temp[29:20];

mark_a《=1;

addrb《=~addr_temp[29:20];

mark_b《=1;

end

2‘b11:

begin

addra《=~addr_temp[29:20];

mark_a《=1;

addrb《=addr_temp[29:20];

mark_b《=0;

end

endcase

end

//ROM表读取

ROM_SIN_1k18 rom_dds (

.clka(clk_10M), // input clka

.addra(addra), // input [9 : 0] addra

.douta(D_SIN[12:0]), // output [12 : 0] douta

.clkb(clk_10M), // input clkb

.addrb(addrb), // input [9 : 0] addrb

.doutb(D_COS[12:0]) // output [12 : 0] doutb

);

reg sin_mark_temp;

reg cos_mark_temp;

assign D_SIN[13]=sin_mark_temp;

assign D_COS[13]=cos_mark_temp;

//此处ROM没有添加register,因此输出和地址有一个周期的延时,故Mark也要有一周期延时

always@(posedge(clk_10M))

begin

sin_mark_temp《=mark_a;

cos_mark_temp《=mark_b;

end

-

新型DDS器件产生正弦波信号和各种调制信号的设计2012-01-10 7962

-

DDS正弦信号发生器2012-02-23 7556

-

用Verilog通过DDS合成正弦波信号2014-03-22 48135

-

基于FPGA的三相正弦DDS电路的设计与实现2018-10-18 1632

-

请问有能直接产生特殊波形信号的DDS芯片吗?2018-12-10 3045

-

基于DDS原理和FPGA技术的基本信号发生器设计2019-06-21 2043

-

浅析DDS信号发生器2021-08-04 1169

-

非正弦周期电路的分析2009-07-08 770

-

高精度DDFS信号源FPGA实现2010-12-11 807

-

非正弦周期信号的分解与合成2008-09-24 14827

-

正弦周期信号的频谱分析2009-05-10 8844

-

非正弦周期信号电路的稳态计算2009-07-27 3923

-

基于FPGA的DDS基本信号发生器的设计2012-07-12 1899

-

基于ARM与DDS的高精度正弦信号发生器设计2016-01-04 1028

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 914

全部0条评论

快来发表一下你的评论吧 !