一文详解Spartan-6系列IO Tile结构

电子说

描述

1. 什么是I/O Tile?

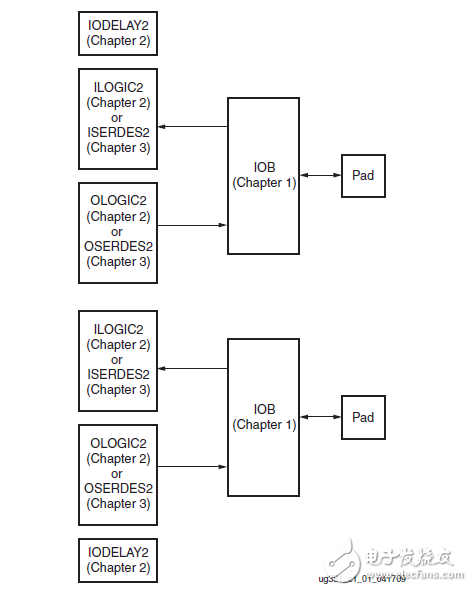

对Spartan-6系列FPGA来说,一个IO Tile包括2个IOB、2个ILOGIC、2个OLOGIC、2个IODELAY。

图 1Spartan-6系列IO Tile结构图

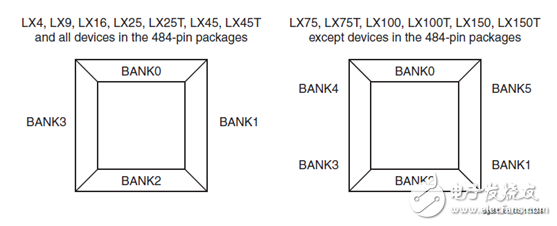

图 2Spartan-6 FPGA I/O Banks

1.1. IOB结构介绍

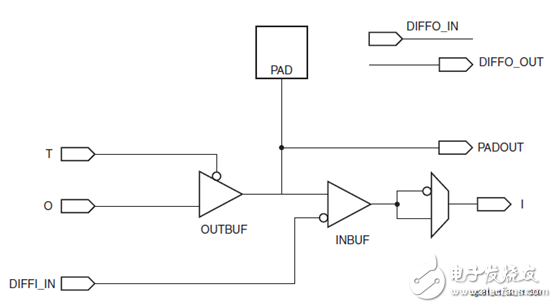

每个IOB包含了输入、输出、三态驱动器;这些驱动器可以配置为不同的电平标准如LVTTL、LVCMOS等;差分IO会用到1个IO Tile里的两个IOB。

每个IOB都被直接连接到了ILOGIC和OLOGIC,ILOGIC和OLOGIC可以被配置成ISERDES或OSERDES,。

图 3基本IOB结构图

1.1.1. IOB内部终端电阻

高速IO电平标准的使用可以优化电平转换特性和信号完整性,在高速IO电平标准中往往需要使用终端电阻。终端电阻的位置应该距离接收器越近越好。

Spartan-6 FPGA为差分IO和单端IO提供了片内终端电阻,这个终端电阻位于IOB内部,使用这些终端电阻,可以避免FPGA外部再引脚处再接电阻。

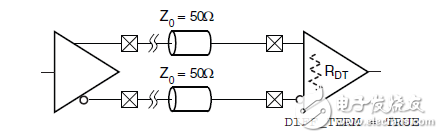

差分IO的终端电阻

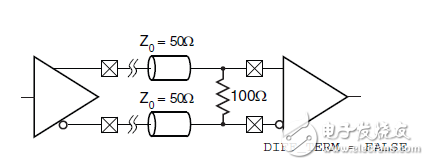

Spartan-6系列为差分IO提供了100Ω的终端电阻,差分引脚的终端电阻可以通过约束文件使之使能或不使能。

图 4差分引脚使能终端电阻

图 5差分引脚不使能终端电阻

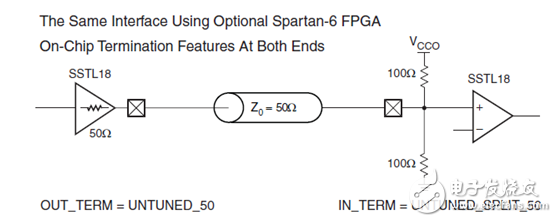

单端引脚终端电阻

单端引脚的输入终端电阻和输出阻抗都是可编程控制的,如下图所示:左边FPGA的输出使能了50Ω的输出阻抗,右边的FPGA使能了输入50%分压电阻;在高速接口应用中,使能输出阻抗可以减少电磁反射,Spartan-6系列FPGA输出阻抗可选值为None、25Ω、50Ω、75Ω;输入阻抗可设置为25%、50%、75%分压。

图 6单向SSTL接口使用片上终端电阻

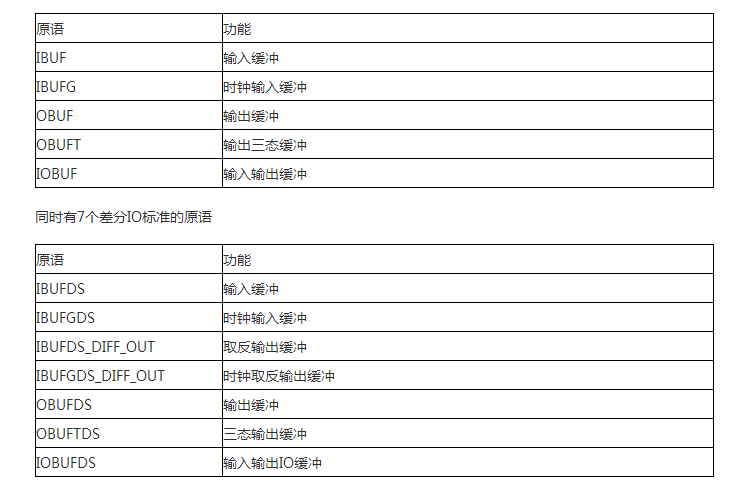

1.1.2. IOB内部可例化的原语

IOB内部有多种输入输出缓冲资源(buffer resource),他们可以原语的形式调用,在Spartan-6系列里,单端IO标准的原语如下5个:

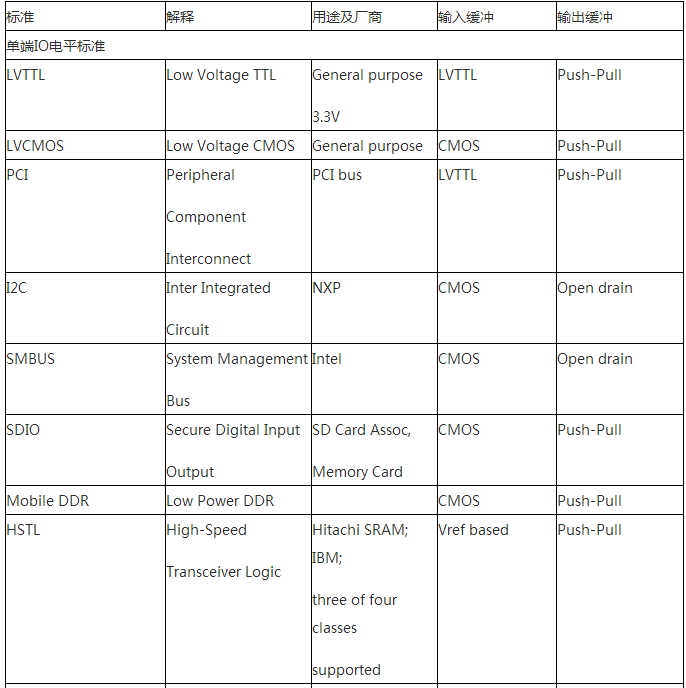

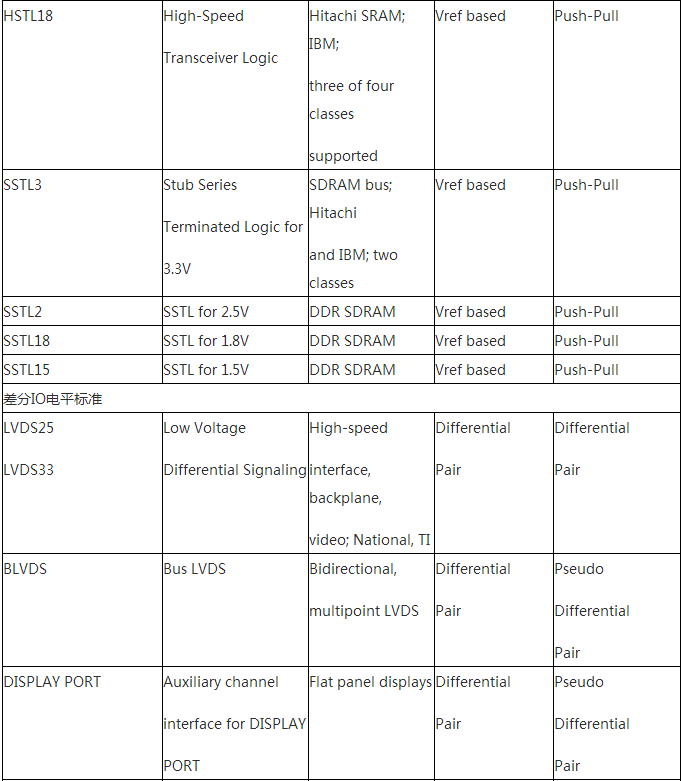

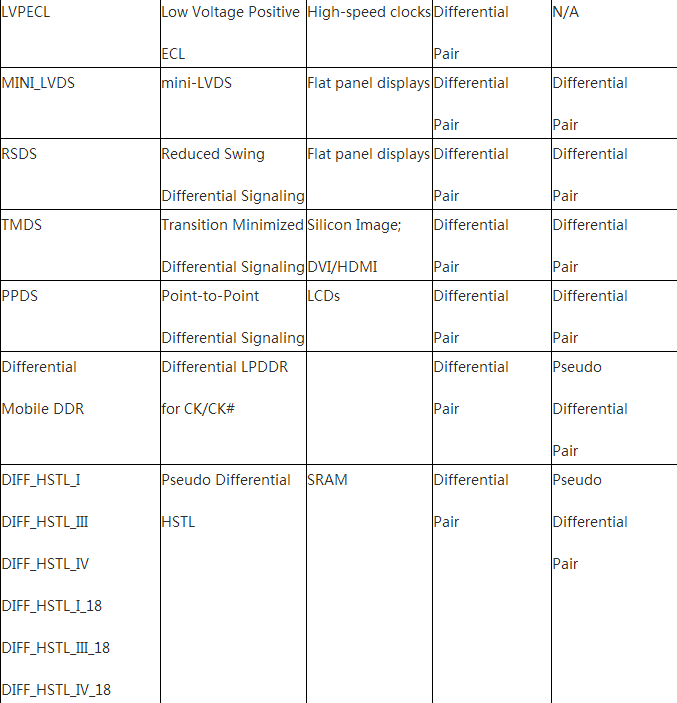

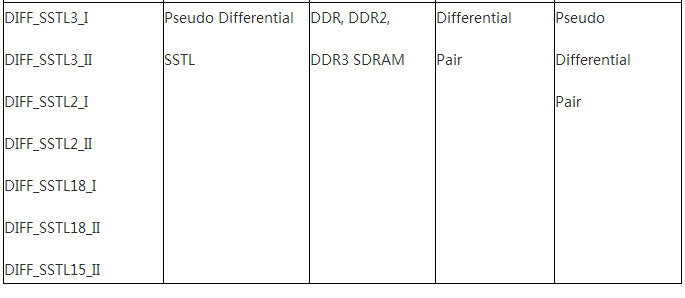

1.1.3. IOB内可用IO电平标准

IOB支持多种电平标准,用户可以自由灵活地为自己的设计选择合适的IO电平标准,Spartan-6系列支持的IO电平标准如下

1.1.4. FPGA配置后未使用引脚状态/strong》

在默认情况下,在FPGA配置完成后,所有未使用的引脚将被配置成输入,并在IOB内部经下拉电阻接地,这种未使用引脚在配置后的状态可以通过UnusedPin BitGen option进行设定。

1.2. SelectIO 的逻辑资源

SelectIO的逻辑资源包括基本资源和高级资源,其中,基本资源包括:

Combinatorial input/output,组合输入/输出

3-state output control,三态输出控制

Registered input/output,寄存器输入输出

Registered 3-state output control,寄存器三态输出控制

Double Data Rate (DDR) input/output,双倍数据率输入输出

DDR output 3-state control,双倍数据率三态输出控制

高级资源包括:

IODELAY2,为用户提供精准的延时控制

NONE, C0, and C1 output DDR mode,输出双倍数据输出

NONE, C0, and C1 input DDR mode,输入双倍数据输入

ISERDES,输入串并转换

OSERDES,输出并串转换

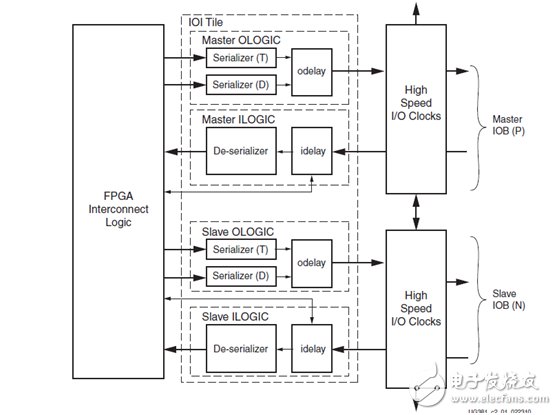

selectIOn逻辑资源被组合在一个IO Tile内部,如下图所示,在单端模式中,master I/O buffer驱动P Pad,slave I/O buffer驱动N Pad;在差分模式中,master I/O buffer和slave I/O buffer组合起来使用,可以完成串并或者并串转换。

图 7一个I/OTile里的selectIO逻辑资源

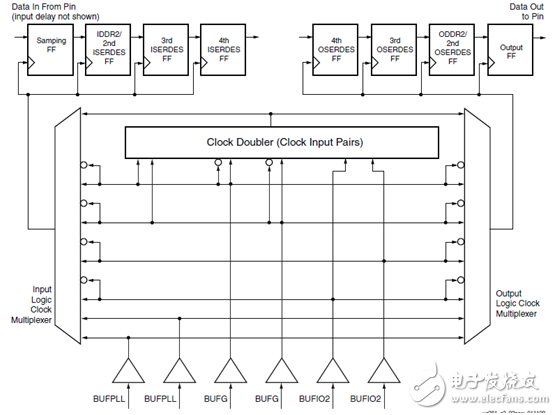

1.3. Selection资源中可用的时钟资源

所有IO的数据采集和转换(包括串并转换和并串转换)、DDR传输等都需要一个内部SDR时钟,为了实现这些功能,I/O接口Tile需要一个本地的时钟倍频器来获取SDR时钟。

进行DDR传输的倍频器需要两个输入时钟,这两个输入时钟必须是下面三种情况之一:

一个全局时钟和它的局部(IO接口资源里)取反时钟

两个相位相差180°的全局时钟

两个相位相差180°的I/O时钟

图 8IO接口逻辑的时钟资源

- 相关推荐

- 热点推荐

- Spartan-6

-

Spartan-6的QDR接口能连接到MCB引脚吗2019-05-22 1453

-

请问IO标准是否与Spartan-6上的SLVS-200兼容?2019-07-12 3840

-

赛灵思宣布Spartan-6 FPGA系列兼容PCI Exp2009-11-05 1295

-

Spartan-6 FPGA工业影像目标设计平台(Xilin2010-03-23 1263

-

基于Spartan-6的FPGA SP601开发设计方案2010-04-02 2848

-

Xilinx Spartan6 IO 电平读书笔记2017-02-08 1564

-

Spartan-6 FPGA的时钟资源及结构介绍2018-07-14 11089

-

Spartan-6 FPGA Configuration User Guide2017-09-19 2097

-

Spartan-6 FPGA电气特性2017-10-24 1616

-

满足 Xilinx Spartan-6 和 Virtex-6 系列的功耗要求2018-06-05 5055

-

Xilinx Spartan-6系列封装概述和管脚分配2018-07-01 10458

-

Spartan-6 FPGA中的DCM功能介绍2018-11-22 6122

-

spartan-6 FPGA的配置资料说明2019-02-15 1536

-

Spartan-6 FPGA的配置教程说明2020-01-10 2186

-

Spartan-6系列FPGA的详细资料概述2020-03-19 3085

全部0条评论

快来发表一下你的评论吧 !