从应用角度详解什么是AXI

电子说

描述

本节介绍的AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

书上讲的AXI比较具体,本节呢不打算落入俗套,从应用角度解释AXI。如果需要深入研究AXI时序,那完全可以从 ?topic=/com.arm.doc.set.amba/ind.。。 下载最权威的规格书,而不是通过别人写的书来获得这些内容(要学习一手材料,不要别人嚼过的)。

Zynq是以ARM作为核心的,运行时也是第一个“醒”过来,然后找可执行代码,找到后进入FSBL(第一引导阶段),接着找配置逻辑部分的bit文件,找到后就叫醒PL按照bit中的方式运行,再接着找可执行代码,进入SSBL(第二引导阶段),这时就可以初始化操作系统的运行环境,引导像Linux这样的大型程序,随后将控制权交给Linux。Linux运行时可以跟PL进行数据交互。注意了,就在这时候,数据交互的通路,就是我们本节要讲的AXI总线。

说白了,AXI就是负责ARM与FPGA之间通信的专用数据通道。

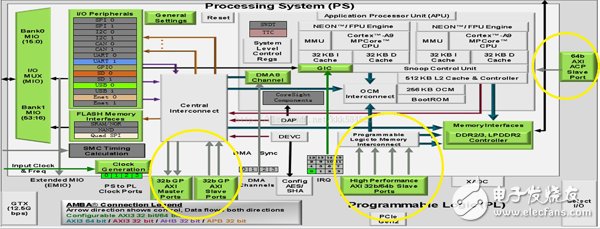

ARM内部用硬件实现了AXI总线协议,包括9个物理接口,分别为AXI-GP0~AXI-GP3,AXI-HP0~AXI-HP3,AXI-ACP接口。如下图黄圈所示。

可以看到,只有两个AXI-GP是Master Port,即主机接口,其余7个口都是Slave Port(从机接口)。主机接口具有发起读写的权限,ARM可以利用两个AXI-GP主机接口主动访问PL逻辑,其实就是把PL映射到某个地址,读写PL寄存器如同在读写自己的存储器。其余从机接口就属于被动接口,接受来自PL的读写,逆来顺受。

这9个AXI接口性能也是不同的。GP接口是32位的低性能接口,理论带宽600MB/s,而HP和ACP接口为64位高性能接口,理论带宽1200MB/s。

有人会问,为什么高性能接口不做成主机接口呢?这样可以由ARM发起高速数据传输。答案是高性能接口根本不需要ARM CPU来负责数据搬移,真正的搬运工是位于PL中的DMA控制器。

位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx提供现成IP如AXI-DMA,AXI-GPIO,AXI-Datamover都实现了相应的接口,使用时直接从XPS的IP列表中添加即可实现相应的功能。

有时,用户需要开发自己定义的IP同PS进行通信,这时可以利用XPS向导生成对应的IP。xps中用户自定义IP核可以拥有AXI-Lite,AXI4,AXI-Stream,PLB和FSL这些接口。

后两种由于ARM这一端不支持,所以不用。

AXI-Lite具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。

AXI4接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。

上面两种均采用内存映射控制方式,即ARM将用户自定义IP编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线。

另外一种AXI接口就是AXI-Stream,这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO根本没有地址的概念),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、音频输出等)构建起连续的数据流。这种接口适合做实时信号处理。

有了上面的这些官方IP和向导生成的自定义IP,用户其实不需要对AXI时序了解太多(除非确实遇到问题),因为Xilinx已经将和AXI时序有关的细节都封装起来,用户只需要关注自己的逻辑实现即可。

- 相关推荐

- 热点推荐

- AXI

-

一文详解AXI DMA技术2025-04-03 2723

-

AXI接口FIFO简介2025-03-17 2361

-

AXI实战(二)-AXI-Lite的Slave实现介绍2023-06-27 8186

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 3260

-

AXI学习路线,从握手协议开始2022-07-29 1622

-

AXI VIP设计示例 AXI接口传输分析2022-07-08 3120

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10954

-

AXI接口协议详解2022-04-08 6025

-

对AXI总线知识详解解析2021-04-09 7541

-

AXI-Stream代码2020-11-05 5011

-

你必须了解的AXI总线详解2020-10-09 9255

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 7573

-

AMBA_AXI总线详解2014-04-18 1829

全部0条评论

快来发表一下你的评论吧 !