利用zedboard添加自定义IP核完成简易计算器功能

电子说

描述

认识zedboard板子也有半个多月了,期间有不少杂事,学的也不是很认真,最近几天在学习如何利用AXI总线进行PS和PL部分的相互通信,利用自定义的IP核实现了简易的计算功能(只有加减),下面对实验的过程和自己的理解进行一下记录。

首先本次试验的目的是做一个建议的计算器,通过zedboard上的sw1,sw2标识操作(01表示加法操作,10表示剪发操作),另外通过led灯进行结果的显示,通过串口进行操作数的输入,而后利用FPGA进行运算,串口输出结果。

实验步骤:

首先在xps中进行工程的建立,导入配置文件(.xml);

而后进行自定义IP核的生成,这部分在下面进行详细记录;

将由xps完成的工程导出,进行ps端应用程序的编写

XPS工程的建立,这部分较为简单,只用简单图示进行记录

首先建立工程,在这里听师兄讲的,我理解为建立工程时用Base System Builder的好处是不需要对基础的一些信息进行配置,这样就能省去很多开发的麻烦,更深层次的就不能体会了。

建立工程后选择Avnet,在Base System Builder界面将右侧不用的外设进行remove掉,而后完成对工程的建立

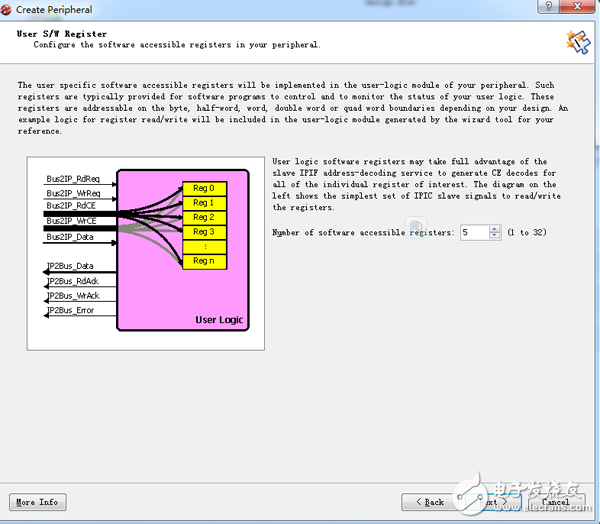

利用Hardware下的Create or import Peripheral建立自定义的IP核(在此我理解为这一步仅为对IP核的一些基础信息的配置,至于IP核具体实现的功能和引出的端口还需要对用户逻辑等信息进行配置),在选择寄存器的个数时,由于本工程中涉及到SW,LED和进行计算时对操作数和结果的存储,因此共需要五个寄存器

在完成此IP的基本配置信息之后,进行用户逻辑和端口号的配置

首先找到工程目录下的pcores\my_calc_v1_v1_00_a\hdl\verilog的user_logic.v文件对用户逻辑进行修改,本工程中设计到的用户逻辑很简单,根据sw前两位的值判断运算方式,而后利用运算数进行运算结果在led灯上进行显示,代码如下,对加入的代码部分进行解释,并加入我的理解

代码:

//----------------------------------------------------------------------------

// user_logic.v - module

//----------------------------------------------------------------------------

//

// ***************************************************************************

// ** Copyright (c) 1995-2012 Xilinx, Inc. All rights reserved. **

// ** **

// ** Xilinx, Inc. **

// ** XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION “AS IS” **

// ** AS A COURTESY TO YOU, SOLELY FOR USE IN DEVELOPING PROGRAMS AND **

// ** SOLUTIONS FOR XILINX DEVICES. BY PROVIDING THIS DESIGN, CODE, **

// ** OR INFORMATION AS ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, **

// ** APPLICATION OR STANDARD, XILINX IS MAKING NO REPRESENTATION **

// ** THAT THIS IMPLEMENTATION IS FREE FROM ANY CLAIMS OF INFRINGEMENT, **

// ** AND YOU ARE RESPONSIBLE FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE **

// ** FOR YOUR IMPLEMENTATION. XILINX EXPRESSLY DISCLAIMS ANY **

// ** WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE **

// ** IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR **

// ** REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF **

// ** INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS **

// ** FOR A PARTICULAR PURPOSE. **

// ** **

// ***************************************************************************

//

//----------------------------------------------------------------------------

// Filename: user_logic.v

// Version: 1.00.a

// Description: User logic module.

// Date: Fri Jul 19 15:24:36 2013 (by Create and Import Peripheral Wizard)

// Verilog Standard: Verilog-2001

//----------------------------------------------------------------------------

// Naming Conventions:

// active low signals: “*_n”

// clock signals: “clk”, “clk_div#”, “clk_#x”

// reset signals: “rst”, “rst_n”

// generics: “C_*”

// user defined types: “*_TYPE”

// state machine next state: “*_ns”

// state machine current state: “*_cs”

// combinatorial signals: “*_com”

// pipelined or register delay signals: “*_d#”

// counter signals: “*cnt*”

// clock enable signals: “*_ce”

// internal version of output port: “*_i”

// device pins: “*_pin”

// ports: “- Names begin with Uppercase”

// processes: “*_PROCESS”

// component instantiations: “I_《#|FUNC》”

//----------------------------------------------------------------------------

`uselib lib=unisims_ver

`uselib lib=proc_common_v3_00_a

module user_logic

(

// -- ADD USER PORTS BELOW THIS LINE ---------------

// --USER ports added here

SW_In, //The operator

LED_Out, //Show some information

// -- ADD USER PORTS ABOVE THIS LINE ---------------

// -- DO NOT EDIT BELOW THIS LINE ------------------

// -- Bus protocol ports, do not add to or delete

Bus2IP_Clk, // Bus to IP clock

Bus2IP_Resetn, // Bus to IP reset

Bus2IP_Data, // Bus to IP data bus

Bus2IP_BE, // Bus to IP byte enables

Bus2IP_RdCE, // Bus to IP read chip enable

Bus2IP_WrCE, // Bus to IP write chip enable

IP2Bus_Data, // IP to Bus data bus

IP2Bus_RdAck, // IP to Bus read transfer acknowledgement

IP2Bus_WrAck, // IP to Bus write transfer acknowledgement

IP2Bus_Error // IP to Bus error response

// -- DO NOT EDIT ABOVE THIS LINE ------------------

); // user_logic

// -- ADD USER PARAMETERS BELOW THIS LINE ------------

// --USER parameters added here

// -- ADD USER PARAMETERS ABOVE THIS LINE ------------

// -- DO NOT EDIT BELOW THIS LINE --------------------

// -- Bus protocol parameters, do not add to or delete

parameter C_NUM_REG = 5;

parameter C_SLV_DWIDTH = 32;

// -- DO NOT EDIT ABOVE THIS LINE --------------------

// -- ADD USER PORTS BELOW THIS LINE -----------------

// --USER ports added here

input [7 : 0] SW_In;

output [7 : 0] LED_Out;

// -- ADD USER PORTS ABOVE THIS LINE -----------------

// -- DO NOT EDIT BELOW THIS LINE --------------------

// -- Bus protocol ports, do not add to or delete

input Bus2IP_Clk;

input Bus2IP_Resetn;

input [C_SLV_DWIDTH-1 : 0] Bus2IP_Data;

input [C_SLV_DWIDTH/8-1 : 0] Bus2IP_BE;

input [C_NUM_REG-1 : 0] Bus2IP_RdCE;

input [C_NUM_REG-1 : 0] Bus2IP_WrCE;

output [C_SLV_DWIDTH-1 : 0] IP2Bus_Data;

output IP2Bus_RdAck;

output IP2Bus_WrAck;

output IP2Bus_Error;

// -- DO NOT EDIT ABOVE THIS LINE --------------------

//----------------------------------------------------------------------------

// Implementation

//----------------------------------------------------------------------------

// --USER nets declarations added here, as needed for user logic \

reg [7 : 0] LED_reg;

// Nets for user logic slave model s/w accessible register example

reg [C_SLV_DWIDTH-1 : 0] slv_reg0;

reg [C_SLV_DWIDTH-1 : 0] slv_reg1;

reg [C_SLV_DWIDTH-1 : 0] slv_reg2;

reg [C_SLV_DWIDTH-1 : 0] slv_reg3;

reg [C_SLV_DWIDTH-1 : 0] slv_reg4;

wire [4 : 0] slv_reg_write_sel;

wire [4 : 0] slv_reg_read_sel;

reg [C_SLV_DWIDTH-1 : 0] slv_ip2bus_data;

wire slv_read_ack;

wire slv_write_ack;

integer byte_index, bit_index;

// USER logic implementation added here

// ------------------------------------------------------

// Example code to read/write user logic slave model s/w accessible registers

//

// Note:

// The example code presented here is to show you one way of reading/writing

// software accessible registers implemented in the user logic slave model.

// Each bit of the Bus2IP_WrCE/Bus2IP_RdCE signals is configured to correspond

// to one software accessible register by the top level template. For example,

// if you have four 32 bit software accessible registers in the user logic,

// you are basically operating on the following memory mapped registers:

//

// Bus2IP_WrCE/Bus2IP_RdCE Memory Mapped Register

// “1000” C_BASEADDR + 0x0

// “0100” C_BASEADDR + 0x4

// “0010” C_BASEADDR + 0x8

// “0001” C_BASEADDR + 0xC

//

// ------------------------------------------------------

assign

slv_reg_write_sel = Bus2IP_WrCE[4:0],

slv_reg_read_sel = Bus2IP_RdCE[4:0],

slv_write_ack = Bus2IP_WrCE[0] || Bus2IP_WrCE[1] || Bus2IP_WrCE[2] || Bus2IP_WrCE[3] || Bus2IP_WrCE[4],

slv_read_ack = Bus2IP_RdCE[0] || Bus2IP_RdCE[1] || Bus2IP_RdCE[2] || Bus2IP_RdCE[3] || Bus2IP_RdCE[4];

// implement slave model register(s)

always @( posedge Bus2IP_Clk )

begin

if ( Bus2IP_Resetn == 1‘b0 )

begin

//slv_reg0 《= 0;

//slv_reg1 《= 0;

slv_reg2 《= 0;

slv_reg3 《= 0;

// slv_reg4 《= 0;

end

else

case ( slv_reg_write_sel )

/* 5’b10000 :

for ( byte_index = 0; byte_index 《= (C_SLV_DWIDTH/8)-1; byte_index = byte_index+1 )

if ( Bus2IP_BE[byte_index] == 1 )

slv_reg0[(byte_index*8) +: 8] 《= Bus2IP_Data[(byte_index*8) +: 8]; */

5‘b01000 :

for ( byte_index = 0; byte_index 《= (C_SLV_DWIDTH/8)-1; byte_index = byte_index+1 )

if ( Bus2IP_BE[byte_index] == 1 )

slv_reg1[(byte_index*8) +: 8] 《= Bus2IP_Data[(byte_index*8) +: 8];

5’b00100 :

for ( byte_index = 0; byte_index 《= (C_SLV_DWIDTH/8)-1; byte_index = byte_index+1 )

if ( Bus2IP_BE[byte_index] == 1 )

slv_reg2[(byte_index*8) +: 8] 《= Bus2IP_Data[(byte_index*8) +: 8];

5‘b00010 :

for ( byte_index = 0; byte_index 《= (C_SLV_DWIDTH/8)-1; byte_index = byte_index+1 )

if ( Bus2IP_BE[byte_index] == 1 )

slv_reg3[(byte_index*8) +: 8] 《= Bus2IP_Data[(byte_index*8) +: 8];

/* 5’b00001 :

for ( byte_index = 0; byte_index 《= (C_SLV_DWIDTH/8)-1; byte_index = byte_index+1 )

if ( Bus2IP_BE[byte_index] == 1 )

slv_reg4[(byte_index*8) +: 8] 《= Bus2IP_Data[(byte_index*8) +: 8]; */

default : begin

slv_reg0 《= slv_reg0;

slv_reg1 《= slv_reg1;

slv_reg2 《= slv_reg2;

slv_reg3 《= slv_reg3;

slv_reg4 《= slv_reg4;

end

endcase

end // SLAVE_REG_WRITE_PROC

// implement slave model register read mux

always @( slv_reg_read_sel or slv_reg0 or slv_reg1 or slv_reg2 or slv_reg3 or slv_reg4 )

begin

case ( slv_reg_read_sel )

5‘b10000 : slv_ip2bus_data 《= slv_reg0;

5’b01000 : slv_ip2bus_data 《= slv_reg1;

5‘b00100 : slv_ip2bus_data 《= slv_reg2;

5’b00010 : slv_ip2bus_data 《= slv_reg3;

5‘b00001 : slv_ip2bus_data 《= slv_reg4;

default : slv_ip2bus_data 《= 0;

endcase

end // SLAVE_REG_READ_PROC

// ------------------------------------------------------------

// Example code to drive IP to Bus signals

// ------------------------------------------------------------

always @(posedge Bus2IP_Clk)

begin

slv_reg0[7 : 0] 《= SW_In[7 : 0];

LED_reg 《= slv_reg1[7 : 0];

end

always @(posedge Bus2IP_Clk)

begin

case(slv_reg0[1 : 0])

2’b01 : slv_reg4 《= slv_reg2 + slv_reg3;

2‘b10 : slv_reg4 《= slv_reg2 - slv_reg3;

default : slv_reg4 《= 0;

endcase

end

assign IP2Bus_Data = (slv_read_ack == 1’b1) ? slv_ip2bus_data : 0 ;

assign IP2Bus_WrAck = slv_write_ack;

assign IP2Bus_RdAck = slv_read_ack;

assign IP2Bus_Error = 0;

assign LED_Out = LED_reg;

endmodule

其中代码slv_reg0~slv_reg4为IP核中申请的5个寄存器,在这里可以根据自己的需要对这个5个寄存器的作用进行分配,在这里完全是按照自己的意愿分配,本程序中,我将slv_reg0用来存储sw的值,slv_reg1用来表示led的信息,slv_reg2和slv_reg3用来进行操作数的存储,slv_reg4用来存储运算结果。

注意,由于在模块中sw为input故他的值不是从总线上进行读取的,slv_reg4存储运算结果,其值也不需要进行存储,故需要对源程序中的一些信息进行注释,即对case下的第一和最后一个选项进行注释,这个地方需要进行自己的判断

另外用户逻辑的加入在代码:

always @(posedge Bus2IP_Clk)

begin

slv_reg0[7 : 0] 《= SW_In[7 : 0];

LED_reg 《= slv_reg1[7 : 0];

end

always @(posedge Bus2IP_Clk)

begin

case(slv_reg0[1 : 0])

2‘b01 : slv_reg4 《= slv_reg2 + slv_reg3;

2’b10 : slv_reg4 《= slv_reg2 - slv_reg3;

default : slv_reg4 《= 0;

endcase

end

可以看出本工程中的逻辑比较简单,就是根据sw的值进行操作数的加减运算。

在完成用户逻辑后,还需要对IP核的端口进行配置,与IPIF相连接(我是这么理解的,可能会不对)

在目录pcores\my_calc_v1_v1_00_a\hdl\vhdl下对文件my_calc_v1.vhd进行更改,代码如下:

------------------------------------------------------------------------------

-- my_calc_v1.vhd - entity/architecture pair

------------------------------------------------------------------------------

-- IMPORTANT:

-- DO NOT MODIFY THIS FILE EXCEPT IN THE DESIGNATED SECTIONS.

--

-- SEARCH FOR --USER TO DETERMINE WHERE CHANGES ARE ALLOWED.

--

-- TYPICALLY, THE ONLY ACCEPTABLE CHANGES INVOLVE ADDING NEW

-- PORTS AND GENERICS THAT GET PASSED THROUGH TO THE INSTANTIATION

-- OF THE USER_LOGIC ENTITY.

------------------------------------------------------------------------------

--

-- ***************************************************************************

-- ** Copyright (c) 1995-2012 Xilinx, Inc. All rights reserved. **

-- ** **

-- ** Xilinx, Inc. **

-- ** XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION “AS IS” **

-- ** AS A COURTESY TO YOU, SOLELY FOR USE IN DEVELOPING PROGRAMS AND **

-- ** SOLUTIONS FOR XILINX DEVICES. BY PROVIDING THIS DESIGN, CODE, **

-- ** OR INFORMATION AS ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, **

-- ** APPLICATION OR STANDARD, XILINX IS MAKING NO REPRESENTATION **

-- ** THAT THIS IMPLEMENTATION IS FREE FROM ANY CLAIMS OF INFRINGEMENT, **

-- ** AND YOU ARE RESPONSIBLE FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE **

-- ** FOR YOUR IMPLEMENTATION. XILINX EXPRESSLY DISCLAIMS ANY **

-- ** WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE **

-- ** IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR **

-- ** REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF **

-- ** INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS **

-- ** FOR A PARTICULAR PURPOSE. **

-- ** **

-- ***************************************************************************

--

------------------------------------------------------------------------------

-- Filename: my_calc_v1.vhd

-- Version: 1.00.a

-- Description: Top level design, instantiates library components and user logic.

-- Date: Fri Jul 19 15:24:36 2013 (by Create and Import Peripheral Wizard)

-- VHDL Standard: VHDL‘93

------------------------------------------------------------------------------

-- Naming Conventions:

-- active low signals: “*_n”

-- clock signals: “clk”, “clk_div#”, “clk_#x”

-- reset signals: “rst”, “rst_n”

-- generics: “C_*”

-- user defined types: “*_TYPE”

-- state machine next state: “*_ns”

-- state machine current state: “*_cs”

-- combinatorial signals: “*_com”

-- pipelined or register delay signals: “*_d#”

-- counter signals: “*cnt*”

-- clock enable signals: “*_ce”

-- internal version of output port: “*_i”

-- device pins: “*_pin”

-- ports: “- Names begin with Uppercase”

-- processes: “*_PROCESS”

-- component instantiations: “I_《#|FUNC》”

------------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

library proc_common_v3_00_a;

use proc_common_v3_00_a.proc_common_pkg.all;

use proc_common_v3_00_a.ipif_pkg.all;

library axi_lite_ipif_v1_01_a;

use axi_lite_ipif_v1_01_a.axi_lite_ipif;

------------------------------------------------------------------------------

-- Entity section

------------------------------------------------------------------------------

-- Definition of Generics:

-- C_S_AXI_DATA_WIDTH -- AXI4LITE slave: Data width

-- C_S_AXI_ADDR_WIDTH -- AXI4LITE slave: Address Width

-- C_S_AXI_MIN_SIZE -- AXI4LITE slave: Min Size

-- C_USE_WSTRB -- AXI4LITE slave: Write Strobe

-- C_DPHASE_TIMEOUT -- AXI4LITE slave: Data Phase Timeout

-- C_BASEADDR -- AXI4LITE slave: base address

-- C_HIGHADDR -- AXI4LITE slave: high address

-- C_FAMILY -- FPGA Family

-- C_NUM_REG -- Number of software accessible registers

-- C_NUM_MEM -- Number of address-ranges

-- C_SLV_AWIDTH -- Slave interface address bus width

-- C_SLV_DWIDTH -- Slave interface data bus width

--

-- Definition of Ports:

-- S_AXI_ACLK -- AXI4LITE slave: Clock

-- S_AXI_ARESETN -- AXI4LITE slave: Reset

-- S_AXI_AWADDR -- AXI4LITE slave: Write address

-- S_AXI_AWVALID -- AXI4LITE slave: Write address valid

-- S_AXI_WDATA -- AXI4LITE slave: Write data

-- S_AXI_WSTRB -- AXI4LITE slave: Write strobe

-- S_AXI_WVALID -- AXI4LITE slave: Write data valid

-- S_AXI_BREADY -- AXI4LITE slave: Response ready

-- S_AXI_ARADDR -- AXI4LITE slave: Read address

-- S_AXI_ARVALID -- AXI4LITE slave: Read address valid

-- S_AXI_RREADY -- AXI4LITE slave: Read data ready

-- S_AXI_ARREADY -- AXI4LITE slave: read addres ready

-- S_AXI_RDATA -- AXI4LITE slave: Read data

-- S_AXI_RRESP -- AXI4LITE slave: Read data response

-- S_AXI_RVALID -- AXI4LITE slave: Read data valid

-- S_AXI_WREADY -- AXI4LITE slave: Write data ready

-- S_AXI_BRESP -- AXI4LITE slave: Response

-- S_AXI_BVALID -- AXI4LITE slave: Resonse valid

-- S_AXI_AWREADY -- AXI4LITE slave: Wrte address ready

------------------------------------------------------------------------------

entity my_calc_v1 is

generic

(

-- ADD USER GENERICS BELOW THIS LINE ---------------

--USER generics added here

-- ADD USER GENERICS ABOVE THIS LINE ---------------

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol parameters, do not add to or delete

C_S_AXI_DATA_WIDTH : integer := 32;

C_S_AXI_ADDR_WIDTH : integer := 32;

C_S_AXI_MIN_SIZE : std_logic_vector := X“000001FF”;

C_USE_WSTRB : integer := 0;

C_DPHASE_TIMEOUT : integer := 8;

C_BASEADDR : std_logic_vector := X“FFFFFFFF”;

C_HIGHADDR : std_logic_vector := X“00000000”;

C_FAMILY : string := “virtex6”;

C_NUM_REG : integer := 1;

C_NUM_MEM : integer := 1;

C_SLV_AWIDTH : integer := 32;

C_SLV_DWIDTH : integer := 32

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

port

(

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

-- ADD USER PORTS ABOVE THIS LINE ------------------

GPIO_LED_Out : out std_logic_vector(7 downto 0);

GPIO_SW_In : in std_logic_vector(7 downto 0);

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol ports, do not add to or delete

S_AXI_ACLK : in std_logic;

S_AXI_ARESETN : in std_logic;

S_AXI_AWADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

S_AXI_AWVALID : in std_logic;

S_AXI_WDATA : in std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

S_AXI_WSTRB : in std_logic_vector((C_S_AXI_DATA_WIDTH/8)-1 downto 0);

S_AXI_WVALID : in std_logic;

S_AXI_BREADY : in std_logic;

S_AXI_ARADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

S_AXI_ARVALID : in std_logic;

S_AXI_RREADY : in std_logic;

S_AXI_ARREADY : out std_logic;

S_AXI_RDATA : out std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

S_AXI_RRESP : out std_logic_vector(1 downto 0);

S_AXI_RVALID : out std_logic;

S_AXI_WREADY : out std_logic;

S_AXI_BRESP : out std_logic_vector(1 downto 0);

S_AXI_BVALID : out std_logic;

S_AXI_AWREADY : out std_logic

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

attribute MAX_FANOUT : string;

attribute SIGIS : string;

attribute MAX_FANOUT of S_AXI_ACLK : signal is “10000”;

attribute MAX_FANOUT of S_AXI_ARESETN : signal is “10000”;

attribute SIGIS of S_AXI_ACLK : signal is “Clk”;

attribute SIGIS of S_AXI_ARESETN : signal is “Rst”;

end entity my_calc_v1;

------------------------------------------------------------------------------

-- Architecture section

------------------------------------------------------------------------------

architecture IMP of my_calc_v1 is

constant USER_SLV_DWIDTH : integer := C_S_AXI_DATA_WIDTH;

constant IPIF_SLV_DWIDTH : integer := C_S_AXI_DATA_WIDTH;

constant ZERO_ADDR_PAD : std_logic_vector(0 to 31) := (others =》 ’0‘);

constant USER_SLV_BASEADDR : std_logic_vector := C_BASEADDR;

constant USER_SLV_HIGHADDR : std_logic_vector := C_HIGHADDR;

constant IPIF_ARD_ADDR_RANGE_ARRAY : SLV64_ARRAY_TYPE :=

(

ZERO_ADDR_PAD & USER_SLV_BASEADDR, -- user logic slave space base address

ZERO_ADDR_PAD & USER_SLV_HIGHADDR -- user logic slave space high address

);

constant USER_SLV_NUM_REG : integer := 5;

constant USER_NUM_REG : integer := USER_SLV_NUM_REG;

constant TOTAL_IPIF_CE : integer := USER_NUM_REG;

constant IPIF_ARD_NUM_CE_ARRAY : INTEGER_ARRAY_TYPE :=

(

0 =》 (USER_SLV_NUM_REG) -- number of ce for user logic slave space

);

------------------------------------------

-- Index for CS/CE

------------------------------------------

constant USER_SLV_CS_INDEX : integer := 0;

constant USER_SLV_CE_INDEX : integer := calc_start_ce_index(IPIF_ARD_NUM_CE_ARRAY, USER_SLV_CS_INDEX);

constant USER_CE_INDEX : integer := USER_SLV_CE_INDEX;

------------------------------------------

-- IP Interconnect (IPIC) signal declarations

------------------------------------------

signal ipif_Bus2IP_Clk : std_logic;

signal ipif_Bus2IP_Resetn : std_logic;

signal ipif_Bus2IP_Addr : std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

signal ipif_Bus2IP_RNW : std_logic;

signal ipif_Bus2IP_BE : std_logic_vector(IPIF_SLV_DWIDTH/8-1 downto 0);

signal ipif_Bus2IP_CS : std_logic_vector((IPIF_ARD_ADDR_RANGE_ARRAY’LENGTH)/2-1 downto 0);

signal ipif_Bus2IP_RdCE : std_logic_vector(calc_num_ce(IPIF_ARD_NUM_CE_ARRAY)-1 downto 0);

signal ipif_Bus2IP_WrCE : std_logic_vector(calc_num_ce(IPIF_ARD_NUM_CE_ARRAY)-1 downto 0);

signal ipif_Bus2IP_Data : std_logic_vector(IPIF_SLV_DWIDTH-1 downto 0);

signal ipif_IP2Bus_WrAck : std_logic;

signal ipif_IP2Bus_RdAck : std_logic;

signal ipif_IP2Bus_Error : std_logic;

signal ipif_IP2Bus_Data : std_logic_vector(IPIF_SLV_DWIDTH-1 downto 0);

signal user_Bus2IP_RdCE : std_logic_vector(USER_NUM_REG-1 downto 0);

signal user_Bus2IP_WrCE : std_logic_vector(USER_NUM_REG-1 downto 0);

signal user_IP2Bus_Data : std_logic_vector(USER_SLV_DWIDTH-1 downto 0);

signal user_IP2Bus_RdAck : std_logic;

signal user_IP2Bus_WrAck : std_logic;

signal user_IP2Bus_Error : std_logic;

------------------------------------------

-- Component declaration for verilog user logic

------------------------------------------

component user_logic is

generic

(

-- ADD USER GENERICS BELOW THIS LINE ---------------

--USER generics added here

-- ADD USER GENERICS ABOVE THIS LINE ---------------

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol parameters, do not add to or delete

C_NUM_REG : integer := 5;

C_SLV_DWIDTH : integer := 32

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

port

(

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

-- ADD USER PORTS ABOVE THIS LINE ------------------

LED_Out :out std_logic_vector(7 downto 0);

SW_In :in std_logic_vector(7 downto 0);

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol ports, do not add to or delete

Bus2IP_Clk : in std_logic;

Bus2IP_Resetn : in std_logic;

Bus2IP_Data : in std_logic_vector(C_SLV_DWIDTH-1 downto 0);

Bus2IP_BE : in std_logic_vector(C_SLV_DWIDTH/8-1 downto 0);

Bus2IP_RdCE : in std_logic_vector(C_NUM_REG-1 downto 0);

Bus2IP_WrCE : in std_logic_vector(C_NUM_REG-1 downto 0);

IP2Bus_Data : out std_logic_vector(C_SLV_DWIDTH-1 downto 0);

IP2Bus_RdAck : out std_logic;

IP2Bus_WrAck : out std_logic;

IP2Bus_Error : out std_logic

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

end component user_logic;

begin

------------------------------------------

-- instantiate axi_lite_ipif

------------------------------------------

AXI_LITE_IPIF_I : entity axi_lite_ipif_v1_01_a.axi_lite_ipif

generic map

(

C_S_AXI_DATA_WIDTH =》 IPIF_SLV_DWIDTH,

C_S_AXI_ADDR_WIDTH =》 C_S_AXI_ADDR_WIDTH,

C_S_AXI_MIN_SIZE =》 C_S_AXI_MIN_SIZE,

C_USE_WSTRB =》 C_USE_WSTRB,

C_DPHASE_TIMEOUT =》 C_DPHASE_TIMEOUT,

C_ARD_ADDR_RANGE_ARRAY =》 IPIF_ARD_ADDR_RANGE_ARRAY,

C_ARD_NUM_CE_ARRAY =》 IPIF_ARD_NUM_CE_ARRAY,

C_FAMILY =》 C_FAMILY

)

port map

(

S_AXI_ACLK =》 S_AXI_ACLK,

S_AXI_ARESETN =》 S_AXI_ARESETN,

S_AXI_AWADDR =》 S_AXI_AWADDR,

S_AXI_AWVALID =》 S_AXI_AWVALID,

S_AXI_WDATA =》 S_AXI_WDATA,

S_AXI_WSTRB =》 S_AXI_WSTRB,

S_AXI_WVALID =》 S_AXI_WVALID,

S_AXI_BREADY =》 S_AXI_BREADY,

S_AXI_ARADDR =》 S_AXI_ARADDR,

S_AXI_ARVALID =》 S_AXI_ARVALID,

S_AXI_RREADY =》 S_AXI_RREADY,

S_AXI_ARREADY =》 S_AXI_ARREADY,

S_AXI_RDATA =》 S_AXI_RDATA,

S_AXI_RRESP =》 S_AXI_RRESP,

S_AXI_RVALID =》 S_AXI_RVALID,

S_AXI_WREADY =》 S_AXI_WREADY,

S_AXI_BRESP =》 S_AXI_BRESP,

S_AXI_BVALID =》 S_AXI_BVALID,

S_AXI_AWREADY =》 S_AXI_AWREADY,

Bus2IP_Clk =》 ipif_Bus2IP_Clk,

Bus2IP_Resetn =》 ipif_Bus2IP_Resetn,

Bus2IP_Addr =》 ipif_Bus2IP_Addr,

Bus2IP_RNW =》 ipif_Bus2IP_RNW,

Bus2IP_BE =》 ipif_Bus2IP_BE,

Bus2IP_CS =》 ipif_Bus2IP_CS,

Bus2IP_RdCE =》 ipif_Bus2IP_RdCE,

Bus2IP_WrCE =》 ipif_Bus2IP_WrCE,

Bus2IP_Data =》 ipif_Bus2IP_Data,

IP2Bus_WrAck =》 ipif_IP2Bus_WrAck,

IP2Bus_RdAck =》 ipif_IP2Bus_RdAck,

IP2Bus_Error =》 ipif_IP2Bus_Error,

IP2Bus_Data =》 ipif_IP2Bus_Data

);

------------------------------------------

-- instantiate User Logic

------------------------------------------

USER_LOGIC_I : component user_logic

generic map

(

-- MAP USER GENERICS BELOW THIS LINE ---------------

--USER generics mapped here

-- MAP USER GENERICS ABOVE THIS LINE ---------------

C_NUM_REG =》 USER_NUM_REG,

C_SLV_DWIDTH =》 USER_SLV_DWIDTH

)

port map

(

-- MAP USER PORTS BELOW THIS LINE ------------------

--USER ports mapped here

LED_Out =》 GPIO_LED_Out,

SW_In =》 GPIO_SW_In,

-- MAP USER PORTS ABOVE THIS LINE ------------------

Bus2IP_Clk =》 ipif_Bus2IP_Clk,

Bus2IP_Resetn =》 ipif_Bus2IP_Resetn,

Bus2IP_Data =》 ipif_Bus2IP_Data,

Bus2IP_BE =》 ipif_Bus2IP_BE,

Bus2IP_RdCE =》 user_Bus2IP_RdCE,

Bus2IP_WrCE =》 user_Bus2IP_WrCE,

IP2Bus_Data =》 user_IP2Bus_Data,

IP2Bus_RdAck =》 user_IP2Bus_RdAck,

IP2Bus_WrAck =》 user_IP2Bus_WrAck,

IP2Bus_Error =》 user_IP2Bus_Error

);

------------------------------------------

-- connect internal signals

------------------------------------------

ipif_IP2Bus_Data 《= user_IP2Bus_Data;

ipif_IP2Bus_WrAck 《= user_IP2Bus_WrAck;

ipif_IP2Bus_RdAck 《= user_IP2Bus_RdAck;

ipif_IP2Bus_Error 《= user_IP2Bus_Error;

user_Bus2IP_RdCE 《= ipif_Bus2IP_RdCE(USER_NUM_REG-1 downto 0);

user_Bus2IP_WrCE 《= ipif_Bus2IP_WrCE(USER_NUM_REG-1 downto 0);

end IMP;

这个里面的一些部分比较难理解,我只是按照我的想法进行解释,不一定正确

我理解的这个文件是对IP核这个实体进行的配置,其中包括的部分分别是,实体的信息,包括实体包含的寄存器,寄存器位宽,实体的对外端口等,其代码为:

entity my_calc_v1 is

generic

(

-- ADD USER GENERICS BELOW THIS LINE ---------------

--USER generics added here

-- ADD USER GENERICS ABOVE THIS LINE ---------------

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol parameters, do not add to or delete

C_S_AXI_DATA_WIDTH : integer := 32;

C_S_AXI_ADDR_WIDTH : integer := 32;

C_S_AXI_MIN_SIZE : std_logic_vector := X“000001FF”;

C_USE_WSTRB : integer := 0;

C_DPHASE_TIMEOUT : integer := 8;

C_BASEADDR : std_logic_vector := X“FFFFFFFF”;

C_HIGHADDR : std_logic_vector := X“00000000”;

C_FAMILY : string := “virtex6”;

C_NUM_REG : integer := 1;

C_NUM_MEM : integer := 1;

C_SLV_AWIDTH : integer := 32;

C_SLV_DWIDTH : integer := 32

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

port

(

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

-- ADD USER PORTS ABOVE THIS LINE ------------------

GPIO_LED_Out : out std_logic_vector(7 downto 0);

GPIO_SW_In : in std_logic_vector(7 downto 0);

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol ports, do not add to or delete

S_AXI_ACLK : in std_logic;

S_AXI_ARESETN : in std_logic;

S_AXI_AWADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

S_AXI_AWVALID : in std_logic;

S_AXI_WDATA : in std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

S_AXI_WSTRB : in std_logic_vector((C_S_AXI_DATA_WIDTH/8)-1 downto 0);

S_AXI_WVALID : in std_logic;

S_AXI_BREADY : in std_logic;

S_AXI_ARADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

S_AXI_ARVALID : in std_logic;

S_AXI_RREADY : in std_logic;

S_AXI_ARREADY : out std_logic;

S_AXI_RDATA : out std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

S_AXI_RRESP : out std_logic_vector(1 downto 0);

S_AXI_RVALID : out std_logic;

S_AXI_WREADY : out std_logic;

S_AXI_BRESP : out std_logic_vector(1 downto 0);

S_AXI_BVALID : out std_logic;

S_AXI_AWREADY : out std_logic

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

在这里需要对实体添加自定义的对外接口,SW和LED

下面就是对IP核的实现进行描述,包括IP核的架构(也是图形界面配置的一部分)包含的用户逻辑和用户逻辑到对外端口的映射关系

component user_logic is

generic

(

-- ADD USER GENERICS BELOW THIS LINE ---------------

--USER generics added here

-- ADD USER GENERICS ABOVE THIS LINE ---------------

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol parameters, do not add to or delete

C_NUM_REG : integer := 5;

C_SLV_DWIDTH : integer := 32

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

port

(

-- ADD USER PORTS BELOW THIS LINE ------------------

--USER ports added here

-- ADD USER PORTS ABOVE THIS LINE ------------------

LED_Out :out std_logic_vector(7 downto 0);

SW_In :in std_logic_vector(7 downto 0);

-- DO NOT EDIT BELOW THIS LINE ---------------------

-- Bus protocol ports, do not add to or delete

Bus2IP_Clk : in std_logic;

Bus2IP_Resetn : in std_logic;

Bus2IP_Data : in std_logic_vector(C_SLV_DWIDTH-1 downto 0);

Bus2IP_BE : in std_logic_vector(C_SLV_DWIDTH/8-1 downto 0);

Bus2IP_RdCE : in std_logic_vector(C_NUM_REG-1 downto 0);

Bus2IP_WrCE : in std_logic_vector(C_NUM_REG-1 downto 0);

IP2Bus_Data : out std_logic_vector(C_SLV_DWIDTH-1 downto 0);

IP2Bus_RdAck : out std_logic;

IP2Bus_WrAck : out std_logic;

IP2Bus_Error : out std_logic

-- DO NOT EDIT ABOVE THIS LINE ---------------------

);

end component user_logic;

这部分用户逻辑的描述,需要再其中加入自己添加的部分,由于在用户逻辑中添加了SW和LED的输入输出,因此在这部分中需要进行添加

最后是用户逻辑中的端口到IP核对外端口的映射,在map中进行了体现,代码如下

USER_LOGIC_I : component user_logic

generic map

(

-- MAP USER GENERICS BELOW THIS LINE ---------------

--USER generics mapped here

-- MAP USER GENERICS ABOVE THIS LINE ---------------

C_NUM_REG =》 USER_NUM_REG,

C_SLV_DWIDTH =》 USER_SLV_DWIDTH

)

port map

(

-- MAP USER PORTS BELOW THIS LINE ------------------

--USER ports mapped here

LED_Out =》 GPIO_LED_Out,

SW_In =》 GPIO_SW_In,

-- MAP USER PORTS ABOVE THIS LINE ------------------

Bus2IP_Clk =》 ipif_Bus2IP_Clk,

Bus2IP_Resetn =》 ipif_Bus2IP_Resetn,

Bus2IP_Data =》 ipif_Bus2IP_Data,

Bus2IP_BE =》 ipif_Bus2IP_BE,

Bus2IP_RdCE =》 user_Bus2IP_RdCE,

Bus2IP_WrCE =》 user_Bus2IP_WrCE,

IP2Bus_Data =》 user_IP2Bus_Data,

IP2Bus_RdAck =》 user_IP2Bus_RdAck,

IP2Bus_WrAck =》 user_IP2Bus_WrAck,

IP2Bus_Error =》 user_IP2Bus_Error

);

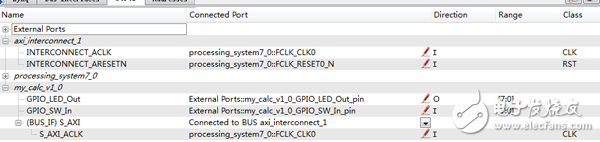

在完成以上代码的书写后,就基本完成了IP的控制,下面就是将IP核添加到工程中去,在此双击用户的IP核即可添加,在添加完成后,会在Bus Interface中发现此IP核,而后在port中进行配置,在port的配置过程中我理解为,此部分为经过IPIF包装后IP核的对外端口,通过这些对外端口可以进行一些外设的连接,而后此IP核映射到PS端,当作一个外设进行同意编址,PS端可以直接对地址进行操作,就可以控制外设(如sw和led)

将GPIO_LED_Out和GPIO_SW_In配置为External Ports,这样我理解是利用External Ports就可以对外设进行连接,外设看到的端口名称为my_calc_v1_0_GPIO_LED_Out_pin,和my_calc_v1_0_GPIO_SW_In_pin。

进行完端口的配置后,就可以进行约束文件的建立,将端口映射到FPGA的具体引脚上,约束文件如下:

#

# pin constraints

#

#

NET “my_calc_v1_0_GPIO_LED_Out_pin[0]” LOC = T22;

NET “my_calc_v1_0_GPIO_LED_Out_pin[1]” LOC = T21;

NET “my_calc_v1_0_GPIO_LED_Out_pin[2]” LOC = U22;

NET “my_calc_v1_0_GPIO_LED_Out_pin[3]” LOC = U21;

NET “my_calc_v1_0_GPIO_LED_Out_pin[4]” LOC = V22;

NET “my_calc_v1_0_GPIO_LED_Out_pin[5]” LOC = W22;

NET “my_calc_v1_0_GPIO_LED_Out_pin[6]” LOC = U19;

NET “my_calc_v1_0_GPIO_LED_Out_pin[7]” LOC = U14;

NET “my_calc_v1_0_GPIO_LED_Out_pin[0]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[1]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[2]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[3]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[4]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[5]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[6]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_LED_Out_pin[7]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[0]” LOC = F22;

NET “my_calc_v1_0_GPIO_SW_In_pin[1]” LOC = G22;

NET “my_calc_v1_0_GPIO_SW_In_pin[2]” LOC = H22;

NET “my_calc_v1_0_GPIO_SW_In_pin[3]” LOC = F21;

NET “my_calc_v1_0_GPIO_SW_In_pin[4]” LOC = H19;

NET “my_calc_v1_0_GPIO_SW_In_pin[5]” LOC = H18;

NET “my_calc_v1_0_GPIO_SW_In_pin[6]” LOC = H17;

NET “my_calc_v1_0_GPIO_SW_In_pin[7]” LOC = M15;

NET “my_calc_v1_0_GPIO_SW_In_pin[0]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[1]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[2]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[3]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[4]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[5]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[6]” IOSTANDARD = LVCMOS33;

NET “my_calc_v1_0_GPIO_SW_In_pin[7]” IOSTANDARD = LVCMOS33;

# additional constraints

#

完成后,XPS端的配置就完成,点击Generate BitStream生成bit文件,成功后导出的SDK

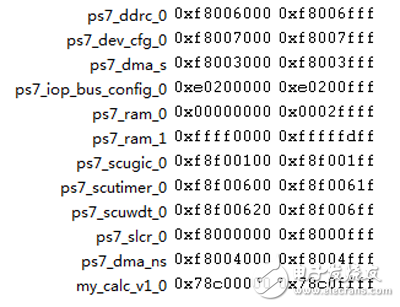

在进入SDK后,我们可以在system.xml文件中可以看到建立的IP核搭建的PL部分被当作外设映射到PS端,映射地址为0x78c00000

在此后我们只需要根据C语言的知识,对此地址端进行编程即可,下面逻辑就不再展开叙述,具体代码如下,写的比较乱

/*

* Copyright (c) 2009 Xilinx, Inc. All rights reserved.

*

* Xilinx, Inc.

* XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION “AS IS” AS A

* COURTESY TO YOU. BY PROVIDING THIS DESIGN, CODE, OR INFORMATION AS

* ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, APPLICATION OR

* STANDARD, XILINX IS MAKING NO REPRESENTATION THAT THIS IMPLEMENTATION

* IS FREE FROM ANY CLAIMS OF INFRINGEMENT, AND YOU ARE RESPONSIBLE

* FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE FOR YOUR IMPLEMENTATION.

* XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO

* THE ADEQUACY OF THE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO

* ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE

* FROM CLAIMS OF INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY

* AND FITNESS FOR A PARTICULAR PURPOSE.

*

*/

/*

* helloworld.c: simple test application

*/

#include

#include “platform.h”

#define SW (* (volatile unsigned int *) 0x78C00000) //

#define LED (* (volatile unsigned int *) 0x78C00004) //

#define ADD1 (* (volatile unsigned int *) 0x78C00008) // 第一个寄存器地址---加数一

#define ADD2 (* (volatile unsigned int *) 0x78C0000C) // 第二个寄存器地址---加数二

#define SUM (* (volatile unsigned int *) 0x78C00010) // 第三个寄存器地址---和

//void print(char *str);

int main()

{

init_platform();

printf(“Hello World\n\r”);

printf(“Please input the first operator:\n\r”);

scanf(“%d”, &ADD1);

printf(“Please second the first operator:\n\r”);

scanf(“%d”, &ADD2);

if(SW == 0x01)

{

printf(“The result of ADD1 + ADD2 = %d\n\r”, SUM);

}

else if(SW == 0x02)

{

printf(“The result of ADD1 - ADD2 = %d\n\r”, SUM);

}

LED = SUM;

-

使用Python/MyHDL创建自定义FPGA IP2026-04-09 217

-

添加自定义属性控制fridaserver启动和停止2023-08-09 3072

-

教程 2:添加特征-自定义配置文件创建2023-03-15 764

-

自定义视图组件教程案例2022-04-08 997

-

自定义进度指示器progressbutton2022-03-24 828

-

玩转Zynq连载25——[ex04] 基于Zynq PL的自定义IP核集成2019-09-20 3305

-

玩转Zynq连载24——用户自定义IP核的移植2019-09-15 2835

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4790

-

xilinx vivado 怎么封装包含一个ip核的自定义ip?2018-12-11 7526

-

EDK中PS2自定义IP2016-06-07 1052

-

添加自定义IP核基本步骤2015-11-30 615

-

c51简易计算器2015-11-12 1456

-

nios 自定义ip问题求助2013-11-26 3427

-

基于Avalon总线SHT11温湿度传感器自定义IP核的开发流程2013-01-28 14440

全部0条评论

快来发表一下你的评论吧 !