一个FPGA中现在可集成多少32位RISC处理器?

FPGA/ASIC技术

211人已加入

描述

Jan Gray是在FPGA中集成32位RISC处理器的专家,他写了一篇博客叫作FPGA CPU 新闻,副标题为 “使用FPGA开发并行计算机体系架构”。 Jan Gray的最新帖子为FPGAs, 当时和现在,这篇帖子将1995年 在Xilinx XC4010PC84-5 FPGA中集成J32 32-bit RISC CPU与目前Xilinx Virtex-7 XC7VX690T FPGA 集成同一处理器进行了对比。Gray 使用的J32处理器采用经典RISC架构,带有3-operand操作指令,4=stage流水线(提取、寄存器读、执行、回写),和32位操作数寄存器文件。

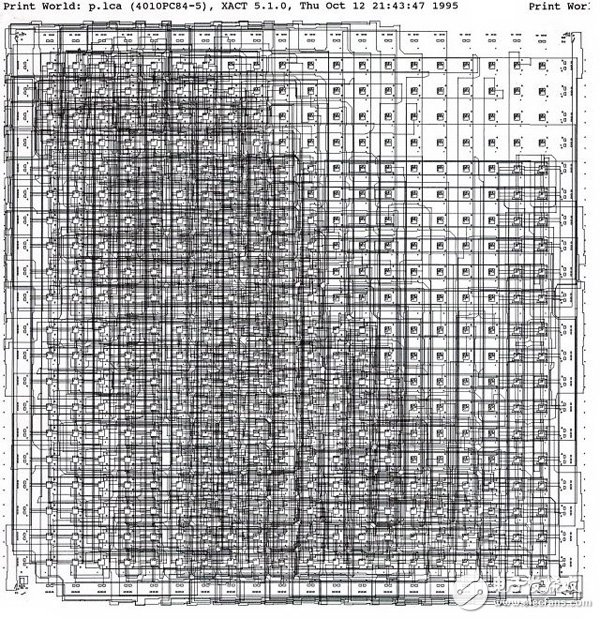

1995年,Gray使用的J32处理器基本消耗了XC4010 FPGA中800个4-input LUT。处理器排列看起来是这样:

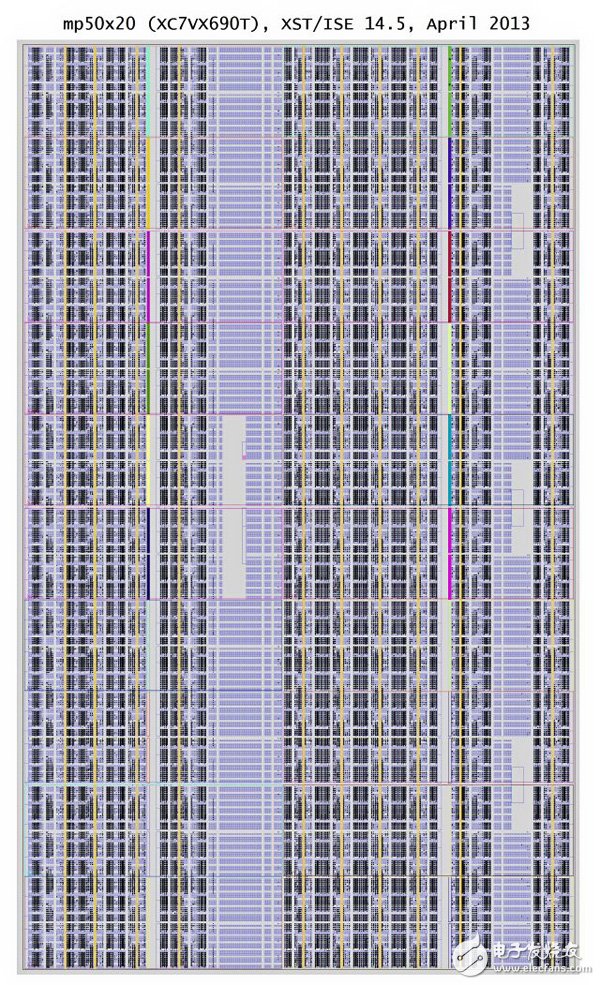

13年以后。同一J32处理器内核集成在Virtex - 7 FPGA,它支持433,000以上的6输入 LUT,是250个路由器核心与1000个处理器互连预留空间的1000倍。J32 RISC处理器的排列看起来像这样:

“也就是说过去18年摩尔定律将每个FPGA集成1K LUT升级至每个FPGA集成1K 32-bit CPU。(顺便说下,规模最大的Virtex Ultrascale 3D FPGA有440万个逻辑单元,所以逻辑容量足够10,000个以上Jan Gray所提到的 32位RISC J32 CPU进行互连。且看以下的注释说明!)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HPM5E31IGN单核 32 位 RISC-V 处理器2025-05-29 3244

-

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景2024-08-31 2096

-

Achronix FPGA增加对Bluespec提供的基于Linux的RISC-V软处理器的支持,以实现可扩展数据处理2024-04-19 1368

-

fpga和risc-v处理器的区别2024-03-27 2859

-

从零开始写RISC-V处理器之一 二 前言 绪论2022-08-22 5164

-

ARM处理器设计RISC介绍(上)2022-04-24 2878

-

RISC-V开源处理器核介绍2021-07-23 2414

-

FPGA技术如何用VHDL语言实现8位RISC微处理器?2021-04-13 1830

-

RISC-V是通用RISC处理器还是可定制的处理器?2020-11-17 4520

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4366

-

ARM处理器简介及RISC设计要点2018-04-01 10416

-

Cyclone V SoC FPGA硬核处理器系统简介2012-09-04 5741

-

嵌入式32位RISC处理器扩展了FPGA的DSP功能2011-02-25 940

-

一个针对FPGA的完全可配置嵌入式32位RISC处理器2009-11-03 1034

全部0条评论

快来发表一下你的评论吧 !