开启400G以太网:Spirent 400G以太网测试系统

FPGA/ASIC技术

描述

在法国尼斯举行的2014WDM和下一代光纤网络研讨会上,思博伦通信 和 赛灵思公司讨论了通过Spirent 400G以太网测试系统对华为NE5000E以太网核心路由成功测试的完成情况,这在一个月前在芝加哥举行的LightReading电信大事件中发表的(见“Huawei’s 400GE router successfully completes testing on Spirent’s new 400GE test platform—both enabled by the Virtex-7 H870T 3D FPGA.”)。然而,这周的WDM报告会更深入地探究Spirent 400G以太网测试系统的实现细节,包括使用Xilinx Virtex-7 H870T 3D FPGA的细节。Xilinx Virtex-7 H870T 3D FPGA在华为和思博伦的设计中均被使用。

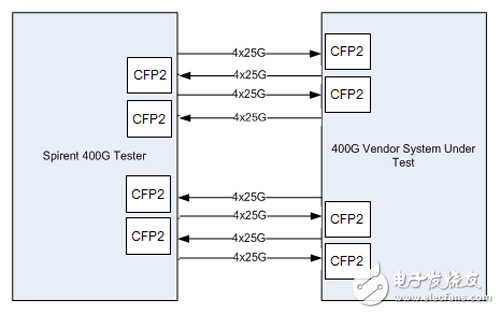

这个是测试结构图:

测试结构图

测试涉及到以400G线全工速率传输和接收的以太网通信。验证零错误操作和收集多种网络通信情况下的统计信息,以提供先前IEEE 400GE规范的初步验证。

可变大小数据包

速率调整

延迟和订购数据包测试

验证每个接收到的数据包

错误检查

数据包抓取

合规性测试

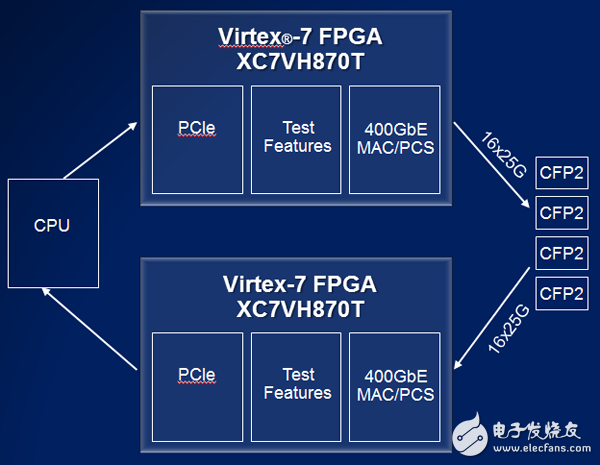

在任何系统上运行400G以太网数据包都不是件小事。它需要用于实现以太网硬件的设备内外拥有大量I/O带宽,也需要设备内有大量数据流和路由。思博伦公司实现了在一个Xilinx H870T 3D FPGA上运行四个CFP2光模块,这意味着400G以太网测试系统有两部分——一部分传输数据包,一部分接收数据包。数据通过使用160字节宽的312MHz总线在芯片上路由。这是其中一块Spirent 400G以太网测试系统板的图片和高级设计方块图。

Spirent 400G以太网测试系统板

Spirent 400G以太网测试系统方块图

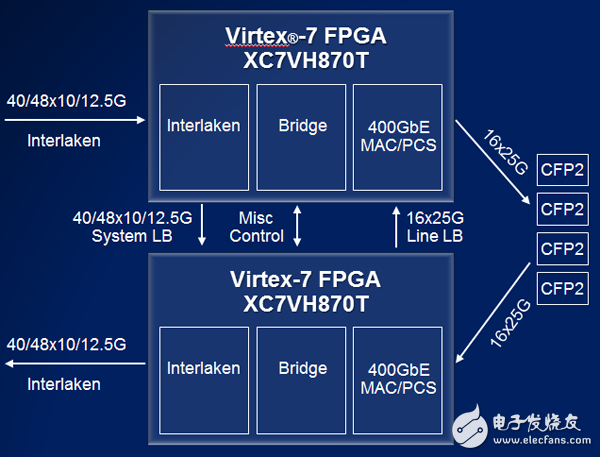

华为400G以太网线卡的方块图也把功能分为一块传输FPGA和 一块接收FPGA,以及一些额外的线卡传输器和接收器之间的通信。

华为400G以太网线卡方块图

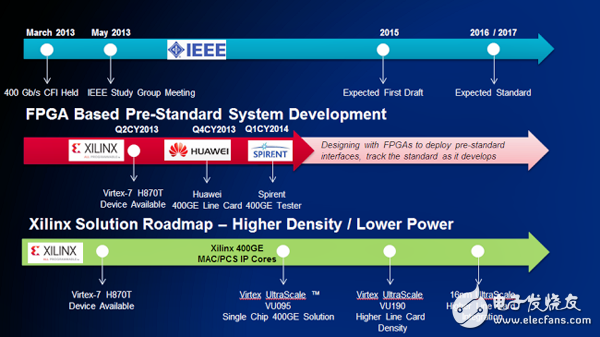

注意到,在获得IEEE 400G以太网标准许可前两年使用Xilinx FPGA实现这些系统,可以显著降低项目成本和设计风险。这些设计可以快速升级和修改以适应400G以太网标准。不需要修改实际硬件——FPGA配置的改变就是所有需要的了,并且这可以通过现有板子的剩余部分实现。这个灵活性相当有帮助,当标准不确定时,就像是这里这种情况。

讨论中的一个新元素在WDM揭露,就是目前基于Virtex-7 H870T 3D FPGA开发IEEE 400G以太网规范的发展路线和先前标准的400G以太网设计的迁移。发展路线指出了未来设计中对Xilinx Virtex UltraScale FPGA的预期使用,为的是降低功耗和提高线卡端口密度,如下所示:

400G以太网发展路线

升级过渡是可行的,因为大量的高速GTY收发器用于Virtex UltraScale器件,由UltraScale架构而改良的片上可路由性和UltraScale器件中集成的Interlaken IP。

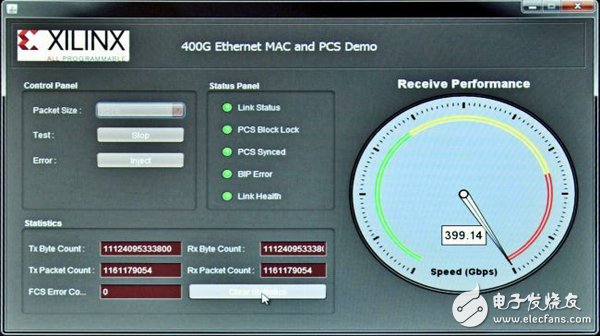

那么我们离这升级过渡还有多远?我非常高兴你能提出这样的问题。今天在WDM2014,赛灵思公司证明了400G以太网可以成功地在UltraScale器件上运行。这是一张演示图片:

WDM2014 UltraScale 400G以太网演示

这里是所有重要统计信息的屏幕:

UltraScale 400G以太网演示统计信息

主要统计信息——上十亿计的字节传输和接收,并且零错误。

早前Xcell Daily关于这些主题的报道,见:

Huawei and Xilinx unveil prototype 400GE Core Router at OFC 2104. FPGAs do the heavy lifting

Huawei and Xilinx discuss 400G Ethernet for future router products at OFC 2014—the Video

-

400G 网络如何测试2024-12-12 6434

-

400G市场现状和前景2020-10-23 2526

-

Xilinx UltraScale 20nm器件助力打造JDSU ONT 400G以太网测试平台2015-04-09 1134

-

JDSU 400G 以太网测试平台基于Xilinx 20nm UltraScale 器件2017-02-09 472

-

不可错过的400Gbps以太网演示2017-02-10 2097

-

100G和400G以太网及数据通信技术2017-09-01 1599

-

世界网络节奏加快!200G/400G以太网近在眼前2018-01-09 1834

-

华为携手赛灵思 展示400G以太网线卡原型2018-11-28 1491

-

赛灵思公司宣布其Virtex UltraScale 20nm FPGA已应用G以太网测试平台2019-07-31 2833

-

400G以太网标准引领连接器发展2019-10-09 3188

-

基于SRv6性能的大规模400G测试完成,为网络基础架构奠定可靠基础2020-05-08 4657

-

下一站数据中心的主流:200G/400G光模块2023-05-09 1756

-

大型以太网世界:10M至400G2023-05-26 2999

-

400G以太网光模块发展及联讯测试方案2023-07-21 2919

-

400G Optical Transceiver 全面解析:Cisco 400G 光模块与应用指南2025-09-15 1606

全部0条评论

快来发表一下你的评论吧 !