ZedBoard学习手记(二) 开发自定义AXI总线外设IP核

FPGA/ASIC技术

211人已加入

描述

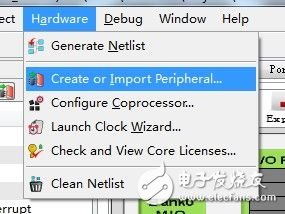

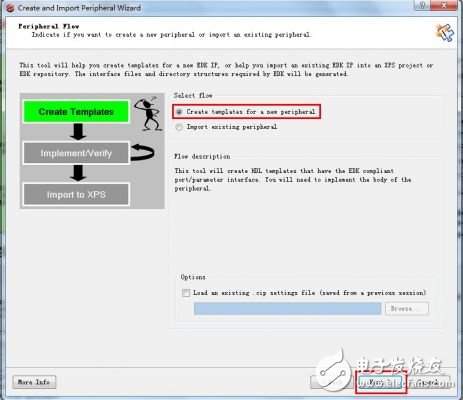

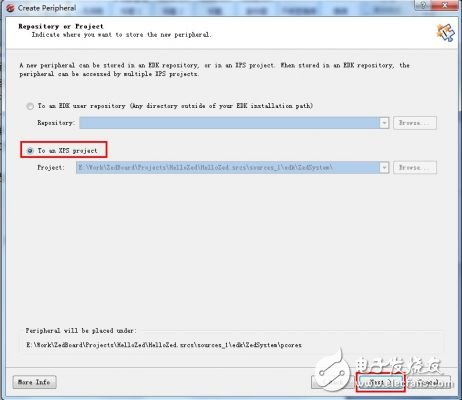

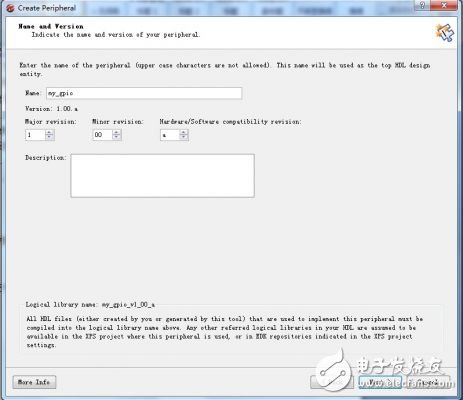

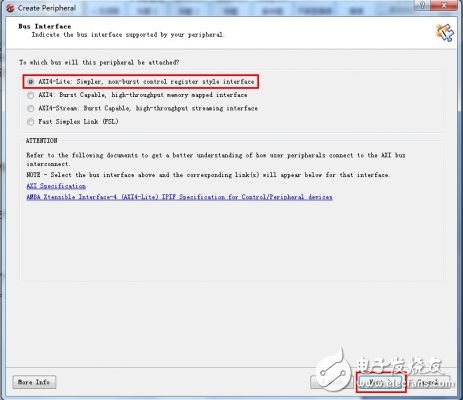

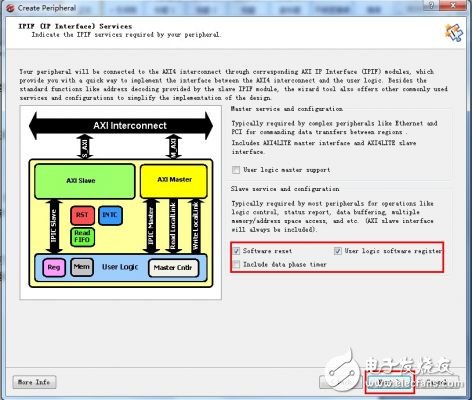

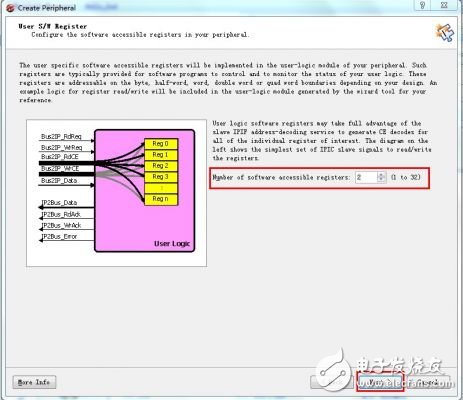

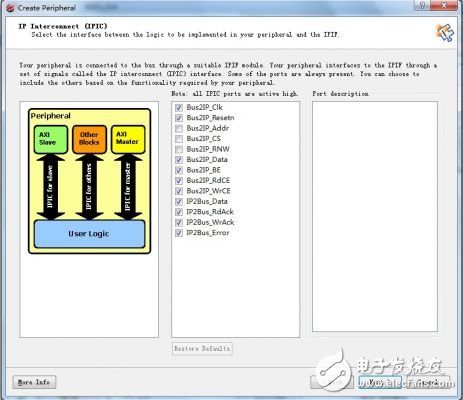

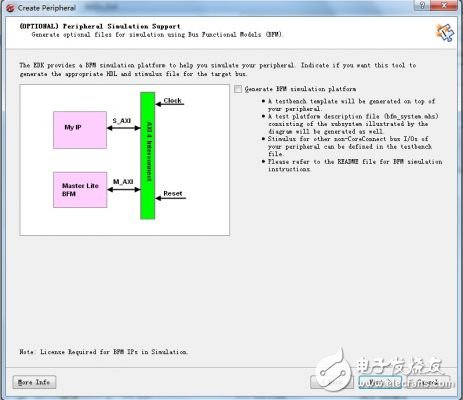

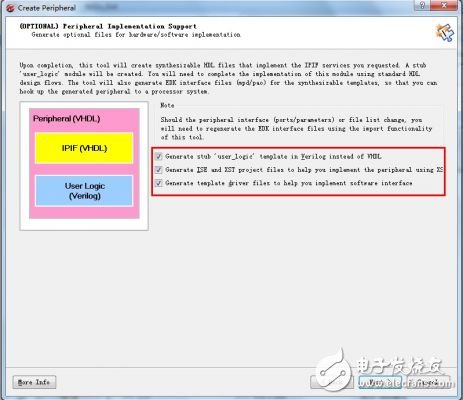

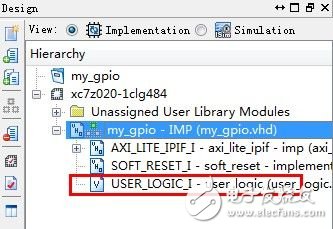

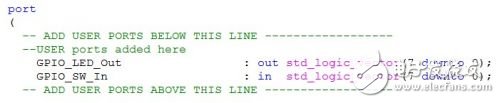

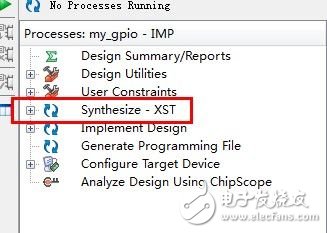

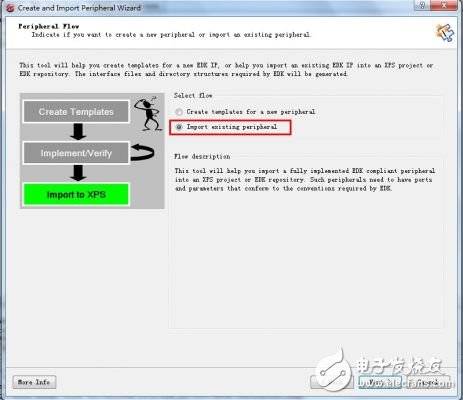

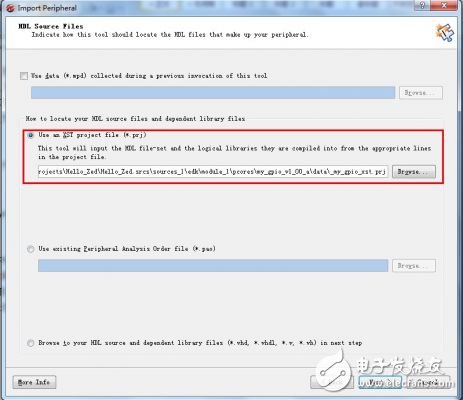

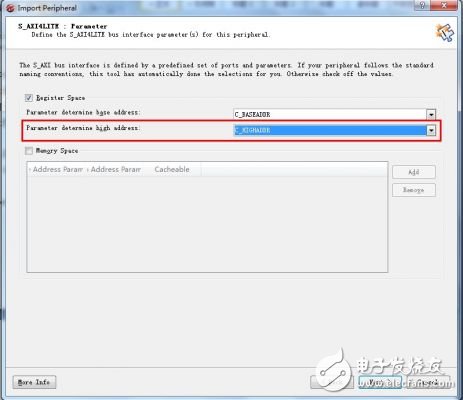

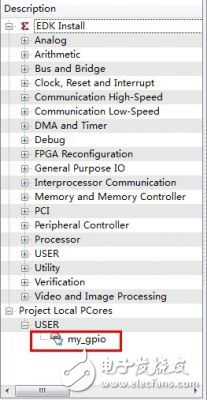

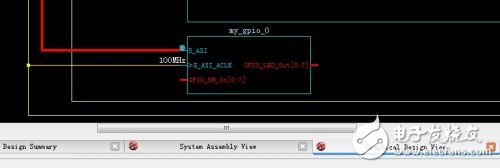

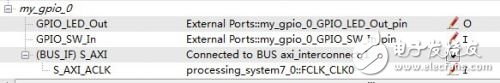

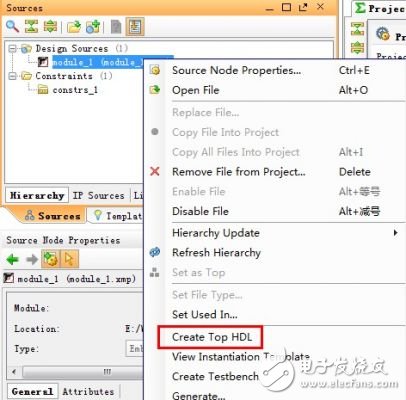

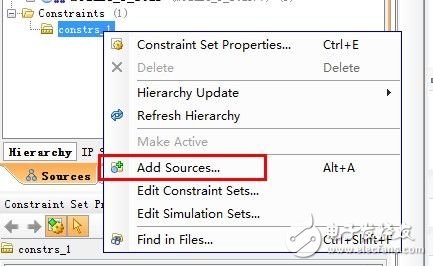

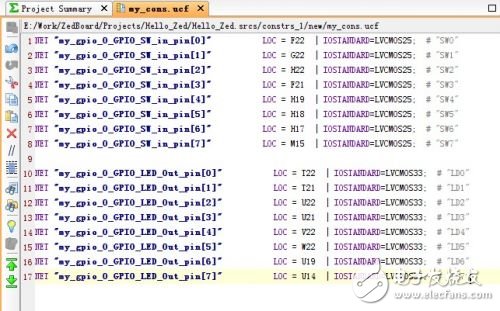

想要发挥ZYNQ芯片的特长,让整个系统协同工作起来,就需要将PS与PL两部分结合在一起,在Cortex-A9核和FPGA逻辑资源之间建立通信的通道,这条通道就是AXI总线。ZedBoard推出的官方例子中已经介绍了如何将Xilinx做好的AXI总线IP(如AXI_Timer、AXI_GPIO等)添加到工程中,而下面就让我们一起来自己编写一个简单的AXI总线设备——读取板上的8个Swtich状态,并控制8个LED的开关。有人会问我不了解AXI总线啊怎么办,无须担心,Xilinx已经为我们设计了建立向导,可以自动生成一个设备模板,即使不了解AXI协议,也可以轻松完成设计工作。首先通过PlanAhead建立一个系统工程,导入ZedBoard的xml文件:zedboard_RevC_v2.xml。这步操作还不清楚的童鞋请在ZedBoard官网上下载ZedBoard_CTT_v14.1资料并跟随该文档进行扫盲。这个资料很详细,也是Step By Step的,可以帮助完成基本的操作学习。工程建好后,进入XPS界面,选择Hardware→Create or Import Peripheral,开始创建外设。(看不清图的话可以点击小图放大,下同)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用AXI4接口IP核进行DDR读写测试2025-11-24 3917

-

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建2020-12-21 4800

-

nios 自定义ip问题求助2013-11-26 3426

-

【Z-turn Board试用体验】+ 【第六贴】:为ZYNQ的SOC添加自定义IP实现嵌入式系统2015-06-11 6507

-

ZYNQ & AXI总线 & PS与PL内部通信(用户自定义IP)2018-01-08 14610

-

ZYNQ自定义AXI总线IP应用 ——PWM实现呼吸灯效果2020-04-23 2734

-

如何使用BMLang开发自定义的算子?2023-09-18 1067

-

SOPC中自定义外设和自定义指令性能分析2009-03-29 1916

-

基于Avalon总线SHT11温湿度传感器自定义IP核的开发流程2013-01-28 14425

-

利用zedboard添加自定义IP核完成简易计算器功能2018-07-12 3119

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 17991

-

怎么样去开发自定义应用程序?2018-07-11 2887

-

如何使用Vivado功能创建AXI外设2018-11-29 7900

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4788

-

自定义AXI-Lite接口的IP及源码分析2023-06-25 5166

全部0条评论

快来发表一下你的评论吧 !