Xilinx可编程逻辑器件设计与开发(基础篇)连载6:Spartan

FPGA/ASIC技术

211人已加入

描述

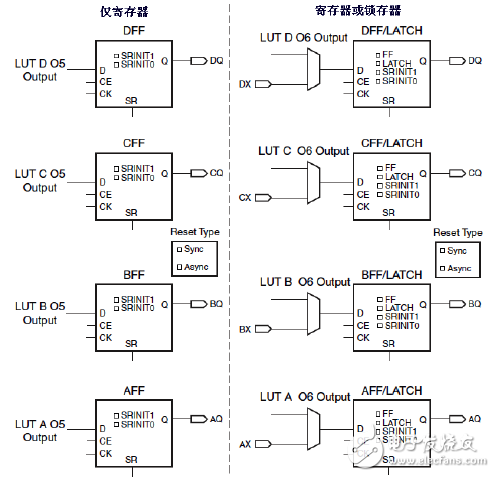

Spartan-6的每个SLICE 有8个存储元件,可以实现存储功能。其中4个与O6相连的存储单元可以配置成寄存器或锁存器,而与O5相连的存储单元仅可以配置成寄存器,如图2-4 所示。这是与Spartan-3系列器件不同之处。

图2-4 SLICE里寄存器/锁存器配置

三、 多路复用器(MUX)

多路复用器F7AMUX、F7BMUX 和F8MUX通常和函数发生器或者片上逻辑一起实现多种多路复用器。在Spartan-6 中,LUT可以实现如下多路复用器。

一个LUT实现4:1多路复用器。

2个LUT实现8:1多路复用器。

4个LUT实现16:1多路复用器。

MUX有两个原语,MUXF7和MUXF8。

四、 快速先行进位逻辑(Carry Logic)

除了函数发生器,SLICEM和SLICEL(非SLICEX)包含专门的进位链,用于在SLICE中实现快速算术加减运算。CLB中有一条进位链,能解决多位宽加法、乘法从最低位向最高位的进位延时问题。先行进位逻辑有专用的进位通路和进位多路复用器(MUXCY),可用来级联函数发生器(LUT),以实现更宽更复杂的逻辑函数,提高CLB的算术运算速度。Spartan-6中的进位链是上行进位链,每个SLICE具有4位的高度。考虑到进位链的上行结构特点,在设计中,要特别注意进位链的长度,因为如果当进位链长度超出一列时,进位会导致延时变长很多,影响时序。

快速先行进位逻辑有一个原语,即CARRY4。

五、 算术逻辑(MULT_AND)

算术逻辑包括一个异或门(XOR)和一个专用与门(MULT_AND)。一个异或门可以使一个SLICE实现2位全加操作,专用与门可提高乘法器的效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 17693

-

可编程逻辑器件2014-04-15 3678

-

可编程逻辑器件是如何发展的?2021-04-29 1871

-

PLD可编程逻辑器件2021-07-22 2324

-

可编程逻辑器件设计2006-03-25 1179

-

可编程逻辑器件基础及应用实验指导书2010-03-24 786

-

什么是PLD(可编程逻辑器件)2009-06-20 30053

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1163

-

Xilinx可编程逻辑器件的高级应用与设计技巧(孙航)2012-11-28 1631

-

可编程逻辑器件学习(共10篇文档)2016-09-02 1291

-

可编程逻辑器件(书皮)2022-07-10 790

-

可编程逻辑器件原理、开发与应用2017-09-19 928

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2250

-

可编程逻辑器件的结构2023-03-24 2136

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4577

全部0条评论

快来发表一下你的评论吧 !