Xilinx可编程逻辑器件设计与开发(基础篇)连载7:Spartan

FPGA/ASIC技术

211人已加入

描述

时钟布线资源具有高速、低SKEW的特点,它对系统设计非常重要,即使系统速率不高,也应该关注时钟设计,以消除潜在的时钟危险。Spartan-6器件包含16个全局时钟资源和40个I/O区域时钟资源。全局时钟用于系统时钟,而I/O区域时钟专用于I/O串行/解串(ISERDES和OSERDES)设计。

Spartan-6时钟资源包含以下4种。

全局时钟输入引脚(GCLK)。

局时钟多路复用器。

I/O时钟缓冲器。

时钟布线网络。

包括由BUFGMUX驱动的全局时钟网络和由I/O时钟缓冲器(BUFIO2)、PLL时钟缓冲器(BUFPLL)驱动的I/O区域时钟网络。

一、 时钟输入

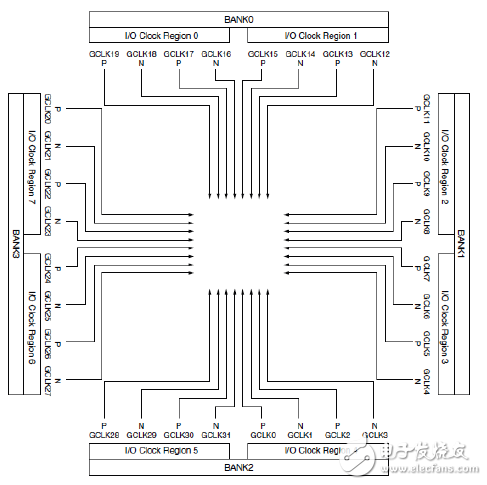

每个Spartan-6有32个全局时钟输入引脚,分布在FPGA的四周。时钟输入引脚在片上的分布图如图2-5所示。时钟输入引脚接收外部时钟信号,直接连接片内的DCM/PLL/BUFGMUX/BUFIO2。时钟输入引脚不连接时钟时,用作普通I/O。

一个差分时钟输入需要两个全局时钟输入。成对的时钟输入在标号上是连续的,例如,GCLK0和GCLK1是差分对,GCLK20和GCLK21是差分对。每个全局时钟缓冲器有两个时钟输入,Spartan-6支持最多16对的差分全局时钟输入。

设计中的时钟输入引脚连接IBUFG原语,通常综合工具会分析设计,自动将顶层时钟引脚推演为与IBUFG相连。如果需要更多IBUFG的控制功能,可以通过例化IBUFG的方式,将IBUFG的I端口连到顶层端口,将O端口连接到DCM、BUFG或通用逻辑。

图2-5 时钟输入引脚片上分布图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 17693

-

可编程逻辑器件2014-04-15 3678

-

可编程逻辑器件是如何发展的?2021-04-29 1871

-

PLD可编程逻辑器件2021-07-22 2324

-

可编程逻辑器件设计2006-03-25 1179

-

可编程逻辑器件基础及应用实验指导书2010-03-24 786

-

什么是PLD(可编程逻辑器件)2009-06-20 30053

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1163

-

Xilinx可编程逻辑器件的高级应用与设计技巧(孙航)2012-11-28 1631

-

可编程逻辑器件学习(共10篇文档)2016-09-02 1291

-

可编程逻辑器件(书皮)2022-07-10 790

-

可编程逻辑器件原理、开发与应用2017-09-19 928

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2250

-

可编程逻辑器件的结构2023-03-24 2136

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4577

全部0条评论

快来发表一下你的评论吧 !