利用Zynq SoC的片上存储空间实现AMP通信

FPGA/ASIC技术

描述

上周我们实现了AMP(非对称多进程处理)模式,并且在ZynqSoC上实现了系统的启动和运行,在ZynqSoC的两个ARM Cortex-A9 MPCore处理器上尝试了最基本的软件应用。现在我想探索一下我们怎样利用ZynqSoC的OCM(片上存储空间)实现双核间的通信。在前面的MicroZed系列的48篇博客中,我们还没有认真的探讨过OCM,只是一带而过。现在我们要使用片上OCM,所以我们需要深入理解片上OCM,其实就像其他的ZynqSoC片上资源一样,OCM的功能比它简单的名字更加的强大。

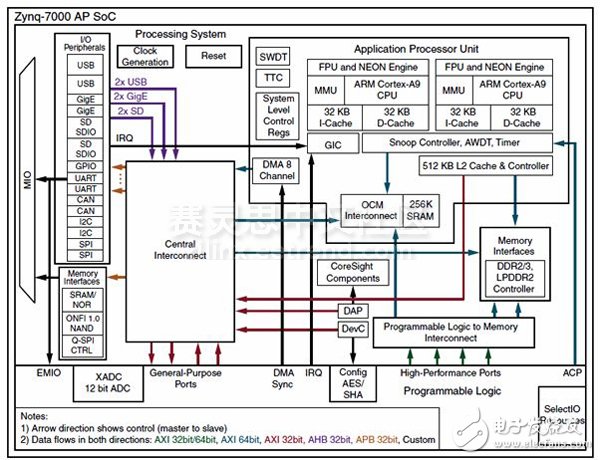

ZynqSoC拥有片上256K字节的SRAM存储空间,共有四个资源可以访问它,下图展示了Zynq PS(处理器系统)部分的结构图:

以下片上资源可以访问OCM:

1.通过SCU(监听控制单元)片上的两个ARM Cortex-A9 MPcore处理器都可以访问OCM

2.通过SCU(监听控制单元)PL(可编程逻辑)部分利用AXI ACP接口可以访问OCM

3.通过OCM interconnect结构PL部分利用AXI High Performance接口可以访问OCM

4.通过OCM interconnect结构,Central Interconnect可以访问OCM

这么多不同的片上资源都可以访问OCM,因此在我们使用它之前必须要深入理解OCM的操作与控制方法,这非常的重要。

因为这么多种复用接口的资源都可以访问OCM,所以定义访问协议的仲裁和优先级机制是非常有必要的。SCU的读写操作具有最高的优先级(读操作的优先级比写操作要高)。由OCM interconnect发起的读写操作具有第二高的优先级。注:你可以翻转SCU写操作的优先级与OCM interconnect访问的优先级,方法是修改OCM控制寄存器,将SCU写操作的优先级设置的低一些。

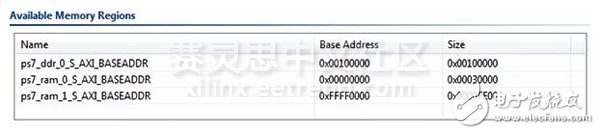

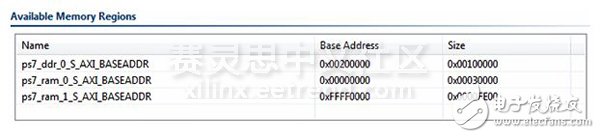

OCM可以组织成128位的字存储空间,根据PS部分定义的地址空间OCM存储空间可以划分为四块64k字节的不同位置的存储区域。初始配置是将前三个64k字节的存储块映射到PS部分起始的地址空间,最后一个64K字节存储块映射到PS部分的末端的地址空间,你可以查看下图中链接文件的地址空间的定义(上图为Core 0的地址空间映射,下图为Core 1 的地址空间映射):

注:ps7_ram_xxx与ps7_ram_1映射到内存的区域0和区域1,不是Core 0 与Core 1的地址空间。

OCM存储空间的地址映射图是能够重写规划的,所以是完全连续的,可以映射到地址空间的末端。你可以利用系统级控制寄存器和OCM配置寄存器,通过设置合适的RAM 高位的每个比特位的值完成对OCM存储地址映射空间的配置。

OCM是一个单端口的存储空间,但是你可以利用ZynqSoC的DMA并行访问OCM其他的交换资源模拟出一个双端口的存储空间。要实现这个机制,访问必须是128位数据对齐,不管在任何情况下都要满足。这个方式能够实现较高的吞吐量,因为DMA可以实现高效的传输大量数据。

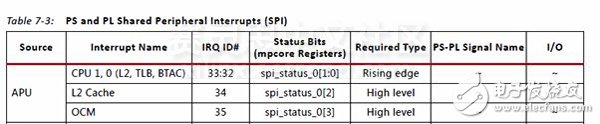

如果我们将OCM运用到一个要求相当严格的应用中,我们也可以使用OCM 奇偶校验控制寄存器添加错误保护机制。你可以分别设置奇校验或者奇偶校验,通过这个寄存器我们也可以配置ZynqSoC怎样处理奇偶校验的错误(通过输出OCM共享的中断35错误或者例如当检测到读操作错误时,传送一个AXI 读错误(SLVERR)信号)。

-

IN100 eFuse存储空间分布橙群微电子 2023-06-12

-

如果存储空间已满,我该怎么办?2012-01-23 46551

-

I/O存储空间什么意思?2018-05-29 4925

-

DSP的存储空间分配说明2019-05-07 2891

-

如何利用PROGMEM将数据写到内存(程序存储空间)啊?2021-07-08 1646

-

存储空间的分配2021-07-28 1482

-

8051单片机有三个存储空间2021-11-18 3086

-

在STM32G4片内不同存储空间运行的速度差异是什么2022-01-11 1268

-

Adam Taylor玩转MicroZed系列50:AMP(非对称多进程处理模式)和Zynq SoC的OCM(片上存储器)2017-02-08 1137

-

MCS-51单片机存储空间的介绍以及划分2018-02-08 28461

-

云存储空间的概念2020-05-09 3104

-

C语言存储空间与MCU(单片机)2021-10-28 696

-

云存储空间已满怎么办?2023-11-14 10089

-

Synology如何使用Nvme固态做存储空间2024-10-09 489

-

电脑制作云存储空间,如何使用电脑制作云存储空间2025-01-13 1694

全部0条评论

快来发表一下你的评论吧 !