基于FPGA的交流电机驱动器的电流控制器2

FPGA/ASIC技术

描述

FPGA技术允许在灵活的设计环境内开发特别的硬件结构。相比微处理器和DSP处理器的标准结构来说,FPGA的这项特点给设计者有了很大的自由度,这是因为它能建立特别的硬件结构,如此去匹配一系列控制性能和实施局限的要求。因此,考虑到为了给保护所有有潜力算法的平行性而树立榜样,这些专用结构均是建立在完美算法的基础之上设计的,而此算法是匹配控制算法和最终硬件的实现。然而,在很多情况下,基于FPGA的控制结构的设计太直接且需要设计者掌握几门不同的知识(如微电子学、控制学以及电机学等理论),这一要求尤其表现在如电机驱动中的复杂控制算法结构。如此自然导致很多设计者更喜欢去选择DSP的标准处理方案。因此,为了使控制算法的设计变得更好管理和削弱直接性,设计者必须得严格遵守一套步骤和规则,即一种有效的设计方法。这种方法的主要特征是供许多现成设计所通用,实现消耗资源和目标元件的最佳化,同时兼顾控制性能,最后,还能缩短开发时间。几位学者已经提出了一种引众人关注的设计方法[22]-[26],而这些都是建立在可重复利用的友善开发步骤的基础之上。这将在下面一幅图片中表示出来,这些计划方案的特别之处寓于既成事实的设计之中,但却总让人怀疑控制工程师为何不是一个微电子学专家。原因是占极其重要作用的设计步骤在Matlab-Simulink友好的设计环境下成功地实现了。然而,另外的关键问题却是去考虑控制性能,因此,最终的硬件结构需要最佳优化。因此,使用Matlab并不意味着极高速硬件描述语言(VHDL)[27]代码在主要的FPGA制造商提供的建议工具箱下能够自动生成,这是考虑到一系列资源的消耗问题而不得不采用非最优化方案。因此,为了建议合适的方案,设计者不得不用VHDL代码描述他自己的算法结构,但是他需要在A3[28]技术大力的帮助下才能完成。众所周知,这种A3技术是平衡两种相反需要的方法,换句话说:1)有好的方法对非专业的设计者不能造成威胁;2)考虑到控制性能的需要,必然导致设计者在设计过程中花费很大的努力心血,然而必须陈述设计方法的主要步骤。

控制算法的模块划分

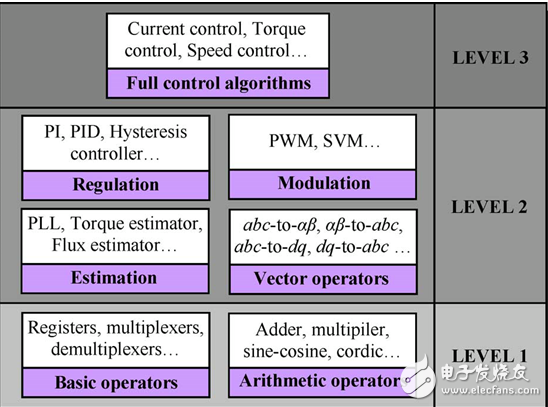

在复杂的控制算法中,这个步骤是至关重要的。它的主要目的是缩短设计周期,即“上市时间”。它内容包括即是把整个控制算法划分成一些较小的子模块,而这些子模块是容易开发且具有某一定功能意义的。这些可以被几个可重复利用且独立的模块如校准器、调制器、评估器和矢量操作器按照层级和规范性概念来鉴别认定[5]。层级概念通常是指划分一个大规模且复杂的设计成一些更便于管理的子模块,而规范性概念的目的是最大化的利用现有的设计模块。然而,与此同时,设计者不得不检查已选择的算法——模块化分离——以满足集成规范。这一规范要求在目标器件的硬件资源条件受到限制条件下必须执行某些过程。接下来为了此目的讲述一个最优化程序计划[28],它将使硬件资源的使用率大大降低。尽管每个模块都是独立地申请,但是这些模块的数目却不少,故考虑到硬件资源的消耗问题,整个模块的性能水平就会降低。因此,如果硬件配置达不到要求,那么尽管减少了一些可利用的现场设计模块,设计者也必须减少模块的数目。不同的可重复利用的模块有着不同程度的抽象概念,因而能够被提出而加入到电子系统的控制库。这个库尽管有用但是还在建设当中[29],如图12所示,它主要由三个不同等级水平组成。据笔者经验可知,这三个不同等级的模块能充分展示电子控制系统的不同功能。最高和最低等级的模块包括微粒操作器如寄存器和算法操作器(加法器、乘法器等)。而中间等级的模块包括电子控制系统中最常用功能的模块,如连续PI控制器,PWM,矢量变换等,这些模块使用第一等级的操作器搭建而成。最后,整个控制算法组成库中第三或者最高等级水平的模块。

-

为交流电机驱动应用选择合适的隔离器的7个步骤2019-07-31 3103

-

交流电机驱动稳定的关键因素——电容隔离2019-10-17 2750

-

在交流电机驱动中实现隔离方法2019-11-05 3868

-

利用电容隔离解决交流电机驱动中的关键挑战2019-12-25 2207

-

电容隔离——解决交流电机驱动中的关键挑战2020-01-05 3284

-

基于矢量控制的高性能交流电机速度伺服控制器的FPGA实现2016-04-26 607

-

基于FPGA的交流电机驱动器的电流控制器12017-02-11 1987

-

mc3526交流电机控制器接线图2017-12-23 62607

-

HJ05系列低压交流电机控制器的详细产品说明书资料免费下载2018-09-28 2331

-

向量控制交流电机驱动器VFD-BW使用手册2021-03-18 1148

-

交流电机调速器2021-09-28 4094

-

交流电机控制器主要的三种控制类型是什么?2023-02-08 4426

-

什么是交流电机控制?2023-03-26 1273

-

三相交流电机正反转固体控制器的设计2023-03-27 839

-

基于Arduino通用交流电机速度控制器2023-06-25 1035

全部0条评论

快来发表一下你的评论吧 !