基于FPGA的交流电机驱动器的电流控制器3

FPGA/ASIC技术

描述

仿真和算法改进步骤

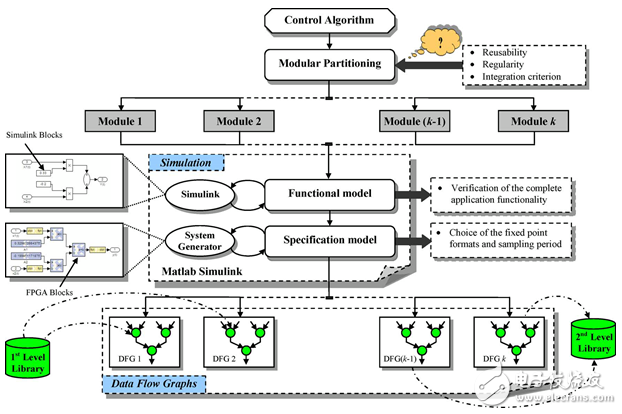

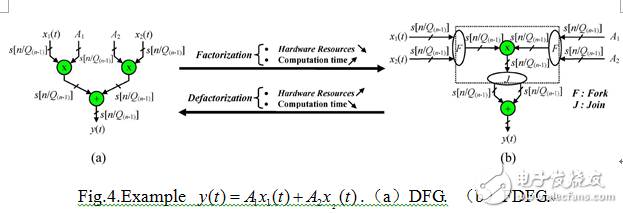

正如之前所提到,仿真步骤在Matlab-simulink软件环境中已经演示过。它的目标是: 改变完整的控制系统的功能;根据控制系统的缺陷所需,找到每个控制变量合适的采样周期和定点格式改进。在利用仿真连续时间模块情况下,功能模块的发展能够促使这些功能成功地改变。然而,每个组合数字算法的参数化是在研究采样周期和定点格式的影响下得到的。注意到这一点,每个定点格式的选择都源于可适应的方法[30],[31]。在此等级下,仿真是在使用系统生成工具箱的数字定点专用模型的发展下实现的[32]。然而,对于每个提出的第二等级的模块来说,提出了数据流曲线图这一概念(DFG)。DFG是算法的图形再现,它包括不定时的规范,由点和边沿组成。每个点表示一个简单的算法操作,或一个简单的数学或逻辑功能,每个边沿对应数据转换。例如,如图4(a)所示,第二算法等级的DFG图展示了下式功能:(1)正如关联图DFG所示,在并行模式中可以完成两种应用,但是附加的应用依赖于两种应用的已得结果,并且只有在两种应用取得结果的条件下才能实现。因此,DFG图明确地表示数据依赖关系性和算法的潜在并行性。图3表示了提出的不同的步骤。值得注意的是,到目前为止,关于目标器件的抉择还没能得到,因为模块分离和定点改进也适用于DSP控制器[33]。

步骤最优化

步骤最优化是建立在A3技术的基础之上的[28],此方法的目的是,若进行基于FPGA设计,那么它是在满足空间和时间限制下达到给出算法的硬件结构最优化。在每个DFG图中,某些操作使用数次。如果某些操作使用了n遍,那么A3将进行因式分解处理但仍然适用于此操作,只不过它是仅使用了m遍,而m

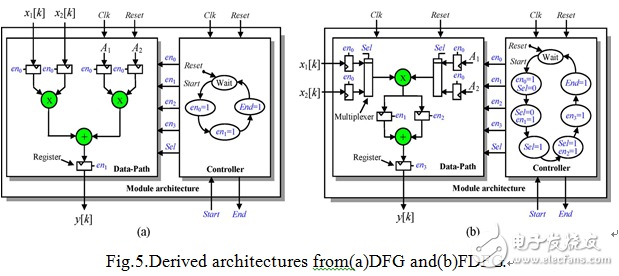

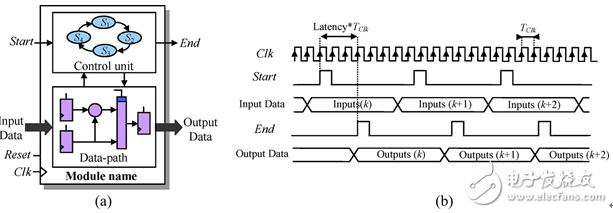

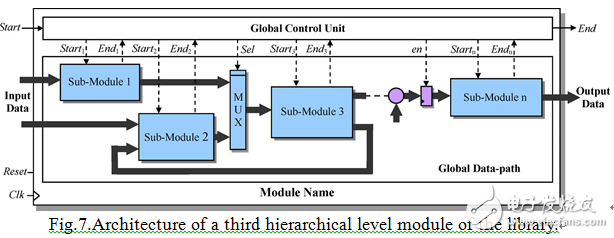

对于库中每个模块,都需要定义一个数据通道和一个控制装置。结构中的数据通道可以用来代替最终图形中的节点所对应的操作器以及边沿对应的操作器之间的数据总线。数据总线转换由控制装置控制管理,它简单地可以被称为有限状态机(FSM)。图5(a)和图5(b)结构分别对应图4中DFG和FDFG。值得注意的是,已获得的数据通道其实是对应图形的拟拷贝,此外,因式分解的结构较未能因式分解的结构的潜力大很多。

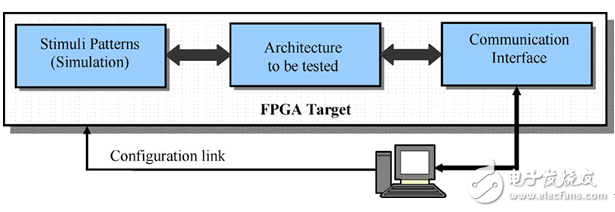

验证的第一步是使用Modelsim和Maltab软件工具一起进行过程运作仿真。这一步骤允许通过编写VHDL修改设计结构中的良性功能,同时可以经过一系列实验平台输入波形进行测试。第二验证步骤是在系统级程度上通过硬件在回路运行步骤完成的,这个过程的目的在于确保第一次实验担保,它通过在测试结构中进行硬件实时完成的,如图8所示,它主要包括三个模块。第一个是产生促进模式,并保存在FPGA存储模块中。这些促进模式直接来源于模拟阶段,能够与模拟系统进行进一步比较。第二个模块是被用来测试的结构,第三个模块是一个连接FPGA和PC主机的通信接口模块。此结构的计算输出应当集中进行测试并通过通信接口送往PC主机,此目的是为了与在Matlab环境下仿真的结果进行比较。一旦这个测试结果被验证成功,那么次设计的结构将可以应用于实际。

模块化硬件结构设计

验证设计结构

-

为交流电机驱动应用选择合适的隔离器的7个步骤2019-07-31 3100

-

交流电机驱动稳定的关键因素——电容隔离2019-10-17 2745

-

在交流电机驱动中实现隔离方法2019-11-05 3859

-

利用电容隔离解决交流电机驱动中的关键挑战2019-12-25 2198

-

电容隔离——解决交流电机驱动中的关键挑战2020-01-05 3276

-

基于矢量控制的高性能交流电机速度伺服控制器的FPGA实现2016-04-26 607

-

基于FPGA的交流电机驱动器的电流控制器12017-02-11 1978

-

mc3526交流电机控制器接线图2017-12-23 62571

-

HJ05系列低压交流电机控制器的详细产品说明书资料免费下载2018-09-28 2318

-

向量控制交流电机驱动器VFD-BW使用手册2021-03-18 1141

-

交流电机调速器2021-09-28 4086

-

交流电机控制器主要的三种控制类型是什么?2023-02-08 4411

-

什么是交流电机控制?2023-03-26 1260

-

三相交流电机正反转固体控制器的设计2023-03-27 831

-

基于Arduino通用交流电机速度控制器2023-06-25 1022

全部0条评论

快来发表一下你的评论吧 !