在FPGA开发中尽量避免全局复位的使用?(3)

FPGA/ASIC技术

211人已加入

描述

全局复位对时序的要求真的很关键吗?

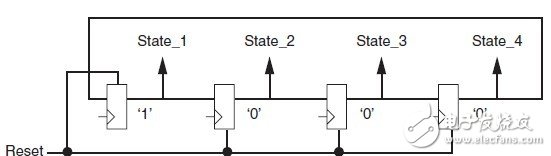

好消息是,在绝大多数设计中(白皮书说是超过99.99%?应该是老外写文档的习惯吧),复位信号的时序是无关紧要的——通常情况下,大部分电路都能够正常工作。然而,只要你曾经遇到过复位信号不正常导致电路无法正确工作的情况,那么可以说你“幸运”地遇到了那0.01%的复位信号异常的情况。图4给出了一个流水线复位的情况。

在流水线中,假如数据都是完全顺序处理的(即不存在反馈、环路等情况),则主复位信号是何时产生的是完全无关紧要的。经过几个周期的流水线操作,任何不正常的数据状态都将被从系统中“冲出”流水线,这是很容易理解的。事实上,在正常的流水线操作中,我们也很少会用到复位操作的,因为这是完全没有必要的。即使是在仿真环境中,我们也往往会在测试程序中对初始状态进行配置,从而将所有的未知状态从系统中清除出去,使得系统中的所有输入都变为有效的数据。

然而,在图5所示的独热码状态机的情况下,复位信号的时序却的的确确成为了系统正常工作的关键因素之一。

图5 独热码状态机的复位

图5 的例子中演示了一个简单的的独热码状态机的复位示意图。图中清晰地显示了复位失败的潜在可能性。如果第一个含有独热码的触发器比第二个触发器提前释放一个时钟周期,则其含有的独热码将丢失,整个状态机将永远进入无效状态(cold)。减小这种情况发生的概率往往可以通过使用相邻的触发器构成状态机来解决(使用本地复位网络,则信号的失真度较低),但前提是时序约束中的建立时间必须满足。此外,如果所有的触发器无法在同一个时钟信号的有效边沿被释放,,则一个已经编码的状态机可能会调变进入未知状态,包括非法状态,造成电路无法正确工作。所以,在包含反馈通路的电路设计者,需要对复位信号的时序要求进行仔细考虑。事实上,不存在反馈通路的电路是完全不需要使用复位信号的。例如,在数字信号处理应用中,有限脉冲响应滤波器(FIR)就不存在反馈通路:只有在有效数据填满所有节拍时,滤波器才会输出采样值,否则不输出任何数据;所以对节拍寄存器进行复位是毫无意义的。然而,在有限脉冲响应滤波器(IIR)中,存在反馈通路,如果在一个不可靠的复位信号下对节拍寄存器进行复位并产生一个伪信号输出,则滤波器输出会受到显著的影响。最坏的情况下,伪信号带来的不稳定将导致整个滤波器陷入崩溃状态。

附件大小

tu_4_liu_shui_xian_de_fu_wei_.jpg 11.64 KB

tu_5_du_re_ma_zhuang_tai_ji_de_fu_wei_.jpg 13.59 KB

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA复位的8种技巧2024-11-16 1732

-

FPGA开发过程中配置全局时钟需要注意哪些问题2024-04-28 1522

-

不得不读的Xilinx FPGA复位策略2023-06-21 3428

-

在高速设计中跨多个FPGA分配复位信号2023-05-18 499

-

在FPGA开发中尽量避免全局复位的使用?2022-05-06 3222

-

FPGA设计中常用的复位设计2021-06-30 3694

-

FPGA全局复位及局部复位设计分享2019-05-17 3368

-

FPGA的理想的复位方法和技巧2017-11-22 6307

-

在FPGA开发中尽量避免全局复位的使用?(5)2017-02-11 1247

-

例说FPGA连载17:时钟与复位电路设计2016-08-08 10730

-

FPGA复位的可靠性设计方法2014-08-28 9335

全部0条评论

快来发表一下你的评论吧 !