静态时序分析基础与应用连载(3)

FPGA/ASIC技术

211人已加入

描述

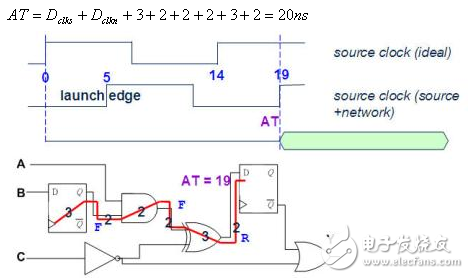

8. 假设前级Flip-Flop的讯号由1变0,计算第2条Path终点的AT。

图二十九

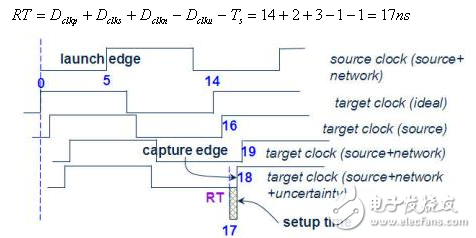

9.计算第2条Path终点的RT

图三十

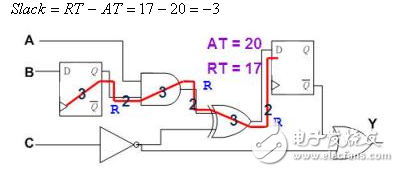

10. 假设前级Flip-Flop的讯号由0变1,计算第2条Path终点的Slack。Slack为负,因此Timing不满足。

图三十一

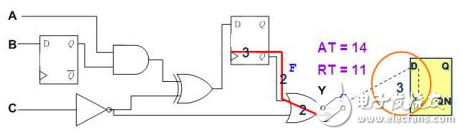

11. 假设前级Flip-Flop的讯号由1变0,计算第2条Path终点的Slack。Slack为负,因此Timing不满足。

综合10和11,第2条Path的Timing不满足,其Slack为-3。

图三十二

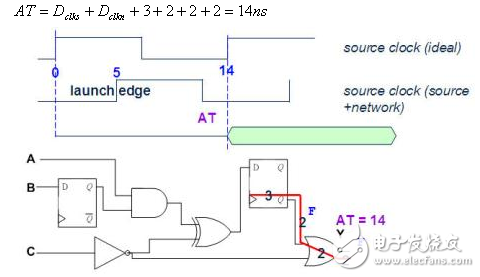

12. 假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的AT。

图三十三

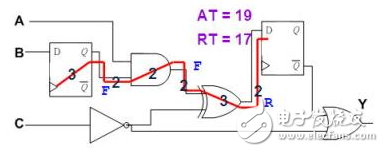

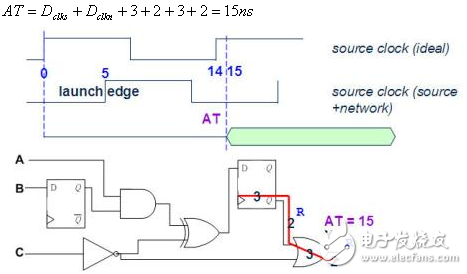

13. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的AT。

图三十四

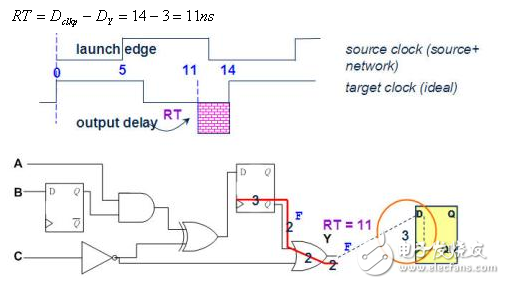

14. 计算第3条Path终点的RT

图三十五

15.假设前级Flip-Flop的讯号由0变1,计算第3条Path终点的Slack。Slack为负,因此Timing不满足。

图三十六

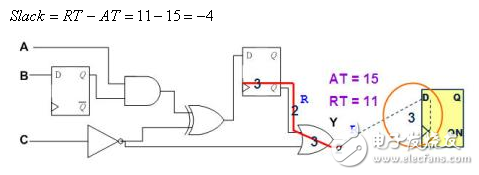

16. 假设前级Flip-Flop的讯号由1变0,计算第3条Path终点的Slack。Slack为负,因此Timing不满足。

综合15和16,第3条Path Timing不符合规格,其Slack为-4。

图三十七

综合上述分析结果,此电路的时序不符合规格,其Critical Path是Path3,Slack为-4。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

静态时序分析的相关概念2023-07-04 2309

-

静态时序分析的基本概念和方法2023-06-28 2661

-

解读FPGA的静态时序分析2023-03-14 1735

-

时序分析的静态分析基础教程2021-01-14 1197

-

华为FPGA硬件的静态时序分析与逻辑设计2020-12-21 1669

-

静态时序的分析原理及详细过程2020-11-25 11580

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2899

-

静态时序分析:如何编写有效地时序约束(一)2019-11-22 4281

-

华为静态时序分析与逻辑设计2016-09-01 1378

-

静态时序分析基础及应用2016-05-09 921

-

静态时序分析在IC设计中的应用2011-12-20 1307

-

静态时序分析与逻辑(华为内部培训资料)2010-07-09 1066

-

[求助]静态时序分析与时序仿真?2010-03-03 5009

全部0条评论

快来发表一下你的评论吧 !