Board从入门到精通系列(六)

FPGA/ASIC技术

描述

由于更新了开发工具,所以本篇博客有必要重复前面的内容,今天首先演示如何利用Vivado开发纯逻辑工程,即只在PL上进行开发。恰好最近在看雷思磊的《步步惊芯——软核处理器内部设计分析》,于是将一部分实验搬到了ZED-Board上进行验证。对OpenRISC感兴趣的童鞋可以关注Rill的专栏 进一步获得学习资源。

先简要介绍下OpenRISC软件开发,参考了雷思磊书上建立开发环境的步骤。

1.下载GNU开发环境,可以直接下载配置好的VirtualBox镜像,链接为 ftp://openrisc.opencores.org/virtualbox-image/ ,FTP用户名和密码都是openrisc。下载2011-12-15版本。

2.下载安装VirtualBox。新建虚拟机,配置为Linux, Ubuntu,512MB内存(需求并不高),使用现有虚拟硬盘(OpenRISC_Ubuntu_2011-12-15.vdi)

安装完成即可启动。GNU工具链为or32-elf-...(可以是ar, as, g++, gcc等等)。root密码:openrisc

VirtualBox中设置Windows和虚拟机的共享文件夹。关闭Ubuntu系统,在VirtualBox主界面中选择“设置”,在“数据空间”中增加Windows共享文件夹E:\Share,在Ubuntu中名称为Share。设置完成后,启动Ubuntu系统,终端输入命令sudo mount -t vboxsf Share /mnt/sharefolder

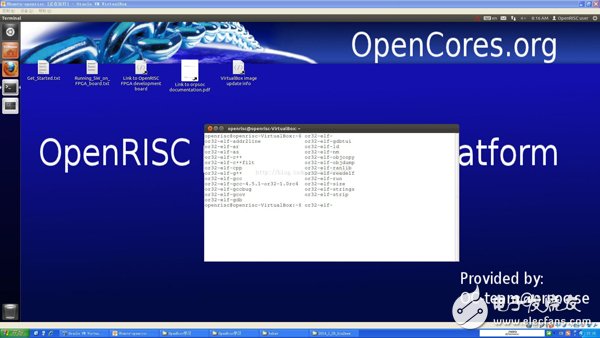

虚拟机运行后如图(如果图太大看不完全,可以右键另存为图片后在本地查看)。

3.编写简单测试汇编代码example.s

# Comments like this

# Begin

.section .text, "ax"

.org 0x100

.global _start

_start:

l.andi r0,r0,0

l.extwz r1,r0

l.extwz r2,r0

l.addi r1,r1,0x0A

l.add r2,r2,r1

l.nop 0x0001

# End

4.

编译:or32-elf-as example.s -o example.o

链接:or32-elf-ld -T ram.ld example.o -o example.or32

链接输入脚本ram.ld内容如下:

MEMORY

{

ram : ORIGIN = 0x00000000, LENGTH = 0x00005000

}

SECTIONS

{

.text :

{

*(.text)

} > ram

.data :

{

*(.data)

} > ram

.bss :

{

*(.bss)

} > ram

}

ENTRY (_start)

OR1KSim模拟器运行:sim -t example.or32 -m1M > example.trace

生成的跟踪文件example.trace内容如下:

Seeding random generator with value 0x88a2d16e

Or1ksim 2011-08-15

Building automata... done, num uncovered: 0/213.

Parsing operands data... done.

Resetting PIC.

loadcode: filename example.or32 startaddr=00000000 virtphy_transl=00000000

Not COFF file format

ELF type: 0x0002

ELF machine: 0x005c

ELF version: 0x00000001

ELF sec = 5

Section: .text, vaddr: 0x00000000, paddr: 0x0 offset: 0x00002000, size: 0x00000118

S 00000100: a4000000 l.andi r0,r0,0 r0 = 00000000 flag: 0

S 00000104: e020004d l.extwz r1,r0 r1 = 00000000 flag: 0

S 00000108: e040004d l.extwz r2,r0 r2 = 00000000 flag: 0

S 0000010c: 9c21000a l.addi r1,r1,0xa r1 = 0000000a flag: 0

S 00000110: e0420800 l.add r2,r2,r1 r2 = 0000000a flag: 0

exit(0)

@reset : cycles 0, insn #0

@exit : cycles 5, insn #6

diff : cycles 5, insn #6

从上述结果可以看到软件仿真的结果,注意r1,r2的值变化情况,后面硬件仿真时会看到。

导出二进制文件:or32-elf-objcopy -O binary example.or32 mem.bin

上述步骤、命令行参数具体含义请参考原书,此处略过不提。

为了将mem.bin文件转换为Vivado Simulator可识别的格式,博主用matlab编写了格式转换程序bin2mem.m,代码如下:

clear;

clc;

close all;

fid = fopen('mem.bin','rb');

mem = fread(fid,'uint8');

fclose(fid);

mem = reshape(mem,4,[]);

mem = [65536*256,65536,256,1]*mem;

fid = fopen('mem.data','w');

fprintf(fid,'%08x\r\n',mem);

fclose(fid);

得到mem.data后宣告OpenRISC软件开发的结束。下面利用Vivado进行硬件平台开发。

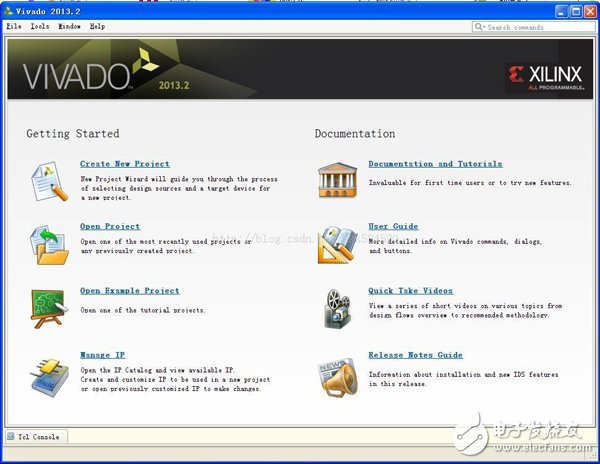

首先获得Vivado 2013.2软件,可以从xilinx官网下载。最新版的博主没有用过,不能保证所有操作步骤都一致,需要读者自行协调。

安装完成后,运行Vivado,双击下面图标,左侧为IDE,右侧为HLS,本实验只用IDE。

启动后欢迎界面如下

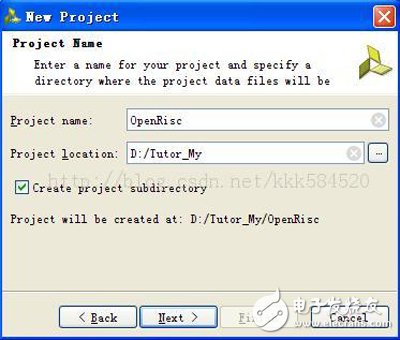

选择Create New Project,如下设置项目名称

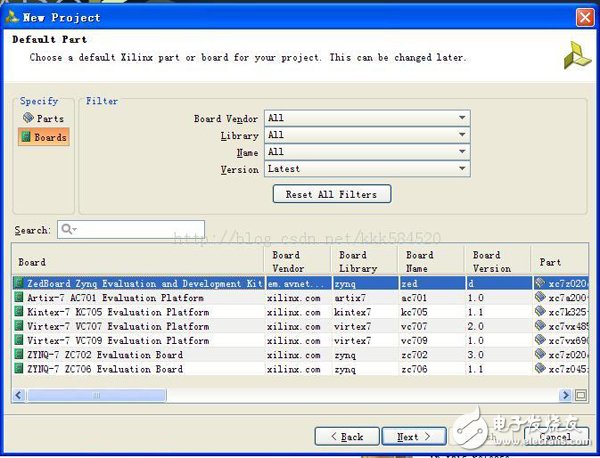

一直按下一步,到如下画面后为止

选择器件,先点Specify中的Boards,再点ZedBoard Zynq Evaluation and Development Kit。下一步,直到完成,进入IDE。

在IDE的Sources窗口中右键选择Add Sources...,添加OpenRisc verilog源码。我们将openrisc_rtl_verilog_or1200_rel3版本源码解压到本地磁盘,还需要将or1200_defines.v, or1200__qmem_top.v, or1200_spram_2048x32.v三个文件进行修改,可以下载后直接覆盖原文件,原书中有详细修改说明。

选择第二项,下一步

点Add Directories...选择源码存放目录,确定,返回IDE。这时还需要添加一个仿真激励文件,我们创建一个文件or1200_tb.v,步骤如下:

仍然在Sources窗口右键,Add Sources...

选择第三项,Next

选择Create File...,输入or1200_tb,确定,回到IDE。双击打开,修改其内容如下:

`timescale 1ns / 100ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2014/01/26 12:57:10

// Design Name:

// Module Name: or1200_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module or1200_tb();

reg CLOCK_50;

reg rst;

initial begin

CLOCK_50 = 1'b0;

forever #10 CLOCK_50 = ~ CLOCK_50;

end

initial begin

rst = 1'b1;

#200 rst = 1'b0;

#1000 $stop;

end

or1200_top or1200_top_inst

(

.clk_i(CLOCK_50),

.rst_i(rst),

.pic_ints_i(20'b0),

.clmode_i(2'b00),

.iwb_clk_i(clk_i),

.iwb_rst_i(rst),

.iwb_dat_i(32'b0),

.iwb_ack_i(1'b0),

.iwb_err_i(1'b0),

.iwb_rty_i(1'b0),

.iwb_cyc_o(),

.iwb_adr_o(),

.iwb_dat_o(),

.iwb_stb_o(),

.iwb_we_o(),

.iwb_sel_o(),

`ifdef OR1200_WB_CAB

.iwb_cab_o(),

`endif

.dwb_clk_i(clk_i),

.dwb_rst_i(rst),

.dwb_dat_i(32'b0),

.dwb_ack_i(1'b0),

.dwb_err_i(1'b0),

.dwb_rty_i(1'b0),

.dwb_cyc_o(),

.dwb_adr_o(),

.dwb_dat_o(),

.dwb_stb_o(),

.dwb_we_o(),

.dwb_sel_o(),

`ifdef OR1200_WB_CAB

.dwb_cab_o(),

`endif

.dbg_stall_i(1'b0),

.dbg_ewt_i(1'b0),

.dbg_lss_o(),

.dbg_is_o(),

.dbg_wp_o(),

.dbg_bp_o(),

.dbg_stb_i(1'b0),

.dbg_we_i(1'b0),

.dbg_adr_i(0),

.dbg_dat_i(0),

.dbg_dat_o(),

.dbg_ack_o(),

.pm_cpustall_i(0),

.pm_clksd_o(),

.pm_dc_gate_o(),

.pm_ic_gate_o(),

.pm_dmmu_gate_o(),

.pm_immu_gate_o(),

.pm_tt_gate_o(),

.pm_cpu_gate_o(),

.pm_wakeup_o(),

.pm_lvolt_o()

);

endmodule

将or1200_tb.v设为仿真的顶层文件。一切就绪,下面进行行为仿真。

在左侧设计流程中选择Run Simulation,接着点行为仿真。经过初始化,进入Vivado Simulator界面。添加信号or1200_tb/or1200_top_inst/or1200_cpu/or1200_ctrl/ex_insn,or1200_tb/or1200_top_inst/or1200_cpu/or1200_rf/rf_b/mem[1]和mem[2]到波形观测窗。

将前面生成的OpenRISC代码mem.data复制到仿真目录(根据你的工程路径设置),如下图

在仿真界面命令行依次输入restart,run 1000ns后得到结果如下

对比mem.data文件最后几行二进制代码:

a4000000

e020004d

e040004d

9c21000a

e0420800

15000001

可以看到,ex_insn信号依次呈现了上述指令,并且能看到mem[1]和mem[2]的值依次变为0x0000000a。对比前面trace文件可以知道,mem[1]即OpenRISC的r1寄存器,mem[2]即r2寄存器,依次类推。我们在进一步学习OpenRISC时,可以重点关注这些寄存器的值变化。

为了直观看到取指、译码、执行流水线,我们再加入or1200_tb/or1200_top_inst/or1200_cpu/or1200_ctrl/ex_insn/if_insn和id_insn两个信号,重启仿真过程:restart, run all.

可以看到指令沿if,id,ex三个模块依次流动,实现了流水线。

本节工程文件可以到我的资源下载。

结论:通过Vivado可以替代ISE完成逻辑开发和验证。

-

氮化镓电源设计从入门到精通的方法2021-12-29 1422

-

DSP从入门到精通全集2006-03-30 15235

-

nios从入门到精通2010-07-08 836

-

Ubuntu从入门到精通2015-10-30 1804

-

《HTML 5 从入门到精通》-中文学习教程2015-11-02 918

-

Unity5 从入门到精通2016-04-18 1536

-

java从入门到精通2016-05-04 798

-

开关电容电路从入门到精通2016-12-29 2188

-

C游戏编程从入门到精通2017-03-31 1937

-

PHP从入门到精通超完美笔记2017-09-08 1212

-

数独游戏技巧从入门到精通_从入门到精通八讲 | 高效氮化镓电源设计第六讲—EMC优化和整改技巧...2022-01-06 837

-

Android Studio从入门到精通2023-08-14 962

-

DeepSeek:从入门到精通2025-02-08 2860

-

DeepSeek从入门到精通2025-03-04 946

-

DeepSeek:从入门到精通2025-05-28 633

全部0条评论

快来发表一下你的评论吧 !