实时时钟芯片应用技术(针对芯片供电电源切换问题的解决方案)

描述

【序文】

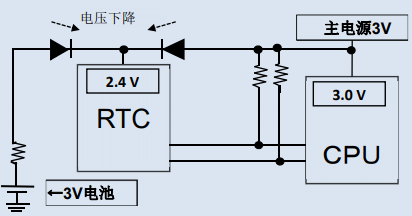

通常,实时时钟必须随石英晶体振荡频率而随时更新日历数据和时间数据。为此,需要使用备用电池保护数据以应对主电源的切断及停电。在这种电池备用电路中,主电源和电池的转换需在适当时间内进行。部分系统为此采用了专用的电源管理 LSI,而大部分系统为追求简便则采用由两只二极管构成的或门电路【图 1】。在此解说这种二极管或门电路特有的技术性课题。

【1】电池能量损耗

考虑二极管所造成的损耗时可列举出两大特性。其一是正向压降(VF)特性,另一项是反向泄漏电流(IR)特性。一般情况下所产生的 VF为 0.6V 左右,当主电源为 3.0V 时,通过二极管后的电压为 2.4V。这种电压下降意味着向充电电池和双电层电容器(以下称为“电容器”)等充电的电压下降。结果有可能导致电池充电电压下降而缩短其寿命。

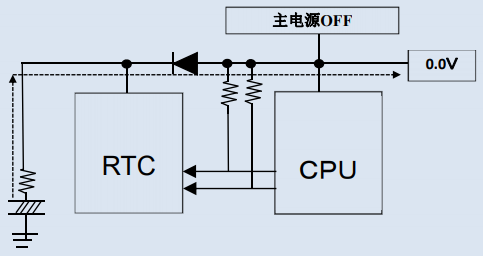

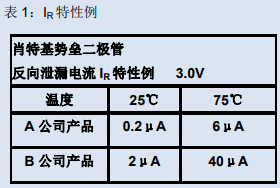

由于上述原因,不少技术人员选择使用 VF 较小的肖特基势垒二极管。肖特基势垒二极管的结构特征导致其 VF 量小,各家公司均推出了这项产品。但是,通常 VF和 IR之间为二律背反的关系,即 VF小的二极管的 IR大。IR的增大将在切断主电源时引发问题。切断主电源后,泄漏电流从电池流向电压为 0V 的电源。这正是被称为反向泄漏的理由(图 2)。而且,IR具有温度特性,温度越高越呈现二次方增长的趋势(表 1)。由于上述背景,设计人员需要根据所开发产品的温度规格范围并考虑到 VF和 IR选择最为均衡的二极管,但实际上很难找到所有条件均与系统要求相匹配的二极管(图 2)。

【2】时钟数据受损风险

在前一项中已经说明了因二极管的 VF而使 CPU 和实时时钟的电源电压之间出现电位差。若 CPU 在这种状态下访问实时时钟,来自 CPU 的输入电压有可能超过实时时钟的额定输入电压。超过额定数值后,一般的 CMOS 工艺半导体产品不少会出现内部寄存器位数无规则变化的现象。额定输入除了适用于输入接口以外,时钟输出的使能输入以及 CMOS 时钟输出端子的上拉对象也可能适用同样的额定输入电压,因此需要进行充分的确认。CMOS 半导体产品的输入最大额定值一般在 VDD+0.3V 以下。这时需把二极管的 VF 控制在 0.3V 以内,所以必然将选择使用肖特基势垒二极管。这就产生了前项所提到的 IR的问题(图 2)。

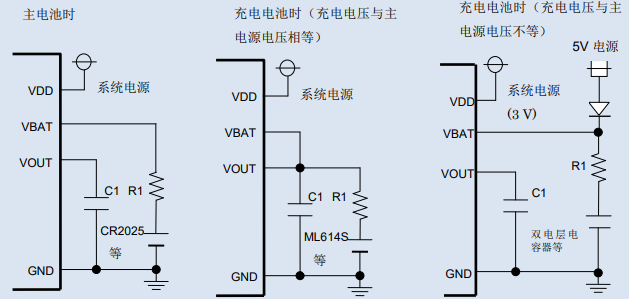

图 1:通常使用二极管或门电路的电源开关电路

图 2:切断主电源时因 IR所造成的泄漏(虛线)

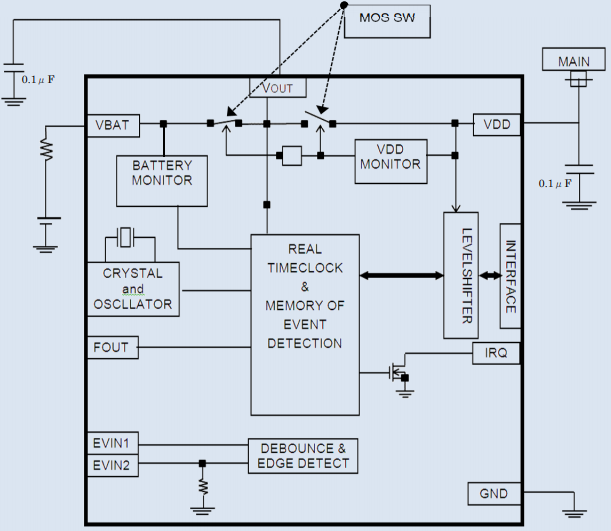

【3】RX-8035/435 中搭载的电源开关电路

本电源开关电路是针对上述二极管或门电源开关电路的设计风险而提供的解决方案。开关元件中没有使用晶体管或二极管,而采用了 PMOS 的开关。VF被控制在 0.12V 以内,通常状态下的 IR在 30nA 以下。实时时钟以外必须准备的电子部品仅为连接 VDD和 VOUT端子的 0.1μF 旁路电容器共计两只而已。

以下介绍原电池、二次电池和双电层电容器的连接方法。

-

深入剖析DS2417:实时时钟芯片的技术奥秘2026-03-24 210

-

BQ32002实时时钟芯片:特性、应用与设计要点2026-02-09 272

-

实时时钟芯片DS1302应用资料2023-09-26 948

-

NuMicro™ 家族中那些系列的芯片支持实时时钟(RTC)控制器?2023-06-27 605

-

实时时钟芯片有哪些2021-05-18 7151

-

实时时钟芯片M41T62主要特性介绍2020-08-28 4936

-

实时时钟芯片的应用资料详细说明2020-03-23 3440

-

实时时钟RTC的程序应用设计和详细资料免费下载2018-08-24 1459

-

实时时钟芯片应用2018-03-16 1612

-

实时时钟芯片有哪些_实时时钟芯片选型介绍2018-01-29 42259

-

基于实时时钟模块 时钟芯片DS13022017-10-16 1659

-

介绍一款低功耗小体积的实时时钟芯片2015-02-25 15663

-

实时时钟芯片DS3231应用笔记,使用指南,FAQ全集2014-03-14 25675

-

基于实时时钟芯片X1228的电源控制器设计2009-05-12 613

全部0条评论

快来发表一下你的评论吧 !