创建ZYNQ处理器设计和Logic Analyzer的使用

FPGA/ASIC技术

211人已加入

描述

我们的目的是创建一个Zynq Soc处理器设计,并用Logic Analyzer来调试我们感兴趣的信号。

首先,打开Vivado,创建一个工程。

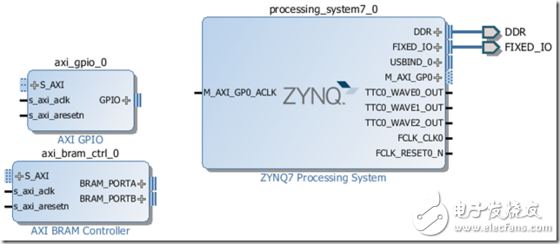

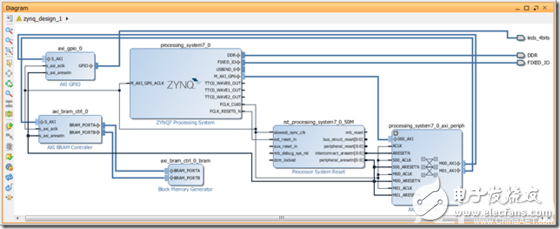

添加这几个IP核,

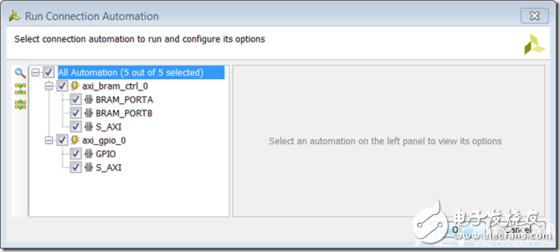

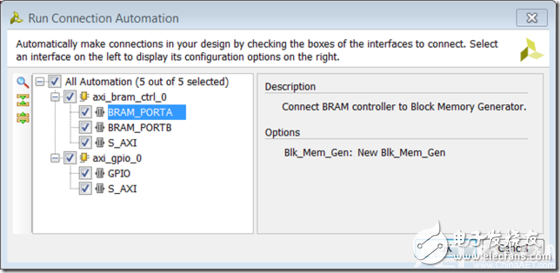

点击Run Connection Automation,让软件自动帮我们连起来。在打开的对话框中选择ALL Automation,

ok,软件自动连接起来,

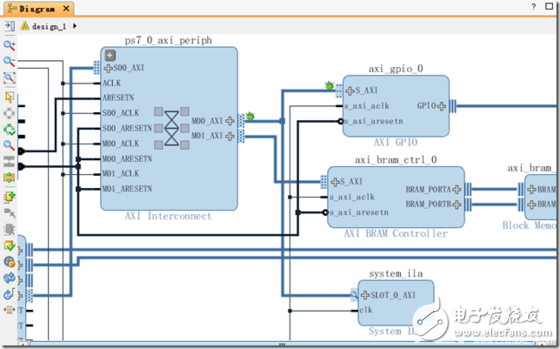

如果要观察感兴趣的信号,这里先右键--Generate Output Products,Create HDL Wrapper,编译,执行完成后,选择感兴趣的信号,右键-Mark,

那么Block框图中会有变化,如图,两只虫,

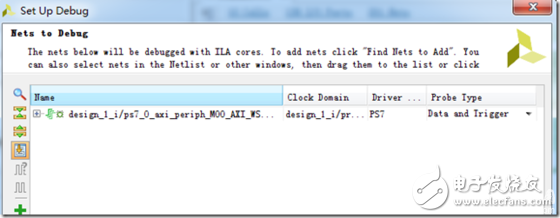

执行Set Up Debug,刚才标记的信号就会出现,

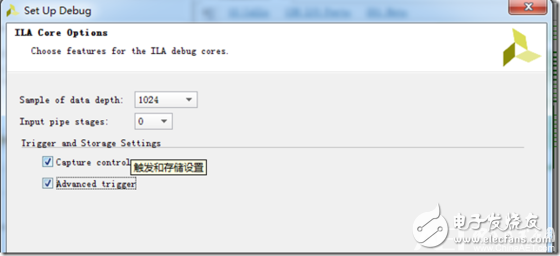

next,进行设置采样深度,

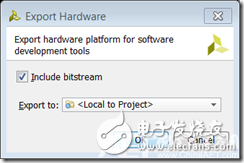

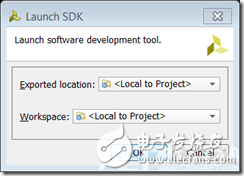

接着执行Implement Design 和 Generate Bitstream。完成后导出到SDK,

未完待续。。。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- Zynq

- Vivado

- Logic Analyzer

-

keil中Logic Analyzer可以在硬件上在线调试,为什么把全局变量加入Logic Analyzer不显示波形呢?2024-05-16 918

-

ZYNQ对比其他处理器有什么优势?2023-11-07 746

-

Zynq系列处理器中AXI接口的使用2023-10-17 2456

-

ZYNQ多核处理器硬件上的划分2022-09-19 3520

-

如何访问zynq处理器GPIO?2019-09-11 1839

-

安装05.80.1004搜索Agilent Logic Analyzer 05.80.00002018-12-11 2765

-

如何使用Vivado Logic Analyzer与逻辑调试IP进行交互2018-11-30 4049

-

如何在Zynq处理器上lwIP实现网络功能2018-11-27 6239

-

如何在Zynq Cortex A9处理器之间执行处理器间通信2018-11-26 4367

-

Zynq扩展处理器平台的电源设计如何实现2018-10-09 3568

-

请问st-link怎么使用logic analyzer?2018-08-29 5184

-

嵌入式处理器硬件设计2017-11-15 2402

-

Zynq处理器2017-08-14 3509

-

MDK Logic Analyzer 功能在STM32中的实现问题简述2015-11-25 920

全部0条评论

快来发表一下你的评论吧 !