EMC浪涌防护设计方案

描述

浪涌是每个电子工程师设计产品时都需要考虑的一个问题,因为这关乎到电子设备在恶劣的电磁环境下是否能够正常工作。

一、什么是浪涌?

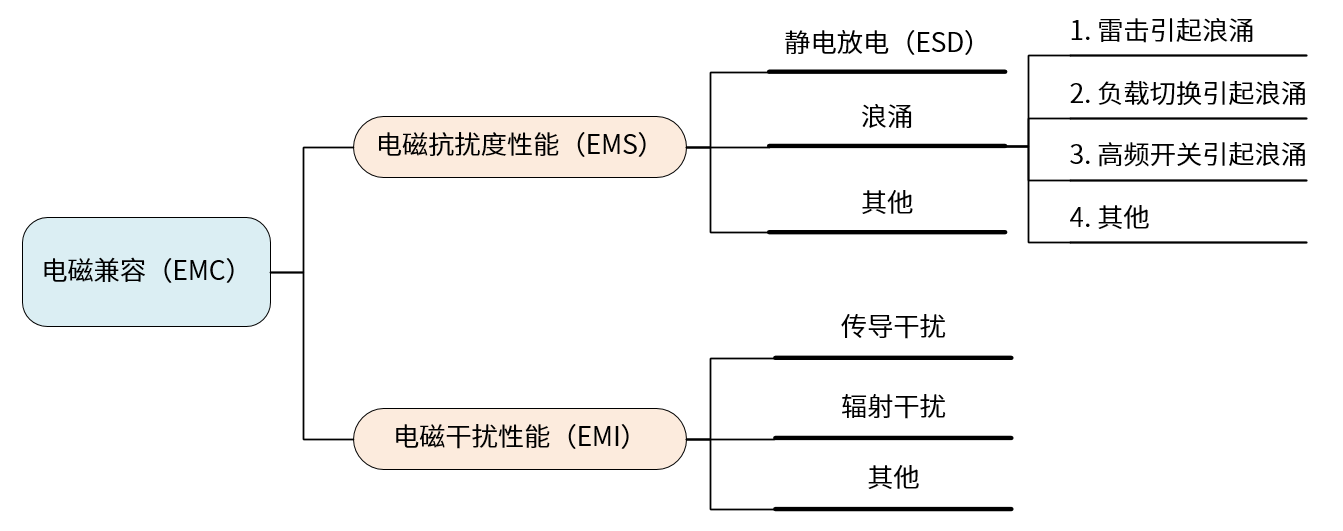

图1 EMC家族

浪涌(Surge)也叫尖峰(Spike),属于电磁抗干扰性能(EMS)的一种情况。在日常生活中,浪涌通常由外界环境如雷击和内部器件的启停、故障等原因产生,会形成若干个超出设备正常工作范围的瞬间(通常为us级别)高压或大电流,从而影响设备的使用寿命甚至导致设备故障。

为了模拟电子设备的实际抗浪涌能力,行业内形成了一个通用的浪涌防护标准:

IEC61000-4-5(GB/T17626.5)

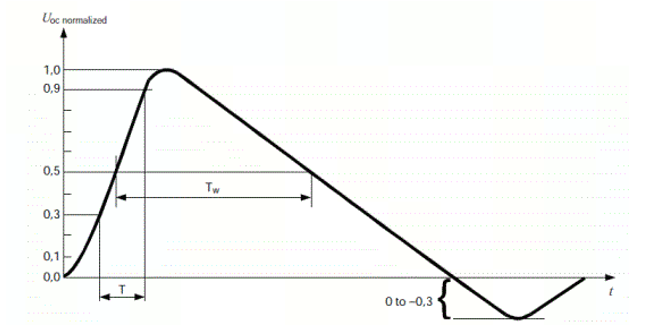

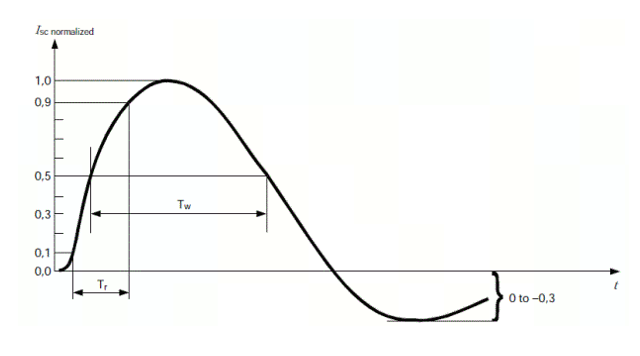

通过浪涌发生器模拟浪涌波形,来测试设备的抗浪涌能力。IEC61000-4-5:2014版标准波形,要求浪涌发生器在未连接被测设备、无耦合/去耦合网络时的输出电压、电流波形满足图2、3要求。

图2 开路电压波形

波头时间:Tf=1.67*T=1.2us±30%

持续时间:Td=Tw=50us±20%

图3 短路电流波形

波前时间:Tf=1,25*Tr=8us±20%

持续时间:Td=1,18*Tw=20us±20%

二、什么是浪涌发生器

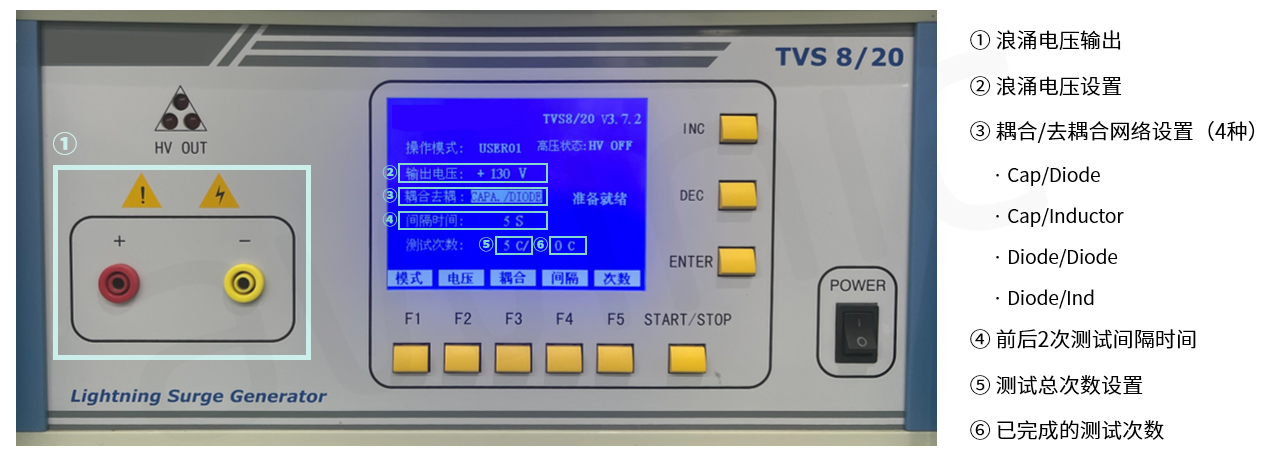

图4为智能型雷击浪涌发生器TVS 8/20的控制表盘示意图,该仪器是严格按照国际电工委员会IEC颁布的IEC61000-4-5标准设计的,具有智能化、性能稳定、操作方便等特点。通过设置输出电压、耦合/去耦网络模式、浪涌次数、浪涌时间间隔等参数后,即可使用。

图4 TVS 8/20雷击浪涌发生器

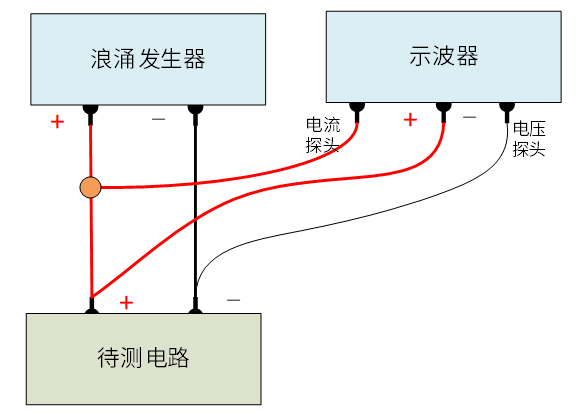

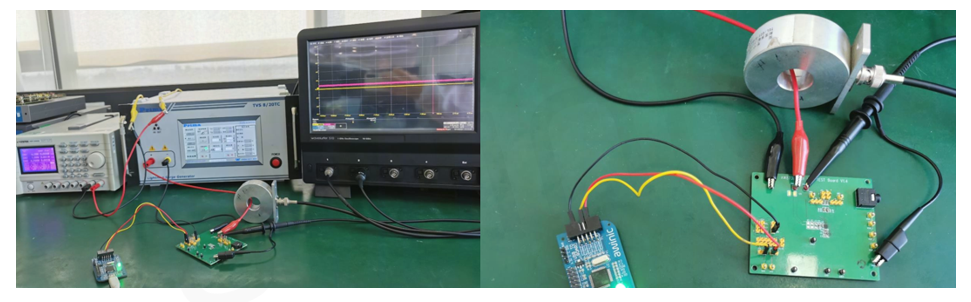

三、如何搭建浪涌测试环境

图5 浪涌测试环境示意图

图6 浪涌测试环境实物图

需要准备的仪器及硬件连接示意图如图5、6所示。 1. 将浪涌发生器的正、负极分别接待测设置的电源VDD和GND 2. 用示波器电流传感探头测试流经VDD的电流,电压探头测试VDD处的电压

注意:示波器的电压探头应尽量靠近待测芯片的VDD引脚,且地线夹应就近接地,建议用接地环测试更佳。

通常每个电压等级测试3次,逐步增大浪涌发生器的输出电压,直到芯片损坏为止。

四、常用的浪涌防护器件及选型

1. 浪涌防护器件简介

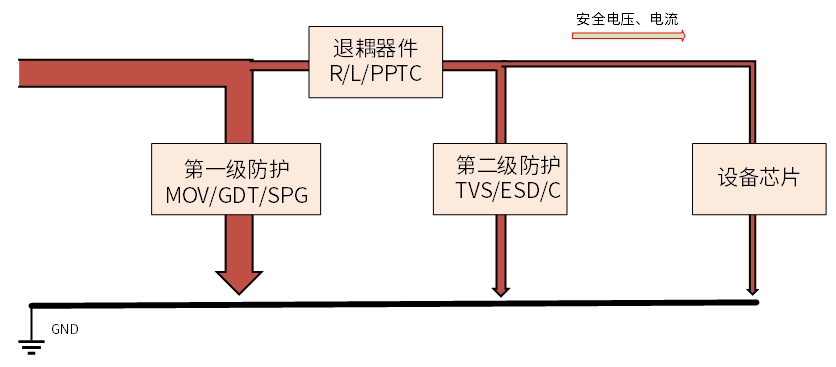

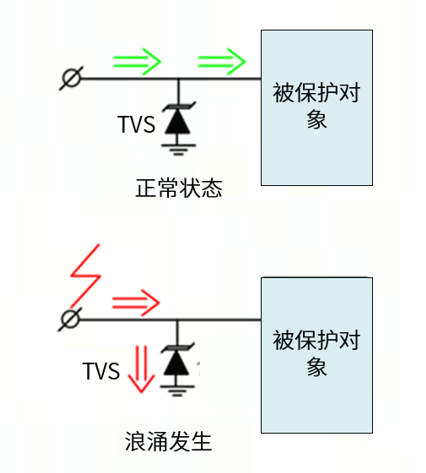

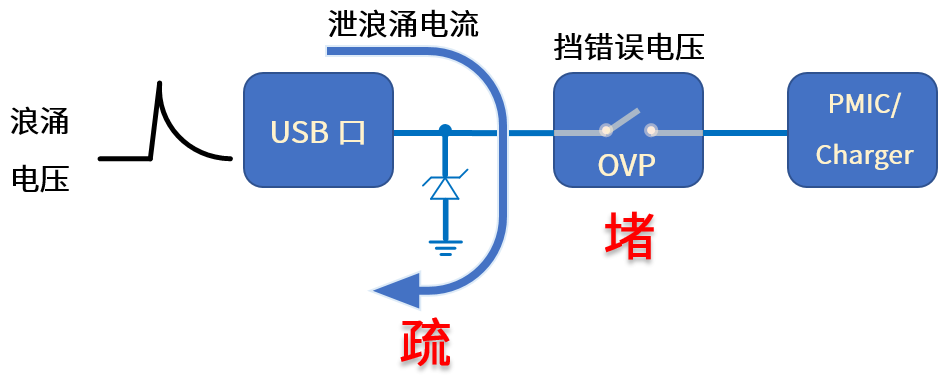

如果遇到浪涌指标不达要求的情况,我们可以采取下图所示的浪涌防护,总结为:泄放为主,阻挡为辅;多级防护,逐级削弱。

图7 浪涌防护结构示意图

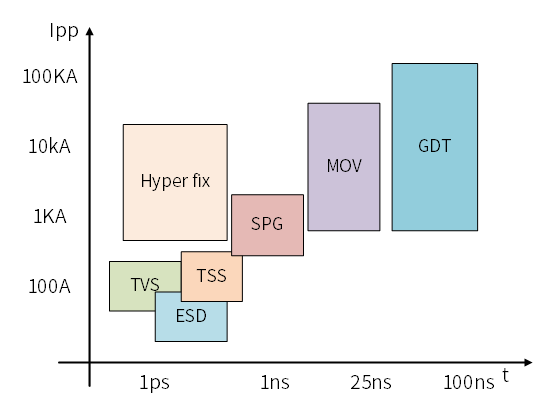

常见的浪涌防护器件有:压敏电阻(MOV)、陶瓷气体放电管(GDT)、玻璃放电管(SPG)、瞬态抑制二极管(TVS)、静电保护管(ESD)、以及阻、容元器件等。为了更加直观的了解各个器件的特性,图8是主流浪涌防护器件的泄流能力及相应速度对比框图。

图8 浪涌防护器件的泄流能力及响应速度框图

浪涌器件这么多,具体该如何选呢?对于便携式的电子设备,考虑到产品的实际应用场景、摆放空间和成本,运用最多的就是TVS瞬态抑制二极管。 顾名思义,瞬态是指电压或电流中的短时间尖峰,抑制是指消除异常瞬间电压、电流信号对器件或电路的影响,二极管是指一样具有PN结效应,当电压超过雪崩击穿电压时,就会吸收过压的多余能量,并且在过压状态结束后可以自动恢复。

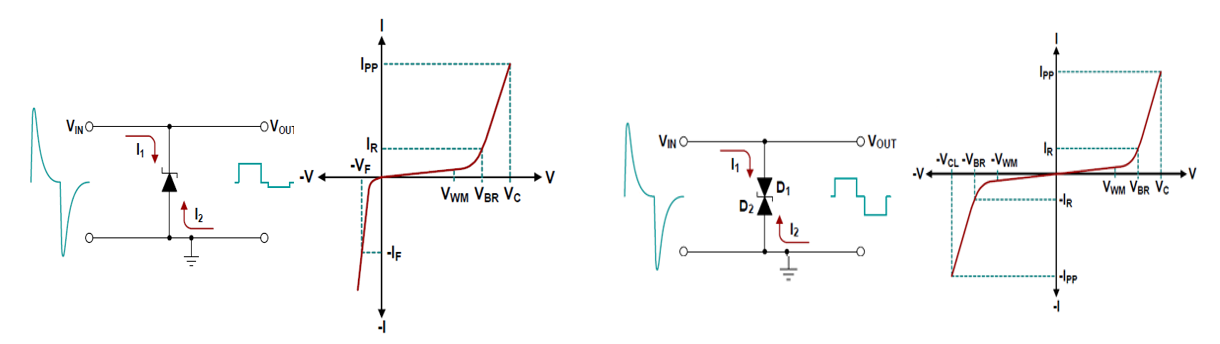

图9 单向、双向TVS管的作用方式及V-I曲线

图9可以初步了解到TVS管的作用方式以及主要指标参数,如何根据这些指标选取合适的TVS型号?

1. 确认被保护电路的正常工作电压VDD>TVS管的Vrwm

2. 确定被保护电路的最高工作电压Vdd>TVS管的击穿电压Vbr

3. 确定被保护电路的损坏电压<钳位电压Vc

4. 确定被保护电路的信号工作频率,选择合适的结电容Cj

5. 根据电源/信号抗浪涌需求选择合适的峰值电流Ipp

6. 确定电路对静态工作电流的需求漏电流IR 7. 选择合适的封装

- 其它注意事项 -

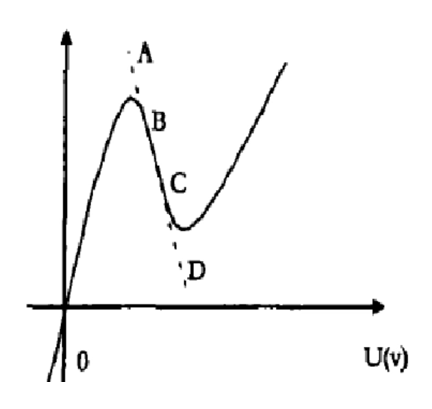

尽量不要选存在Snapback现象的TVS管。Snapback的现象就是TVS管在被反向击穿(VBR)后,当电压降到反向击穿电压VBR之下时,仍会存在较大的漏电流,即电压降低电流反而增大,所以这个现象也称为负阻现象。

图10 TVS管的snapback现象

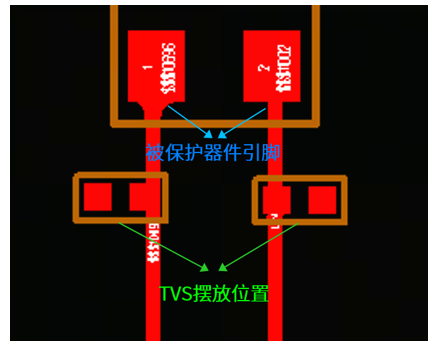

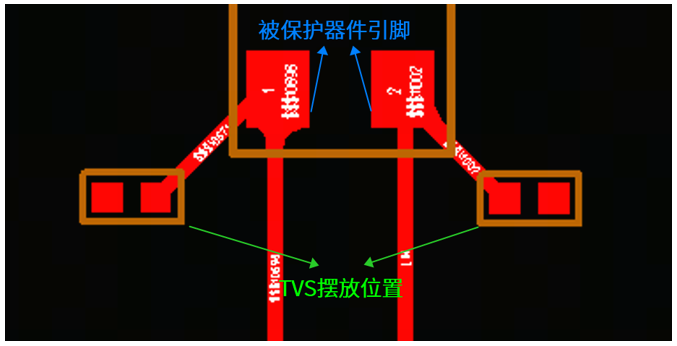

2. TVS管的layout如何布局

选好TVS管后如何布局layout使其效果最佳也是大有学问的,下面简单介绍下常用的layout手法。

No.1 TVS放置在浪涌流经的路径上

图11 TVS摆放示意图

图12 正确示例

图13 错误示例

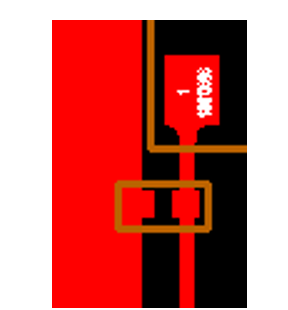

No.2 TVS走线最短且最大面积接地

图14 正确示例

图15 错误示例

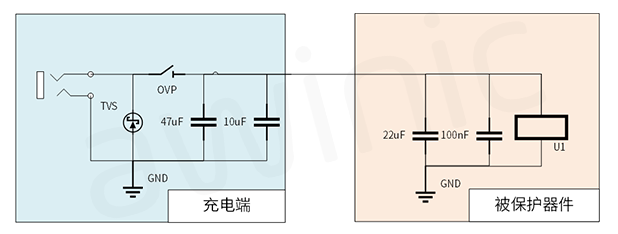

3. 电容在浪涌防护中起的作用

电容基于其特性以及实际布局空间和成本考虑,电子产品上面一般会大量使用陶瓷电容,几乎每颗芯片的VDD引脚处都要求要加电容,所以大家对电容的储能滤波作用肯定深有了解。 由于电容的物理特性:电容两端的电压不能突变。因此也决定了电容的浪涌泄放能力必然不如TVS的。但如果和“好兄弟”TVS管组合使用,是可以起到锦上添花的作用。

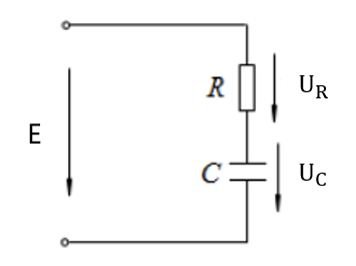

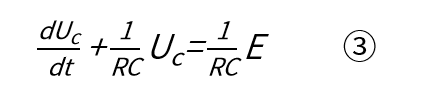

根据

以及下方的等效电路(其中R=电源内阻 Re+线损Ra+电容ESR,C为电容),

有:

将①带入②式:

令电容初始条件t=0时,Uc=0,得到③得解为

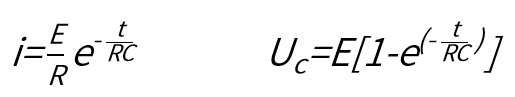

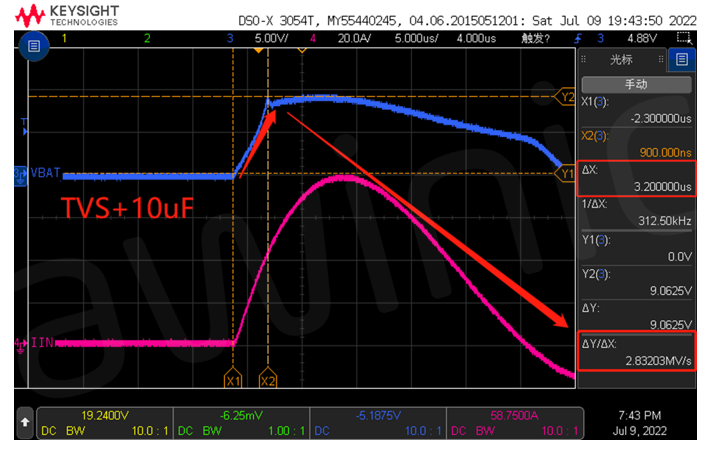

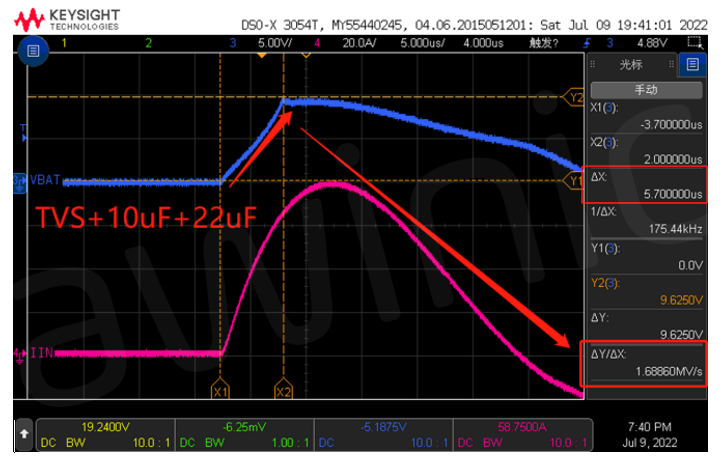

根据方程式的解可以了解到电容的两个作用: 1. 提供一条电流泄放路径 2. Uc不能突变,但能平滑脉冲上升速率 实测增加电容容值后浪涌残压变化如下图:

图16 TVS+10uF的浪涌残压变化

图17 TVS+10uF+22uF的浪涌残压变化

考虑到整机Vbat上挂的滤波电容总容值一般在100uF以上,因此对整机抗浪涌能力的提升也是有一定帮助的。

4. 艾为OVP过压保护芯片

图18 端口保护典型应用框图

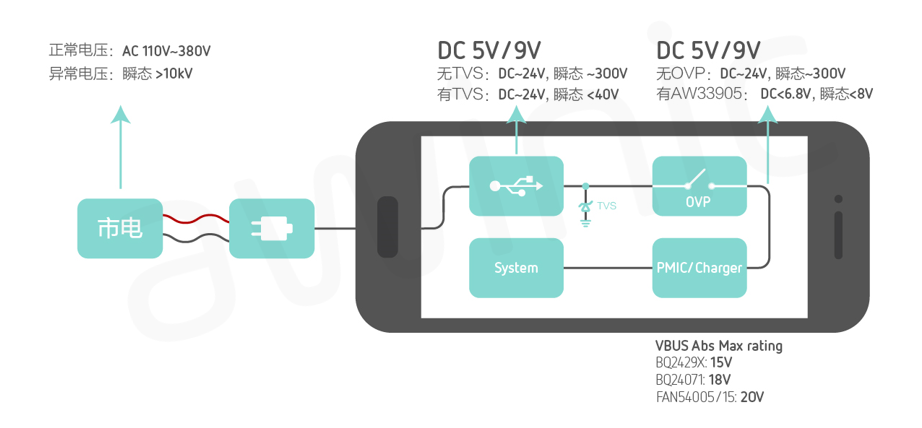

除了通过“疏导”浪涌电压来保护设备,我们还可以采用OVP过压保护芯片来”堵”住浪涌电压,即输入端电压值超过一定值后,芯片的输出端会被关断,对后级电路起到保护作用。

什么是OVP呢?OVP是一类过压保护器件,它通常被放置在系统输入接口处,通过实时检测该路径上的电压,并在输入电压超过设定阈值的情况下快速响应,切断电源通路,从而起到保护后级IC的目的。

保护后级IC免受输入过压影响的办法有很多,比如我们可以用MOS管来搭建开关回路,但是OVP IC解决方案与之相比,因其具备高性价比、高集成度、高响应速度等明显优势,被广泛应用在各种场合。

艾为推出的AW329XX系列OVP芯片内置浪涌泄放能量,从而做到以“疏”与“堵”结合的方式为系统提供全方位的安全防护,该系列IC因其可提供宽泛的输入电压范围、内置浪涌泄放路径、纳秒级的OV响应时间和极低的导通阻抗为广大客户所采纳。

更多艾为OVP芯片介绍请回顾《【技术帖】OVP的原理和应用概述》

图19 AW329XX系列OVP芯片保护效果

总 结

图20 浪涌防护设计通用防护方案

图20是浪涌防护设计的通用防护方案,浪涌从输电线引入设备,容易导致充电口损坏。通用的防护方案是:

1. 先由一级TVS进行浪涌疏导

2.经过若干退耦电容后抵达OVP器件进行浪涌阻挡

从而对后级电路起到保护作用。

以上是艾为电子对EMC浪涌防护设计的归纳总结,可能实际遇到的浪涌问题更为错综复杂,只要前期做好浪涌防护设计的评估,后期根据浪涌的指标选择合适的防护器件,就一定能跨过这个难关。

-

EMC电源浪涌防护分析方法介绍2023-08-17 4460

-

机顶盒浪涌和静电防护解决方案2015-06-11 5772

-

雷击浪涌防护方案基本设计思路2018-01-30 8550

-

RS-485端口EMC防护方案设计详解2020-01-03 2954

-

POE 端口浪涌防护方案2020-11-06 2458

-

RS485端口浪涌瞬变防护设计2021-04-08 2243

-

千兆以太网口静电浪涌防护方案设计2021-06-04 8103

-

开关电源EMC设计方案分享2021-12-28 1360

-

汽车电子的EMC设计方案2010-03-10 1291

-

LED显示屏EMC设计方案2017-02-08 1482

-

ptc自恢复保险丝浪涌防护方案分析2017-09-18 1540

-

EMC电路、雷电与浪涌防护设计资料下载2018-03-21 1530

-

485接口EMC电路设计方案2020-02-05 7858

-

汽车BMS浪涌静电防护设计方案及保护器件选型2024-08-02 2681

-

长距离POE供电模块静电浪涌防护方案2025-09-12 1628

全部0条评论

快来发表一下你的评论吧 !