Xilinx的RGMII 的PHY层逻辑设计详解

电子说

描述

今天讲解是RGMII的FPGA设计。因为这边文章主要是用XILINX的约束工具,所以标记为XILINX,其实你用altera平台也可以的。设计分为2部分,一部分讲解MDIO操作和IEE802.3寄存器要求。另外一部分主要讲解PHY层的软件设计。

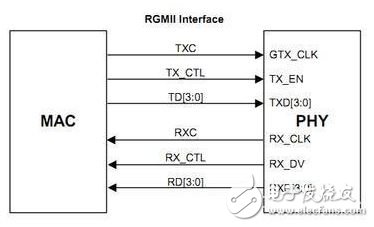

RGMII是千兆网总线,但是比GMII差别在于数据发送和接受是4BIT,RGMII是双边得到数据,所以千万要注意约束双边沿的数据。观察RGMII是不是跟MII很像,所以兼容总线100,M/10M接口。

有人问我,是不是很蛋疼,为啥不用ALTERA和xilinx的 TRI-mode MAC ip核心设计。关键三模式MAC的IP只能挂在nios或者microblaze一类处理器,你还要学习这些处理器平台。而且很多工业以太网也不是基于TCP/IP协议的。所以这次有必要讲述PHY层的操作。

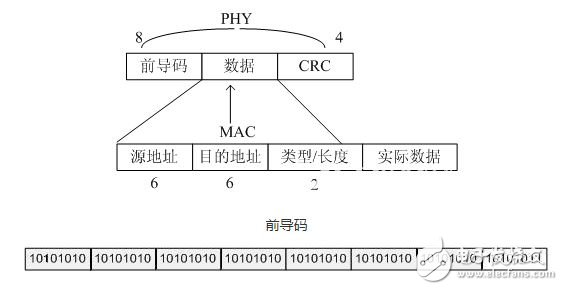

对于PHY模式和MAC模式,主要差别MAC没有前导码和4个字节的CRC32校验码。而PHY层是带这些。经常使用PC软件发送是MAC层发送。

可以看出前导码是固定,CRC我们下载已经搞好。已经上传了基本CRC的算法文件。CRC32_8_CONTROL.rar?,有人问我为啥要用CRC32校验,如果你不用CRC32,你发给PC,pc不会认你的以太网包的。 ? 注意,CRC校验是不包括前导码还有CRC32的4个字节数据。

crc32_8 crc32_8_inst

(

.crc(crc) , // output [7:0] crc

.d(p_data) , // input [7:0] d_sig

.calc(calc) , // input calc_sig

.init(init) , // input init_sig

.d_valid(d_valid) ,// input d_valid_sig

.clk(clk_125mhz) ,// input clk_125mhz

.rst_n(rst_n) // input rst_n

);

if((p_data == 8‘hd5) &&(cnt_pre 》= 4’d7))

begin //开始CRC校验

calc 《= 1‘b1;

d_valid 《= 1’b1;

init 《= 1‘b0;

end

else if(cnt_crc 《 3’d4) //4个字节的校验码

begin

d_valid 《= 1‘b1;

calc 《= 1’b0;

init 《= 1‘b0;

cnt_crc 《= cnt_crc + 1’b1;

cnt_pre 《= 4‘d0;

end

else

begin //数据无效,对校验程序设置初始化值

d_valid 《= 1’b0;

calc 《= 1‘b0;

init 《= 1’b1;

end

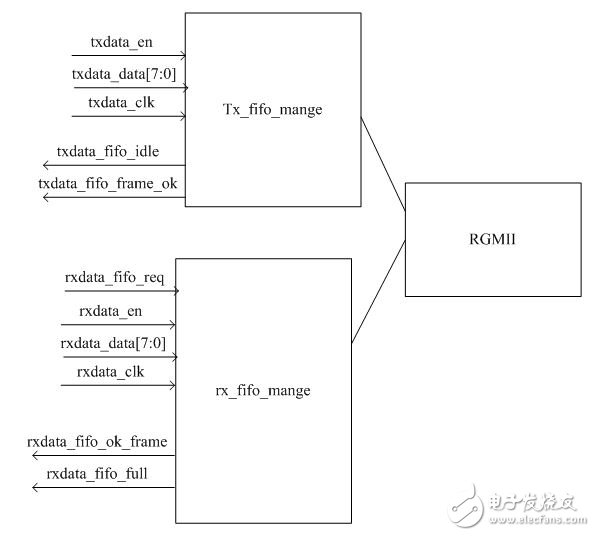

上述基本问题已经初步解决,关键怎么看待这个设计给用户怎么一个好的接口。初步设想使用两个读和写fifo来兼容三种不同的速度模式。在发送的fifo中提供发送fifo的空闲标示,标示可以发送数据。而接收的fifo上面提供完整帧指示,读缓冲满指示。

-

数字电路与逻辑设计2024-03-11 709

-

RGMII接口案例:二个设备共享一个PHY2023-11-27 10238

-

FPGA 控制 RGMII 接口 PHY芯片基础2023-06-06 1968

-

RK3288 RGMII如何连接百兆PHY DP83822?2022-03-03 1712

-

《数字电路与逻辑设计》李晓辉版课后答案详解2021-12-27 5516

-

逻辑设计是什么意思2021-11-10 1410

-

基于RGMII+phy的典型应用快速入门2021-09-29 8235

-

RGMII应用框图/接口信号/帧格式2020-12-14 8534

-

RGMII接口信号和帧格式_RGMII接口应用框图2020-09-30 33466

-

静态时序分析与逻辑设计2017-12-08 3403

-

《数字电路与逻辑设计》答案2012-06-25 851

-

RGMII总线上挂两片PHY是否可行2012-04-25 5068

-

组合逻辑设计实例_国外2011-12-16 1112

-

ASIC与大型逻辑设计实习教程2010-06-19 688

全部0条评论

快来发表一下你的评论吧 !