为什么说Cortex-M是低功耗应用的首选

物联网

描述

虽然Cortex-M处理器家族目标瞄准效能光谱较低端的区域,但是和大多数微控制器(MCU)采用的其他典型处理器相比,Cortex-M的效能依然算相当强悍。举例来说,像是许多高效能微控制器所采用的Cortex-M4与Cortex-M7处理器,其最高时脉频率就高达400MHz。

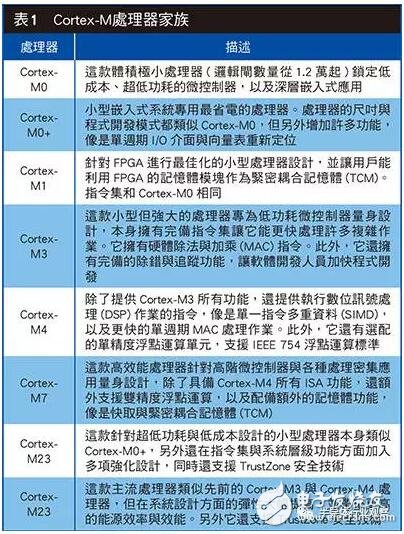

当然在选择处理器时效能并非唯一考量的因素。在许多应用中,低功耗与成本是顾客最关切的标准。因此,Cortex-M处理器家族纳入各种类型的产品来因应不同的需求(表1)。

Cortex-M和传统ARM处理器(像是ARM7TDMI、ARM9)大相径庭之处,就是大幅改造的架构。举例来说:

·仅支援ARM Thumb指令,但在Thumb-2中,已延伸成能支援16位元与32位元指令。·中断处理任务,由名为巢状向量中断控制器(NVIC)的内建中断控制器执行,NVIC提供自动优先排程、中断遮罩与巢状配置、以及系统例外处理。

·中断处理程序(Handler)可写成正规的C语言函式以及向量化中断处理机制,不须使用软体去判断该服务哪个中断。而中断的回应则属于决定性,并具有低延迟特性。

·中断向量表方面,从分支指令改成中断的起始位址以及系统例外处理程序。

·暂存器区块(bank)以及程式开发模式的部分细节亦有所变动。

这些改变意谓许多针对传统ARM处理器撰写的组合语言程式码必须进行修改,而旧的Projects档在移植到Cortex-M时必须进行修改与重新编译。

指令集概述

在大多数情况中,软体的程式码多以C或其他高阶语言撰写。不过,如果对Cortex-M处理器所支援的指令集有基本的认识,能帮助判断特定任务须要用到哪一种Cortex-M处理器。指令集架构(ISA)是处理器架构的一部分,Cortex-M处理器能区分成几种架构类型(表2)。

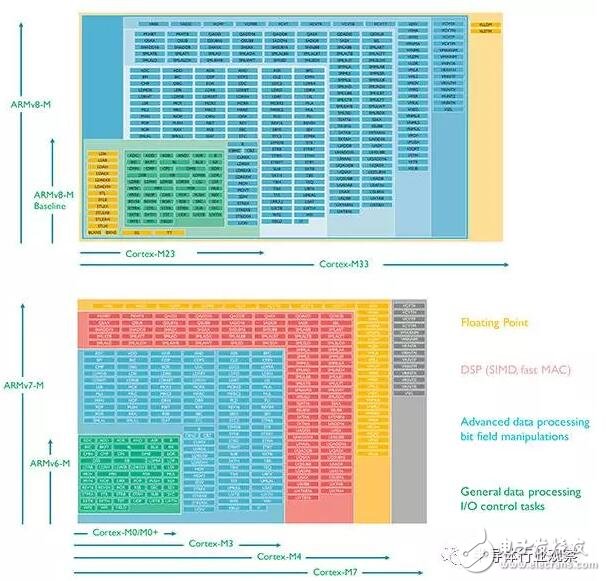

所有Cortex-M处理器都支援名为Thumb的指令集。在Thumb-2技术释出后,整个Thumb指令集就变得相当庞大。然而,不同Cortex-M处理器支援Thumb ISA里的指令子集合也不一致,如图1所示。

图1 各款Cortex-M处理器支援的指令集

Cortex-M0/M0+/M1处理器以ARMv6-M架构为基础,其指令集很小,只有56个指令,其中大多数为16位元,如图1中较小的椭圆形。不过,处理器中的暂存器以及处理的资料依然为32位元。对于大多数简单的I/O控制作业以及生成资料处理,这样的小指令集就已经足够应付。由于指令集很小,因此仅须用少量的逻辑闸就能建置处理器,像是Cortex-M0与Cortex-M0+处理器仅需1.2万个逻辑闸。不过,这些指令当中有一些不能用有高位暂存器(R8到R12),而且在即时生成资料方面的能力相当有限。这主要是为了在超低功耗处理器设计以及效能之间作折衷。

Cortex-M3处理器是以ARMv7-M架构为基础,并支援大上许多的指令集,当中有许多属于32位元指令,让系统能更有效率地运用高位暂存器。此外,它还支援向量表分支指令与条件执行(使用IT指令)、硬体除法指令、乘加(MAC)运算、可变位元栏位作业。

具更多指令集Cortex-M3效能大提升

更多的指令能透过几种方式提升效能。例如像32位元Thumb指令能提供较大范围的立即资料值、分支偏移、以及立即偏移以利资料记忆体的存取。另外,它还对DSP作业提供基本支援(像是几个MAC指令,须用几个时脉周期,另外还有饱和调整指令)。最后,32位元指令允许滚筒移位器和多个资料处理作业在同一个指令中操作。

然而,更大的指令集,代价就是矽元件面积与耗电都增加。在典型微控制器中,Cortex-M3的逻辑闸数量会比Cortex-M0或Cortex-M0+设计的逻辑闸多两倍以上。但由于在多数现代微控制器中处理器,只占一小部分的矽元件空间,因此较大的矽元件空间以及功耗产生的影响也变得微不足道。

Cortex-M4处理器在许多层面相当类似Cortex-M3,包括管线与程式开发模式。它除了支援Cortex-M3的所有功能,还额外支援DSP应用方面的指令,像是SIMD、饱和演算法指令、以及各种能在单周期完成的MAC指令(相对于Cortex-M3的多周期指令以及有限部分),选配的浮点运算单元能支援各种单精度浮点运算。

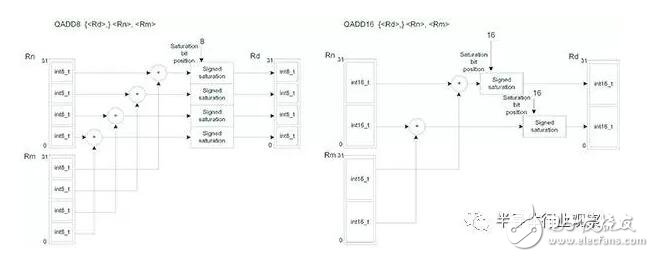

Cortex-M4的SIMD作业能同时处理两个16位元资料或4个8位元资料。举例来说,图2显示QADD8以及QADD16作业。

图2 SIMD指令范例:QADD8与QADD16

在某些DSP作业方面,由于计算能同时执行,因此,SIMD能让系统能更快运算16位元与8位元资料。然而,在一般程式开发方面,C语言编译器不太可能用到SIMD功能。这也导致Cortex-M3与Cortex-M4会产生大家常见的效能量测结果。然后,Cortex-M4的内部资料通道和Cortex-M3并不相同,Cortex-M3的通道在一些案例中支援更快的资料处理(像是单周期MAC,能在一个周期内将资料写回两个暂存器)。

Cortex-M7处理器的指令集支援类似Cortex-M4,另外还加入:

浮点运算架构方面,以FPv5为基础而不是FPv4 (Cortex-M4所采用),因此额外加入几个浮点运算指令。

选配双精度浮点运算指令。

支援预载资料(PLD)指令,让系统预先载入快取资料。

Cortex-M7的管线和Cortex-M4有极大差异。它拥有一个6阶双发送管线,发挥更高的效能。大多数针对Cortex-M4撰写的软体,都能在Cortex-M7重复使用,不过软体必须重新编译,才能针对管线特性的差异做最好的优化,在一些案例中,软体还需要一些微幅更新,才能利用像是快取在内的新功能。

Cortex-M23处理器的指令集以ARMv8-M基线sub-profile为基础,同时也是ARMv6-M的超集合。额外增加的指令包括硬体除法指令;比较与分支、以及32位元分支指令;TrustZone安全延伸的指令;互斥存取指令(通常用在旗标作业);16位元立即生成资料指令;Load acquire与store release指令(配合C11版C语言标准支援)。

在某些情况,这些指令集的加强有助于提升效能。另外,对于内含多个处理器的SoC设计也有助益(像是互斥存取在跨处理器的旗标传递相当有用)。

由于Cortex-M33的设计有极高的设定弹性,其中一些指令也属于选配,例如像是:

DSP指令(包括Cortex-M4与Cortex-M7处理器都有支援)都属于选配。

单精度浮点运算的支援能力属于选配。这项支援以FPv5为基础,比Cortex-M4浮点运算支援能力多了几项指令。

此外,Cortex-M33还支援ARMv8-M主线sub-profile,其中包括:

TrustZone安全延伸的指令。

Load Acquire与Store Release 指令(配合C11版C语言标准的支援能力)。

ISA功能比较总结

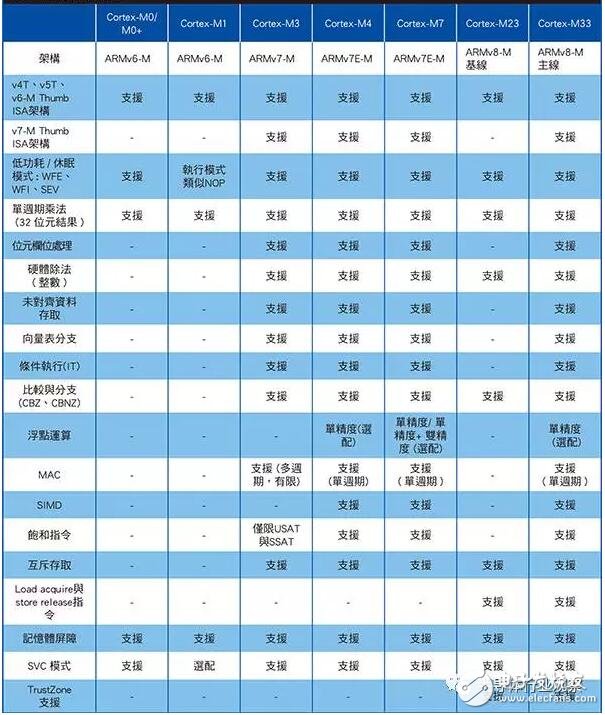

ARMv6-M、ARMv7-M、以及ARMv8-M架构具有为数众多的ISA特色,很难逐一详细介绍,所以在表3汇整其中关键的差异。

Cortex-M处理器中ISA其中一项关键特性就是向上相容性。Cortex-M处理器所支援的指令,系为Cortex-M0/M0+/M1的超集合(Superset)。因此,理论上如果记忆体地图相同,Cortex-M0/M0+/M1的二进位映像档就能直接在Cortex-M3上运行。Cortex-M4/M7和其他Cortex-M处理器之间也存在这样的相容性,Cortex-M0/M0+/M1/M3的指令能在Cortex-M4/M7上执行。

虽然Cortex-M0/M0+/M1/M3/M23处理器没有浮点运算单元选项,但可以用软体来执行浮点运算。另外,本身没有浮点运算单元的Cortex-M4/M7/M33也可用软体执行浮点运算。在这些处理器中,当使用程式处理浮点运算资料,编译程式在链结阶段会插入所需的执行阶段函式库函数。使用软体来执行浮点运算,除了运算时间变长,程式码长度也会略为增长。但如果没有频繁执行浮点运算,所开发的应用也适合采用这种类型的处理器。

-

最小化ARM Cortex-M CPU功耗的方法与技巧分享2026-01-21 131

-

Cortex-M产品的特色2025-11-26 201

-

Cortex-M位带操作的原理2023-10-24 1832

-

基于32位Arm Cortex-M内核N32系列MCU应用2023-03-28 1990

-

no cortex-m sw device found 问题解决【转】2021-12-02 3202

-

Cortex-M可以跑Linux操作系统吗?2021-12-01 925

-

如何选择正确的Cortex-M处理器?2020-10-22 2433

-

Cortex-M内核的MPU内存保护单元2020-03-04 4957

-

米尔科技Cortex-M Prototyping System +介绍2019-11-14 2815

-

关于Cortex-M 调试应用的介绍2018-07-10 3144

-

关于STM32与Cortex-M内核系列的介绍(2)2018-07-05 5528

-

Atmel Studio 6软件中如何调试ARM Cortex-M2018-07-04 4917

-

你总得知道你为什么要用Cortex-M2018-06-09 4047

-

ARM Cortex-M的音频性能解析2011-08-09 13295

全部0条评论

快来发表一下你的评论吧 !