硬件FPGA的资源划分及组成

嵌入式技术

描述

众所周知FPGA的硬件资源被划分为若干个不同的bank,Xilinx一些高端的FPGA器件由22个甚至更多个bank组成,这样设计主要是为了提高灵活性。FPGA的I/O支持1.8V、2.5V和3.3V等多种电平输入输出,为了获得这些I/O电平,就需要在对应bank的供电引脚输入对应的电源电压,这样就节省了很多总线转换器。

Flash是一种具有电可擦除的可编程ROM存储器,掉电内容不会丢失,按接口可以分为两大类:并行Flash和串行Flash,并行Flash存储量大,速度快;而串行Flash存储量相对较小,但体积小,连线简单,可减小电路面积,节约成本。SPI Flash是内嵌SPI总线接口的串行Flash,它比起传统的并行总线接口Flash,节省了很多的I/O口资源。

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存储器)也是FPGA设计中经常采用的内存器件,掉电后不能保存数据,功耗也比较大。因此Flash用于保存FPGA系统启动所需的配置文件,SDRAM则用于系统的数据的缓存,所有程序的运行都在内存中进行,速度快。

Xilinx Spartan-7 FPGA器件适用于那些成本敏感型应用。它采用小型封装却拥有高比例的I/O数量,单位功耗性价比相较前代产品提升多达四倍,可提供灵活的连接能力、接口桥接和辅助芯片等功能。

图1:Xilinx推出的成本敏感型的Spartan-7系列FPGA器件

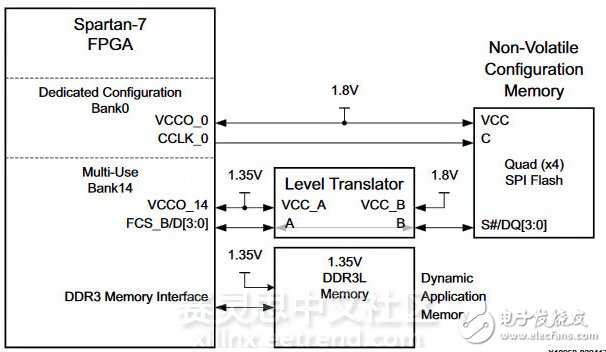

最小型的Spartan-7 FPGA只集成了100个I/O管脚,划分为两个bank,如果能够实现将QSPI Flash和DDR SDRAM都集成到同一bank那么就会充分利用有限的I/O资源。QSPI Flash的工作电压是1.8V,而DDR3L SDRAM的工作电压为1.35V,因此我们需要借助电压转换模块、MIG(Memory Interface Generator, 内存接口生成器)IP模块和Vivado工具的一些设置,专用I/O bank 0电压为1.8V,bank 14电压为1.35V,具体链接方式如下图所示:

图2:Spartan-7 FPGA同一bank连接1.8V SPI Flash和1.35V DDR3L

虽然这不是一个标准的解决方案,只是限于有限的I/O资源,但是对于小型系统设计不失为一种好的方法。具体设计细节如器件选型、原理图、确定时钟频率等要求请参看官方文档XAPP1313。

-

fpga是硬件还是软件2024-03-14 3798

-

FPGA资源与AISC对应关系2024-02-22 4964

-

DshanMCU-R128s2启动与资源划分2023-12-22 1991

-

【资料】FPGA硬件基础篇--理解FPGA时钟资源:PLL2021-03-30 1353

-

如何评估FPGA的资源2020-12-28 1251

-

FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载2020-12-10 968

-

星翼电子:开拓者FPGA开发板资源硬件描述2019-10-16 4546

-

浅析如何评估FPGA的资源2019-02-15 4414

-

Artix-7 FPGA中可用的专用硬件资源介绍2018-11-28 5434

-

硬件资源介绍2.1 核心板硬件资源2018-03-23 3129

-

FPGA中丰富的布线资源2017-12-05 1096

-

浅析FPGA芯片中丰富的布线资源2012-12-17 6317

-

支持过程级动态软硬件划分的RSoC设计与实现2010-05-28 1975

全部0条评论

快来发表一下你的评论吧 !