加法器电路原理图解_二进制加法器理解

电子常识

描述

在计数体制中,通常用的是十进制,它有0,1,2,3,…,9十个数码,用它们来组成一个数。但在数字电路中,为了把电路的两个状态(1态和0态)和数码对应起来,采用二进制较为方便,二进制只有0和1两个数码。

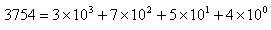

十进制是以10为底数的计数体制,例如

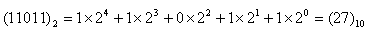

二进制是以2为底数的计数体制,例如

二进制数11011相当于十进制数27。

二进制加法器是数字电路的基本部件之一。二进制加法运算同逻辑加法运算的含义是不同的。前者是数的运算,而后者表示逻辑关系。二进制加法是“逢二进一”,即1+1=10,而逻辑加则为1+1=1。

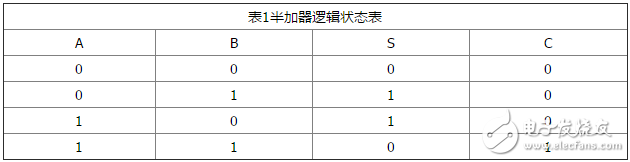

1、半加器

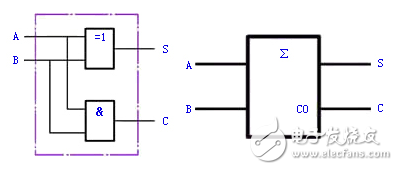

所谓“半加”,就是只求本位的和,暂不管低位送来的进位数。半加器的逻辑状态表见表1。

其中,A和B是相加的两个数,S是半加和数,C是进位数。

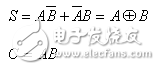

由逻辑状态表可写出逻辑式:

并由此画出图1(a)的逻辑图。图1(b)是半加器的逻辑符号。

(a)逻辑图(b)逻辑符号

图1半加器逻辑图及其逻辑符号

2、全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数 ,还有一个来自低位送来的进位数

,还有一个来自低位送来的进位数 。这三个数相加,得出本位和数(全加和数)

。这三个数相加,得出本位和数(全加和数) 和进位数

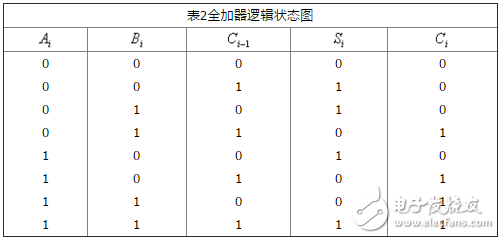

和进位数 ,这就是“全加”,表2是全加器的逻辑状态表

,这就是“全加”,表2是全加器的逻辑状态表

表2全加器逻辑状态图

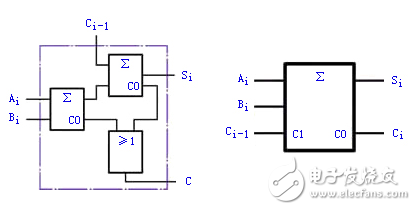

全加器可用两个半加器和一个或门组成,如图2(a)所示。 在第一个半加器中相加,得出的结果再和

在第一个半加器中相加,得出的结果再和 在第二个半加器中相加,即得出全加和

在第二个半加器中相加,即得出全加和 。两个半加器的进位数通过或门输出作为本位的进位数

。两个半加器的进位数通过或门输出作为本位的进位数 。图2(b)是全加器的逻辑符号。

。图2(b)是全加器的逻辑符号。

(a)逻辑图(b)逻辑符号

图2 全加器逻辑图及其逻辑符号

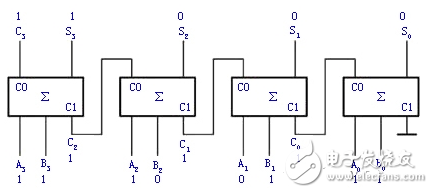

例1、用4个全加器组成一个逻辑电路以实现两个4位的二进制数A—1101(十进制为13)和B—1011(十进制为11)的加法运算。

解:

逻辑电路如图3所示,和数是S—11000(十进制数为24)。根据全加器的逻辑状态表自行分析。

这种全加器的任意一位的加法运算,都必须等到低位加法完成送来进位时才能进行。这种进位方式称为串行进位,它的缺点是运算速度慢,但其电路比较简单,因此在对运算速度要求不高的设备中,仍不失为一种可取的全加器。T692集成加法器就是这种串行加法器。

图3 例1的逻辑图

二进制加法器

一、多位二进制加法器

多位二进制加法电路种类很多,如四位并行输入串行进位加法电路,如图所示:

这种加法运算的速度是比较低的,在最不利的情况下,每做一次加法运算,需要经过4个全加器的传输延迟时间,才能得到稳定可靠的运算结果。

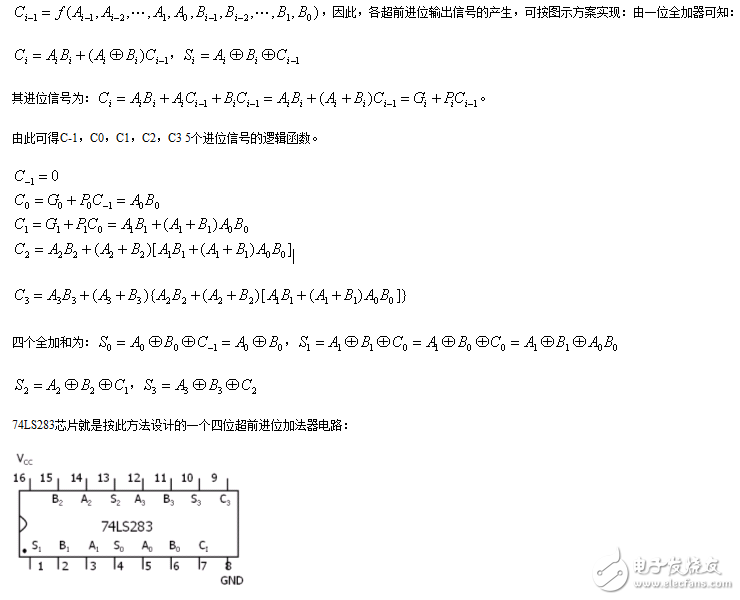

二、中规模集成超前进位加法器

为提高运算速度,必须设法减小或消除由于进位信号逐级传递所消耗的时间。那么高的进位输入信号能否在相加运算开始时就知道呢?因为第i位的进位输入信号 是两个加数中第i-1位以下各位数据的函数,即有:

是两个加数中第i-1位以下各位数据的函数,即有:

-

深圳冠荣

2017-09-25

0 回复 举报(支持)-深圳冠荣电子有限公司专业生产二极管 免费为您送样 网址:WWW.TVS-GR.COM QQ:1815215507 收起回复

深圳冠荣

2017-09-25

0 回复 举报(支持)-深圳冠荣电子有限公司专业生产二极管 免费为您送样 网址:WWW.TVS-GR.COM QQ:1815215507 收起回复

-

加法器的原理是什么 加法器有什么作用2024-05-23 7531

-

全加法器的工作原理和电路解析2023-06-29 15468

-

加法器的原理及采用加法器的原因2023-06-09 6351

-

什么是加法器?加法器的原理是什么 ?2021-03-11 5132

-

加法器工作原理_加法器逻辑电路图2021-02-18 34775

-

4位二进制并行加法器的程序和工程文件免费下载2020-09-30 1500

-

二进制加法器电路框图2019-06-22 28362

-

加法器原理2019-06-19 27366

-

加法器电路原理图解2018-10-11 4555

-

加法器电路原理_二进制加法器原理_与非门二进制加法器2017-08-16 23865

-

同相加法器电路原理与同相加法器计算2016-09-13 58834

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 14377

-

加法器,加法器是什么意思2010-03-08 5883

全部0条评论

快来发表一下你的评论吧 !