资料下载

×

电源噪声测量最佳解决方案

消耗积分:0 |

格式:rar |

大小:1.02 MB |

2017-08-29

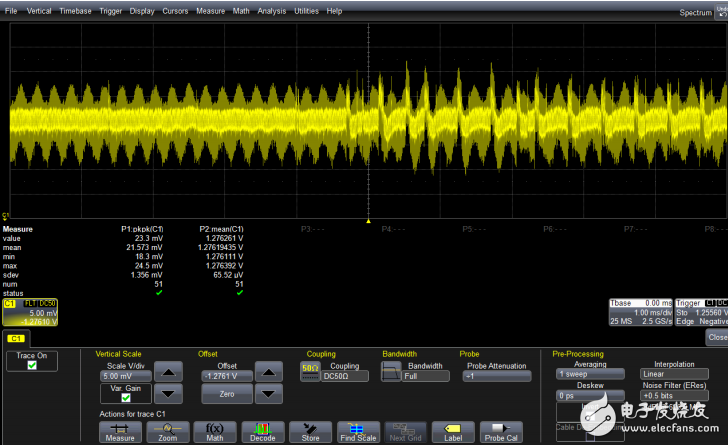

当今的计算机、PAD、手机、通信系统设备等电子产品,处理速度越来越快,运算能力越来越强,其电源的设计也越来越复杂。进入 21 世纪后,芯片的制作工艺由 0.18um 逐步升级到了 95nm、65nm、45nm,晶体管的集成度更高、主频更高、供电电压更低,这给产品的电路设计与调试带来了更大的挑战。在 90年代,芯片的供电通常是 5V 和 3.3V,使用 CMOS 或 TTL 电平,而现在,很多数字电路芯片的核心电压以及 IO 电平都小于 3.3V,以最常用的内存芯片为例,最古老的 SDR SDRAM 供电电压为 3.3V,DDR SDRAM为 2.5V,DDR2 为 1.8V,DDR3 为 1.5V,而最新的 DDR4 的供电电压为 1.2V,其 VREF 只有 0.6V。这些电路的供电电压越来越小,对电源噪声的要求也更加严格,如何设计低噪声的电源、并且准确测量其电源噪声非常关键,本文将从电源完整性(Power Integrity,简称 PI)的角度,简要分析电源噪声测试中可能遇到的问题和相应的解决方法。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章