Lint静态验证工具如何助力IC设计

描述

静态验证与“设计左移”

近年来IC设计的规模和复杂度不断增大,产品的迭代周期越来越短,传统的验证方式已经难以满足设计团队的要求。在“设计左移”这一理念的趋势下,设计流程和方法学不断进行创新和优化,其中,具备“设计左移”思想的静态验证方法实现了将原本在仿真、综合、布局布线阶段出现的问题移动到RTL阶段进行检测和分析,帮助IC设计者在早期发现和诊断设计缺陷,缩短芯片整体开发周期,降低成本。

不同于其他验证方式,静态验证是通过分析设计的源代码来发现设计中的错误。静态验证是对硬件设计经验的总结提炼, 是硬件设计的知识库 ,硬件设计知识涵盖了语法分析、可综合性分析、时序优化技术、功耗优化技术、面积优化技术、可测性分析技术、跨时钟分析技术等许多方面。

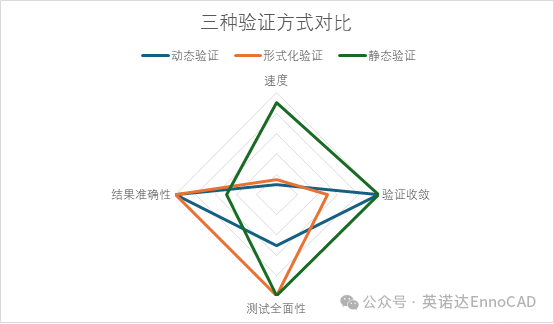

静态验证是IC设计验证方法之一,是确保高质量设计输出的关键步骤。相比需要激励进行仿真的动态验证(如软件仿真、硬件仿真加速)与形式化验证(如等价验证、模型检测)手段,静态验证(如STA、Lint、CDC等)可以在成本、速度、覆盖率等方面弥补传统验证手段的不足。

Lint静态验证工具

Lint工具是一款代码检测工具,也是最常见的静态验证工具之一。通常设计团队在编写Verilog等代码时,会犯一些无意识的代码错误,或产生一些虽语法正确但后期可能有隐患的代码。对于这些问题,设计团队要在第一时间解决,否则将直接导致编译或运行错误,影响开发效率和质量。

Lint本义是指除掉织物上的毛线和短绒,后来引申到计算机领域,这个概念最早源于1979年贝尔实验室开发的针对C语言的Lint程序,它能够进行更深入的检查错误,找出编译器可能忽略的潜在问题。

在芯片设计中,Lint工具可在RTL阶段对HDL代码的naming、coding style、structure、综合以及仿真mismatch等问题进行检查。Lint分析节约整体流程时间提升开发效率主要体现在3方面:

在RTL编码阶段即可进行验证,无需等待验证环境的搭建;

运行速度快;

直接从根因发现问题。

比如电路中的管脚的悬空输入(floating input),往往会造成功耗损失,增加电路噪声,更致命的是功能上的错误。这些错误如果在逻辑综合或后仿真阶段才被检查出来,需要耗费大量的时间和精力溯源并修改相关的RTL代码。如果一个人为的疏忽,直到芯片流片后都没有发现,那么芯片流片后回来可能会变成产品功能缺失。而避免这样的错误也很容易,在RTL设计阶段使用Lint工具找到该问题并修改floating input就可以了。

作为一款静态验证工具,Lint非但不会对工程师现有的设计流程造成任何阻碍,反而能够优化现有的流程,通过在早期发现设计错误并改善代码质量,Lint可以帮助工程师更快地理解和解决复杂设计中的问题,实现效率与质量的双重提升。

关于英诺达

英诺达(成都)电子科技有限公司是一家由行业顶尖资深人士创立的本土EDA企业,公司坚持以客户需求为导向,帮助客户实现价值最大化,为中国半导体产业提供卓越的EDA解决方案。公司的长期目标是通过EDA工具的研发和上云实践,参与国产EDA完整工具链布局并探索适合中国国情的工业软件上云的路径与模式,赋能半导体产业高质量发展。英诺达首款自主研发的EnFortius®凝锋®系列低功耗EDA工具,可有效帮助IC设计工程师定位并分析低功耗设计相关问题。在静态验证领域,EnAltius®昂屹®系列工具将在设计流程的早期增强可预测性,帮助IC设计工程师做出最优决策。英诺达的EnCitius®曜奇® SVS系统验证平台则利用EDA上云的优势,为客户打通验证资源的渠道,提供全面的SoC及系统级验证的一站式解决方案,提高芯片设计效率。此外,英诺达还可提供完整、可定制的前/后端设计服务。

-

C语言——代码检查工具2017-04-20 9318

-

ASIC静态验证方法2011-06-21 1026

-

zpwsmile朗讯设备选择HDAC进行静态功能验证2020-02-07 1578

-

关于PC-lint,以及如何在MDK中添加PC-lint工具2020-03-04 5908

-

IC验证的主要工作流程和验证工具是什么?2023-05-31 3072

-

ic验证是做什么的 ic验证用什么语言2023-07-24 6545

-

如何在SpyGlass环境本身中修复这些Lint错误呢?2023-08-14 6235

-

ic验证是封装与测试么?2023-08-24 1951

-

英诺达发布DFT静态验证工具2023-09-13 2576

-

英诺达静态验证EDA工具可确保设计在可测试性部分达到交付标准2023-09-23 2110

-

分享一款不错的嵌入式静态代码扫描工具2023-10-16 5719

-

SpyGlass®Lint Turbo结构用户指南2023-12-21 625

-

英诺达推出两款全新静态验证EDA工具2024-12-05 1935

-

英诺达发布全新静态验证产品,提升芯片设计效率2024-12-24 1457

-

华大九天物理验证EDA工具Empyrean Argus助力芯片设计2025-07-03 3770

全部0条评论

快来发表一下你的评论吧 !