PCIe3.0 Tx发射一致性测试

描述

PCIe 3.0发射一致性测试是确保数据传输稳定性和可靠性的重要环节,本文将为大家详细介绍该测试的流程和要点。

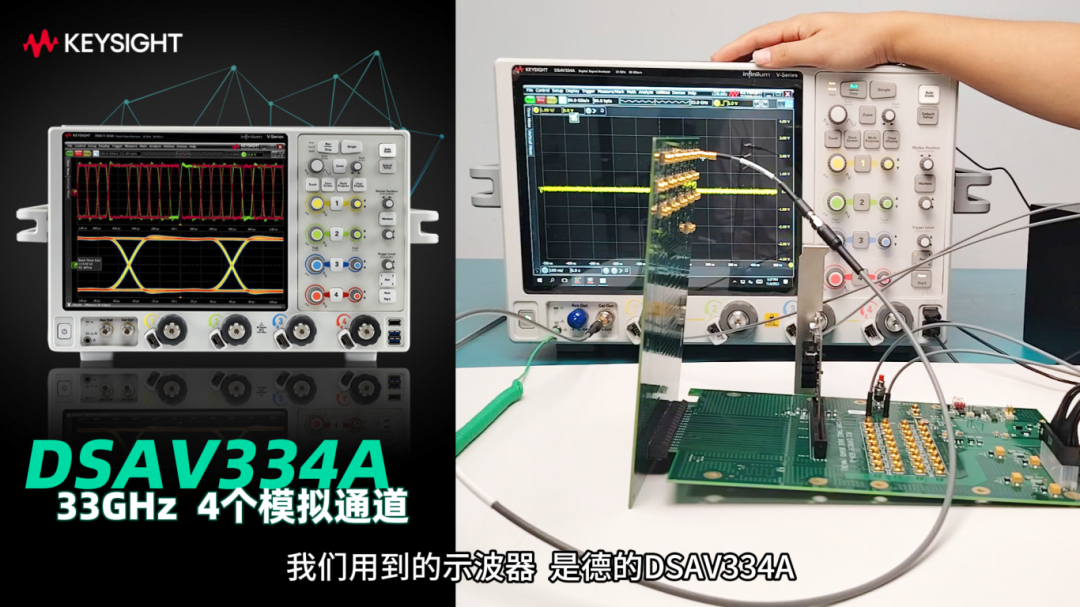

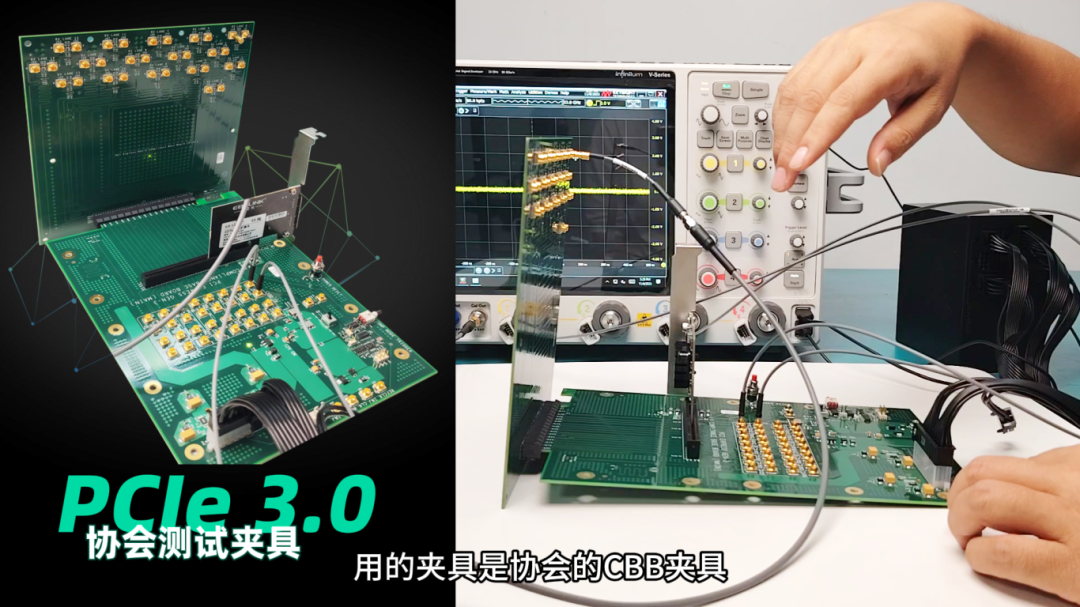

Chrent设备介绍

示波器:是德DSAV334A,33G。

夹具:协会的CBB夹具,分两部分:一部分是CBB板,另一部分是CBB的Riser板

Chrent系统连接

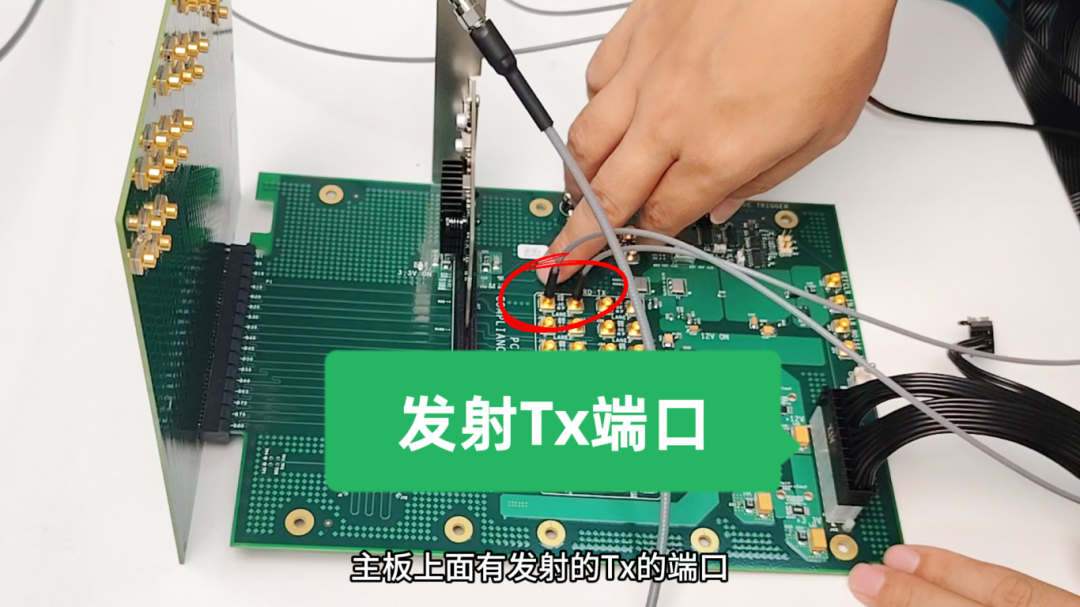

我们来看一下整个系统连接。首先把夹具的CBB主板和Riser板连接在一起,主板上面有发射的Tx端口,Riser板上是接收的Rx端口。

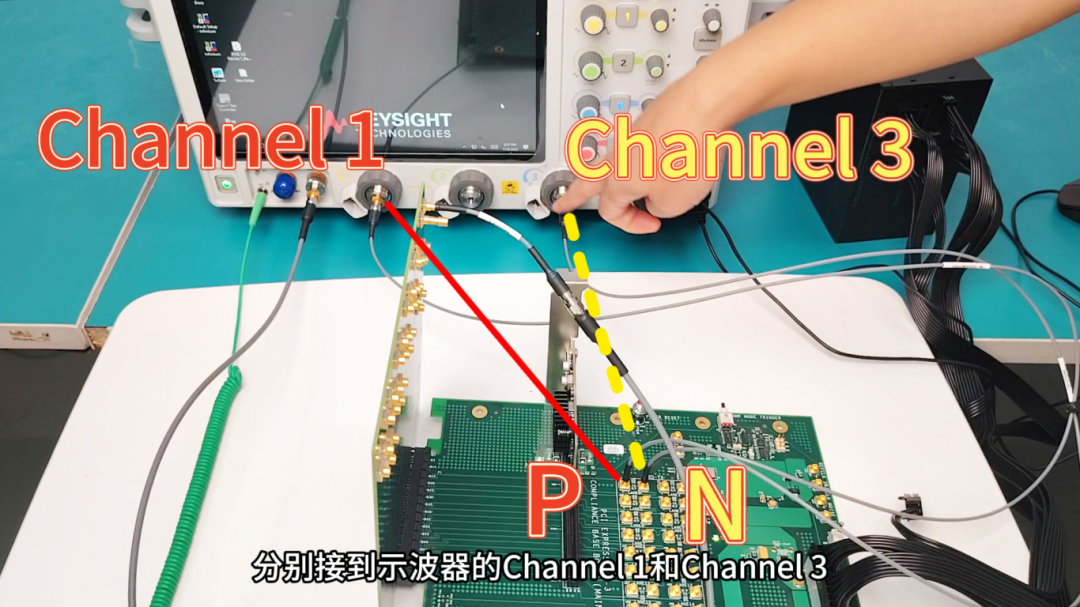

我们把发射Tx的Lane 0的P和N,接到示波器上:P接Channel 1,N接Channel 3。

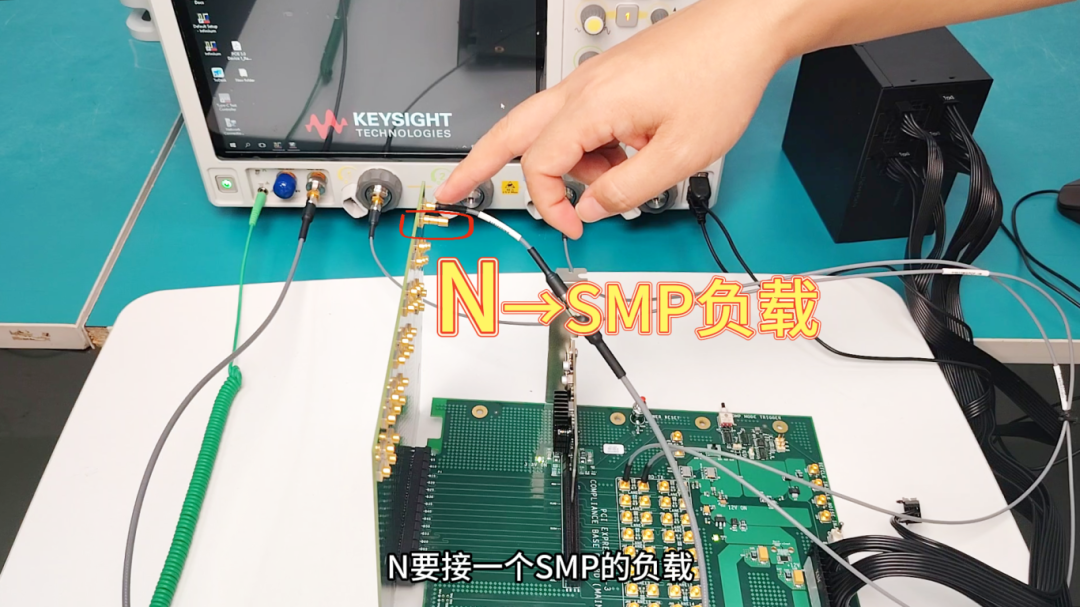

因为我们不是通过夹具来手动Toggle码型,而是通过示波器的Cal Out端口自动Toggle,所以把Riser板接收Lane 0的P和N:P通过射频线接到示波器的Cal Out端口上面,N接一个SMP的负载。

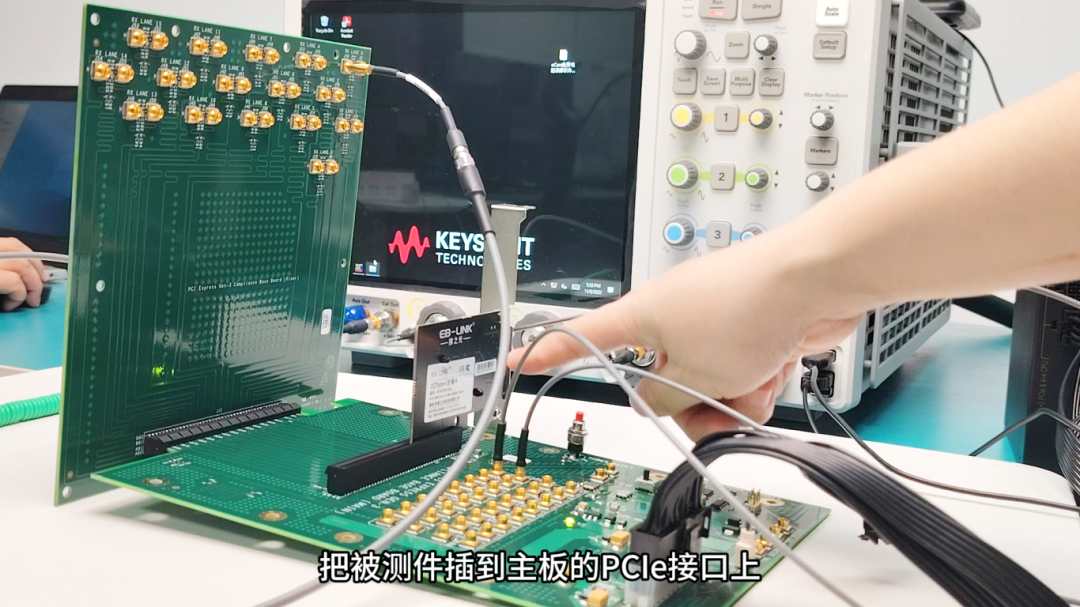

整个系统射频的连接就接好了。再把被测件插到主板的PCIe接口上,这是一个X4的被测件,最后把电源接到CBB板上。

Chrent测试流程

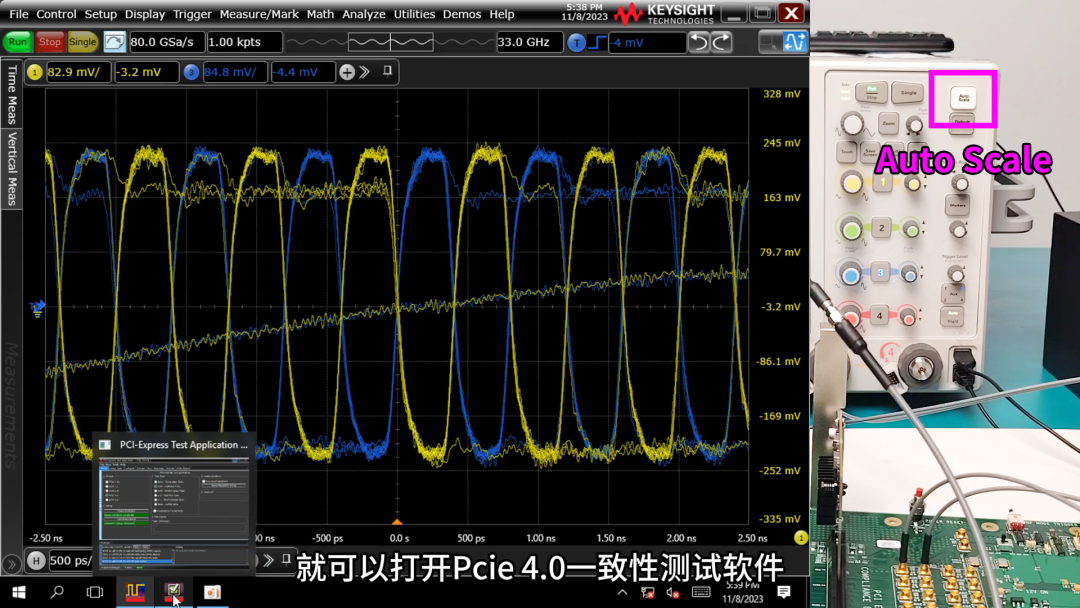

打开夹具上的电源。可以看到示波器上已经有Toggle码型了,这时候我们可以Auto Scale看一下这个码型。

在示波器上能看到码型以后,就可以打开PCIe 4.0一致性测试软件,软件是向下兼容的。

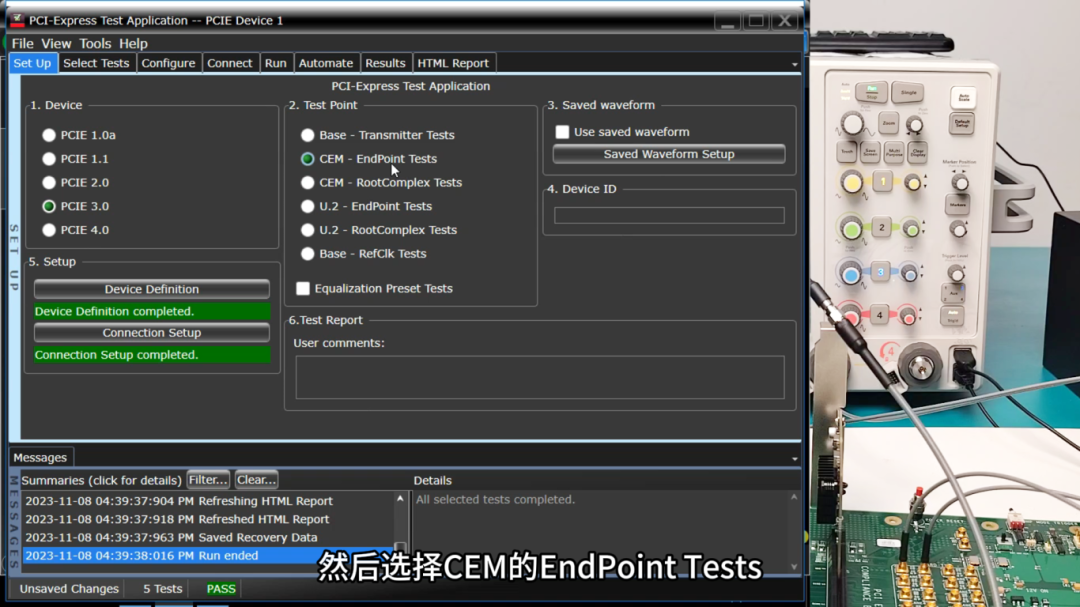

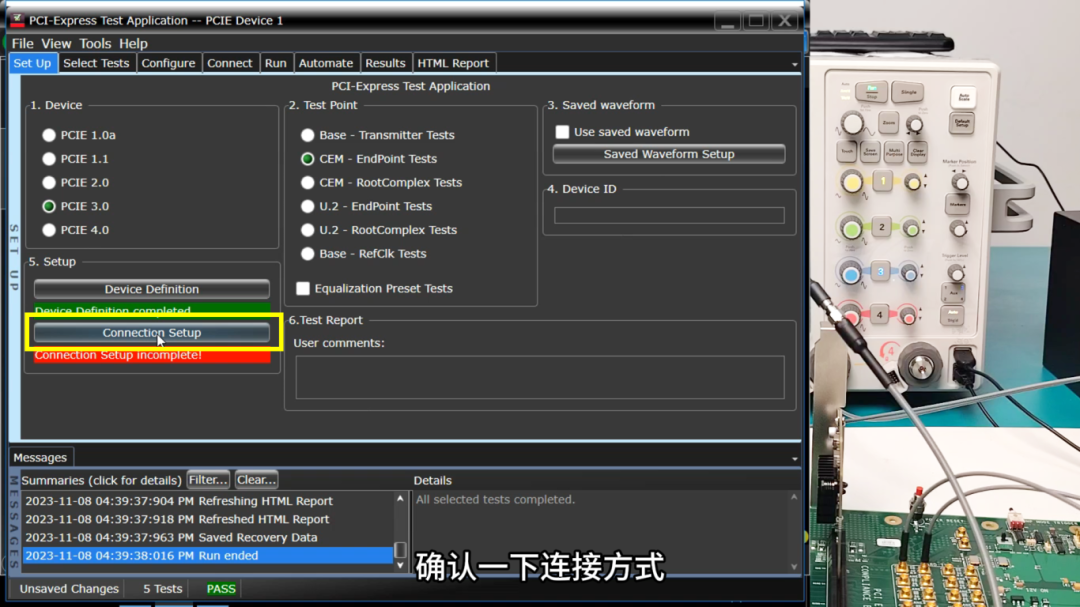

第一项Set Up里我们选择PCIe 3.0,再选择CEM-EndPoint Tests,这个是Add-in Card的测试。

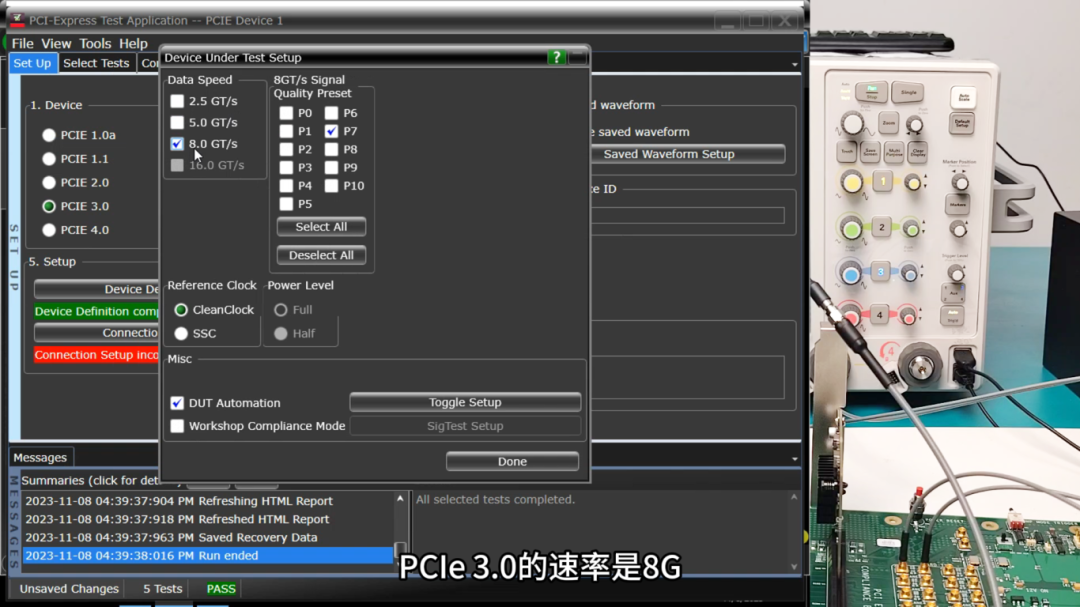

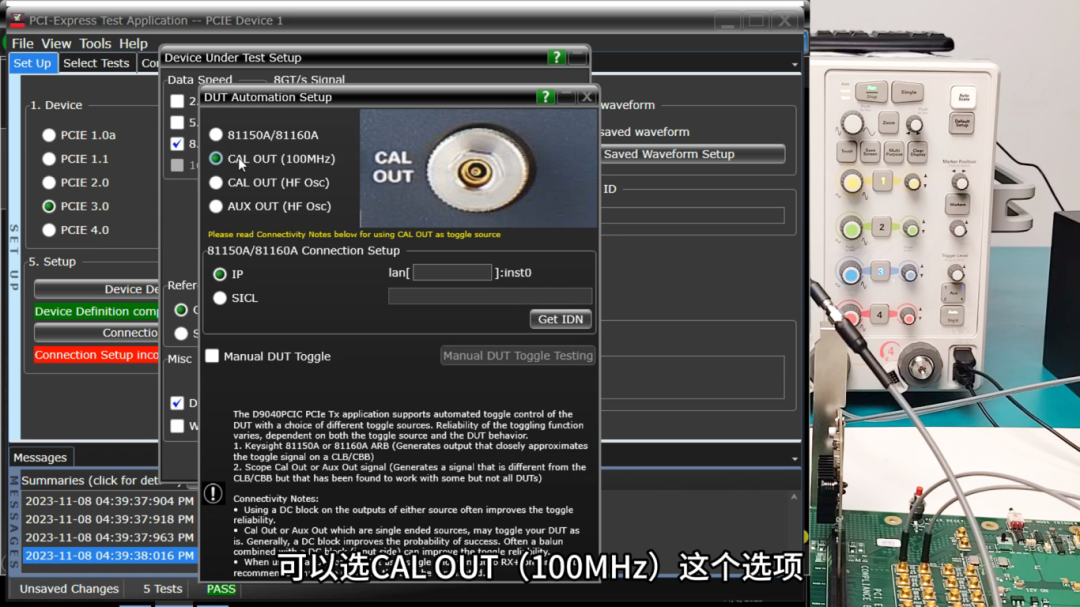

在Device设置里面选择速率,PCIe 3.0的速率是8G,Preset选择P7,勾选DUT Automation(自动Toggle码型)。点击Toggle Setup,选择CAL OUT(100MHz),关闭这个小窗口后,点击Done。

点击Connection Setup,确认一下连接方式。

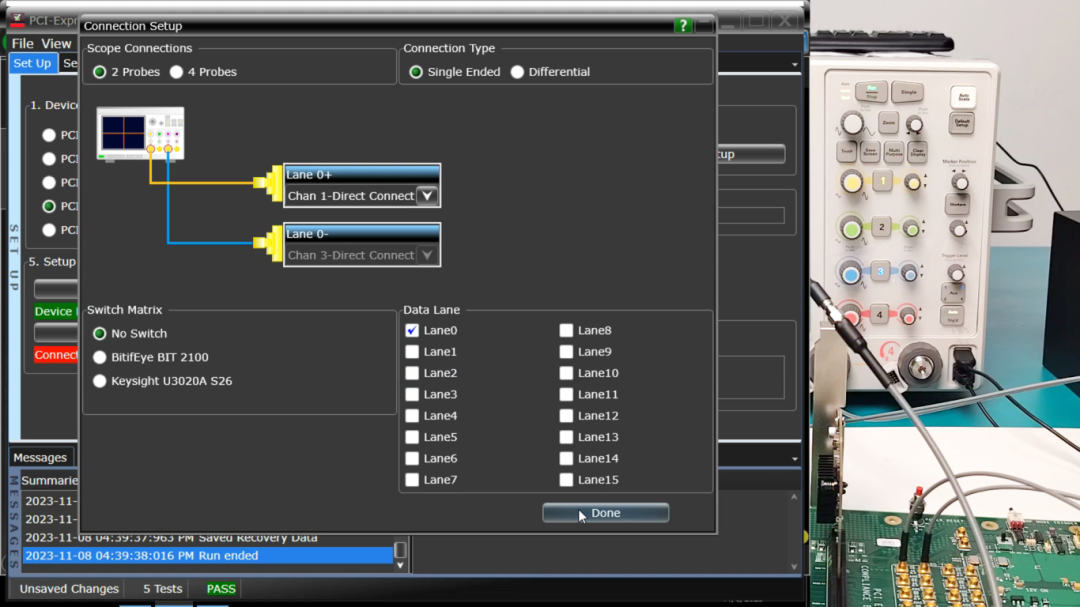

我们是用单端的方式,两条射频线接到Channel 1和Channel 3,没有用开关,选择测试Lane 0。

Set Up的界面就设置完成。

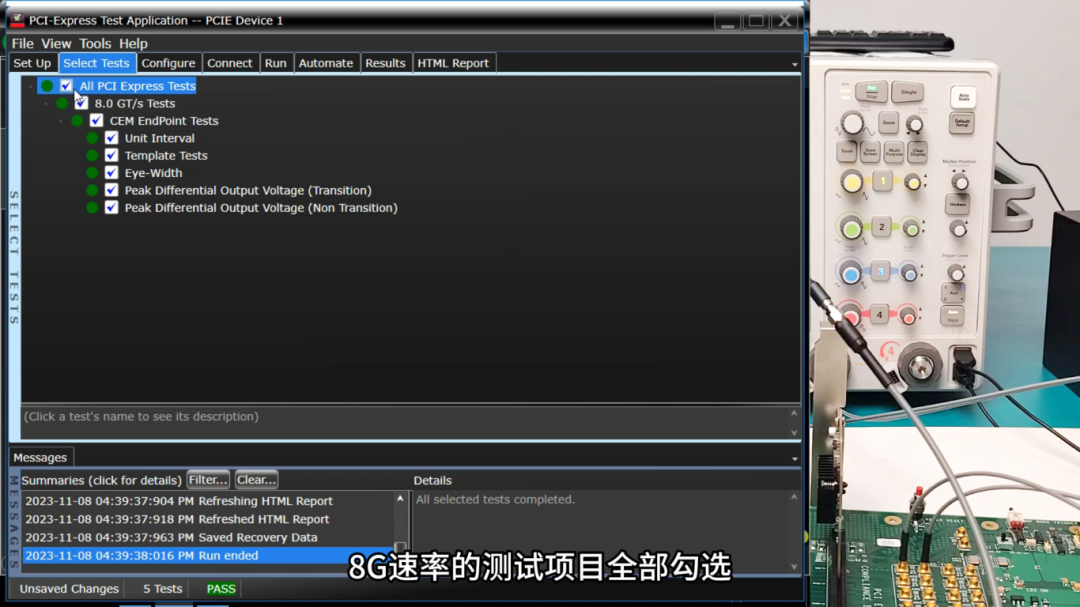

第二项Select,8G速率的测试项目全部勾选。

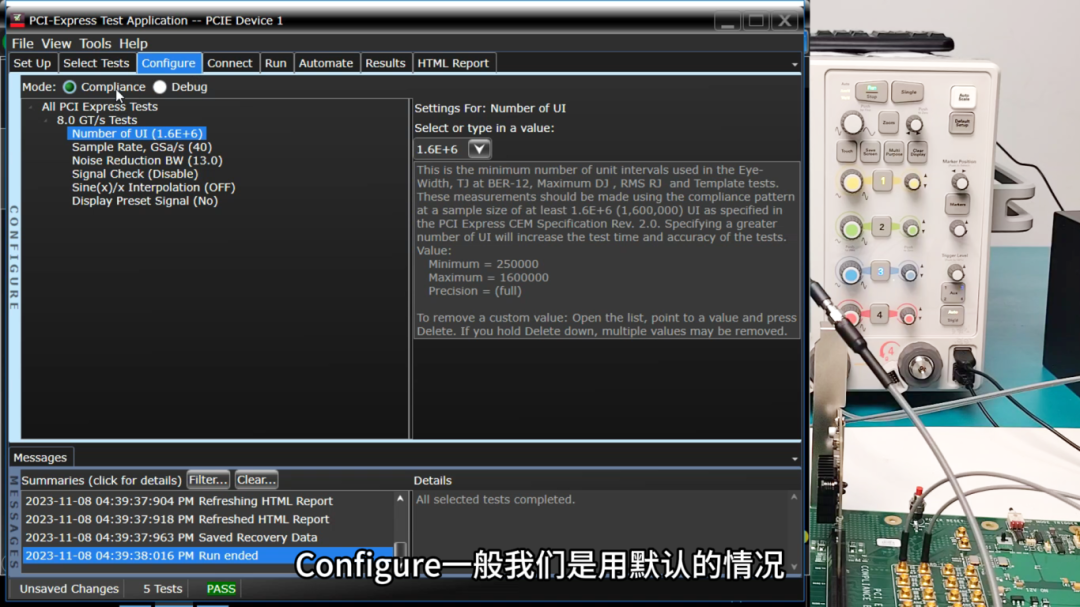

第三项Configure一般默认。

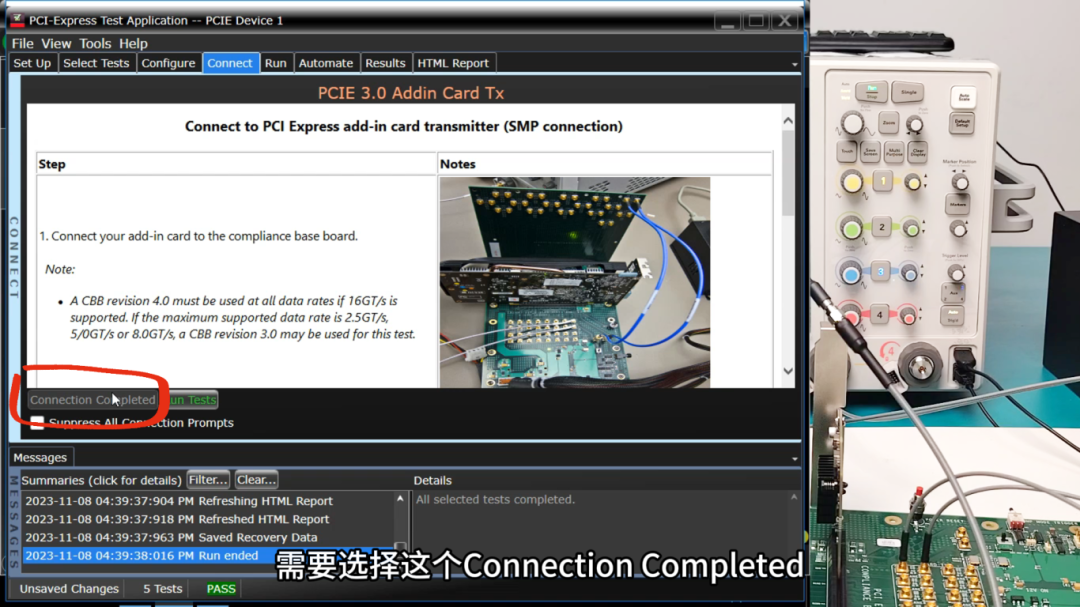

第四项Connect,选Connection Completed。

图中是手动Toggle的方式,需要把CBB上的G5、G85,分别接到Rx的Lane 0的P和N,我们是用示波器自动Toggle的方式,只需要把Cal Out端口接到P端口。

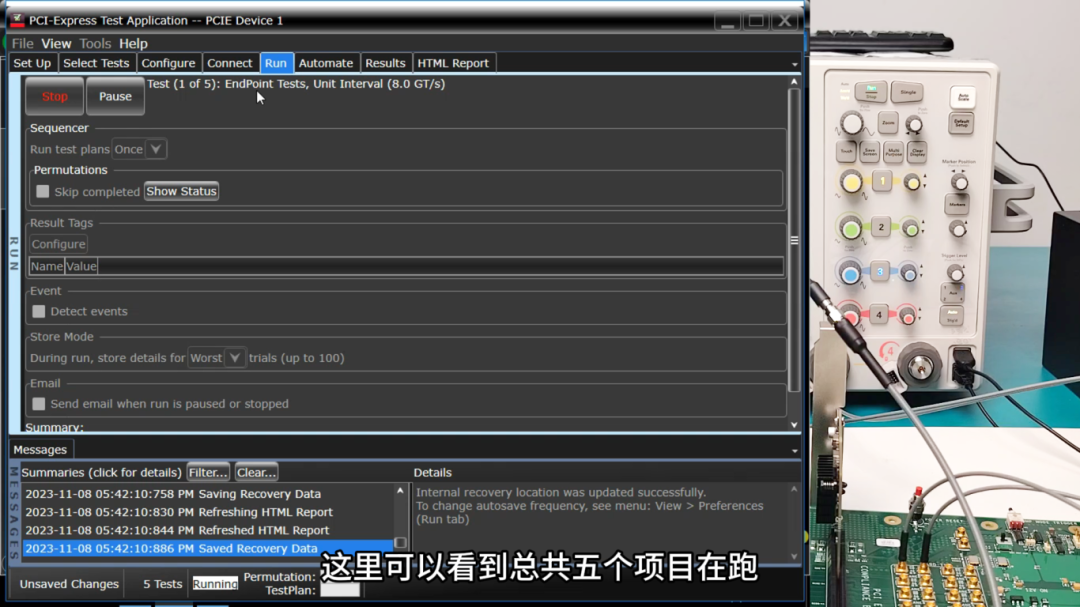

点击Run Tests。

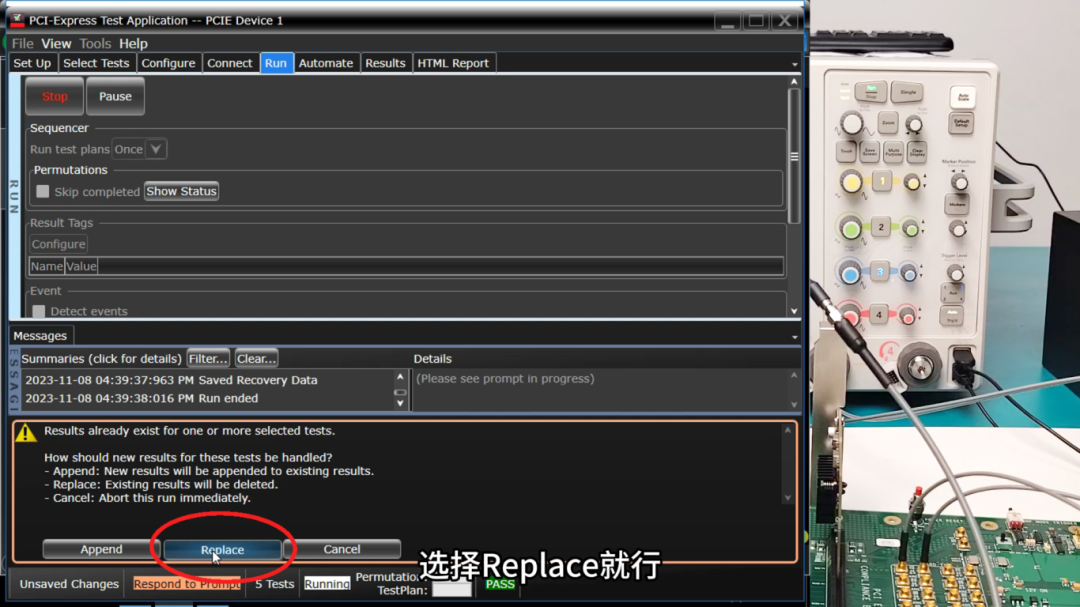

第五项Run,因为我之前跑过一遍,所以再跑一遍不需要做什么操作,选择Replace就行。

这里可以看到总共五个项目在跑。

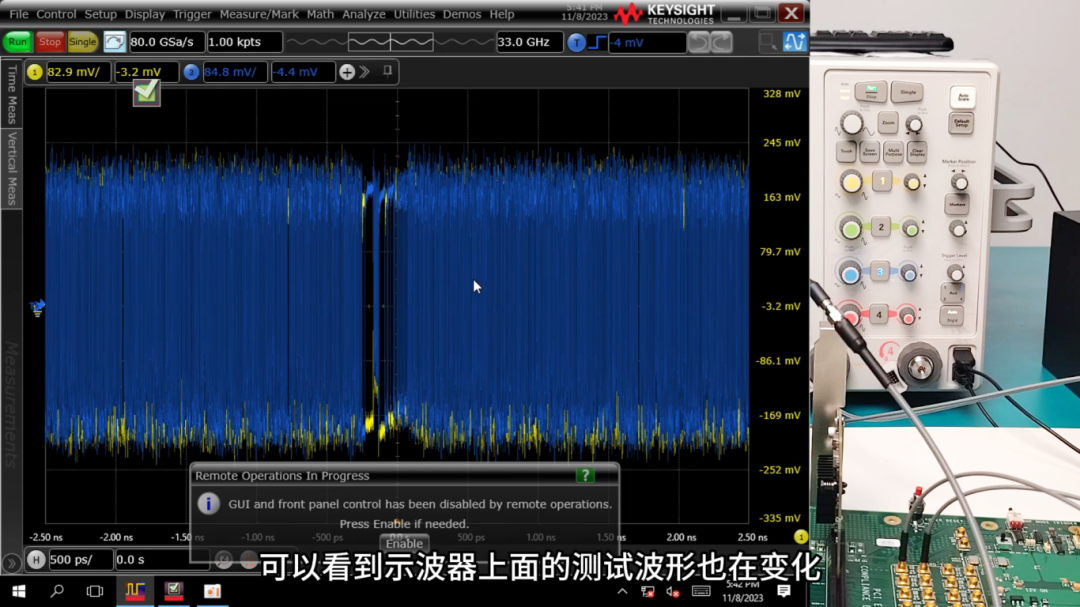

把这个最小化,可以看到示波器上面的测试波形也在变化。点击Enable退出界面。

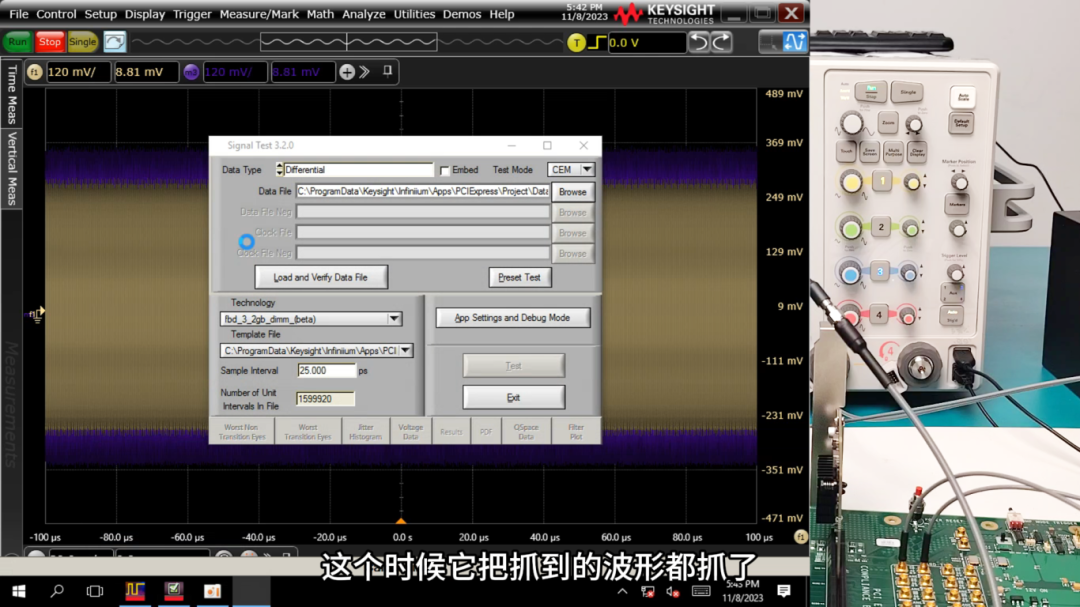

这是它抓到的波形,然后调用SIGTEST软件来分析测试结果。

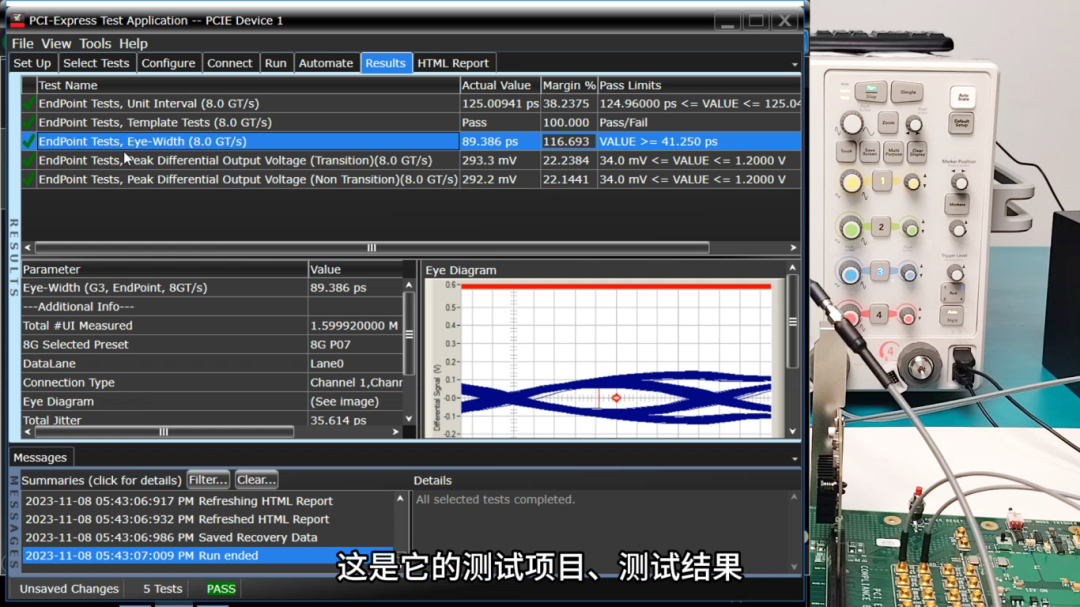

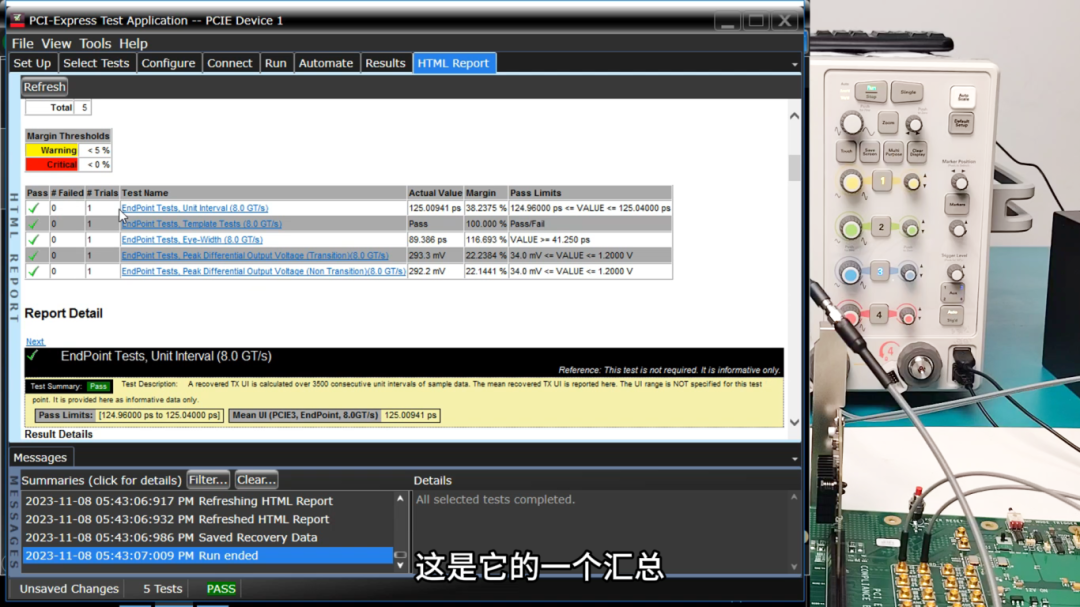

第七项Results看测试项目和结果,测试结果是PASS。

最后一项看测试报告,下拉是各个项目的详细测试结果。

PCIe 3.0发射一致性测试就简单介绍到这里,大家如果还有更多的测试测量方面的问题,可以后台留言。

-

LIN一致性测试规范2.12024-08-15 881

-

DDR一致性测试的操作步骤2024-02-01 4295

-

如何进行千兆以太网的一致性测试2023-07-07 2457

-

PCIE一致性测试过程的详细介绍2022-02-14 20082

-

泰克示波器在USB3.0一致性测试的应用2021-06-23 2126

-

USB3.0物理层一致性测试挑战是什么?2021-05-08 2097

-

MIPI一致性测试2019-09-26 3630

-

LTE基站一致性测试的类别2019-06-06 1960

-

EMI一致性测试调试方法2017-09-12 1054

-

一致性测试2017-07-14 3584

-

TD-LTE终端一致性测试标准化技术规范2013-01-09 5467

-

泰克公司推出全自动Thunderbolt发射端一致性测试解决方案2012-07-03 1530

-

RFID协议一致性测试系统设计(二)2012-03-28 2060

-

PCIe 2.0/PCIe 3.0验证、调试和一致性测试解决2010-06-29 1259

全部0条评论

快来发表一下你的评论吧 !