国产RFSoC 47DR/28DR/27DR核心板

电子说

描述

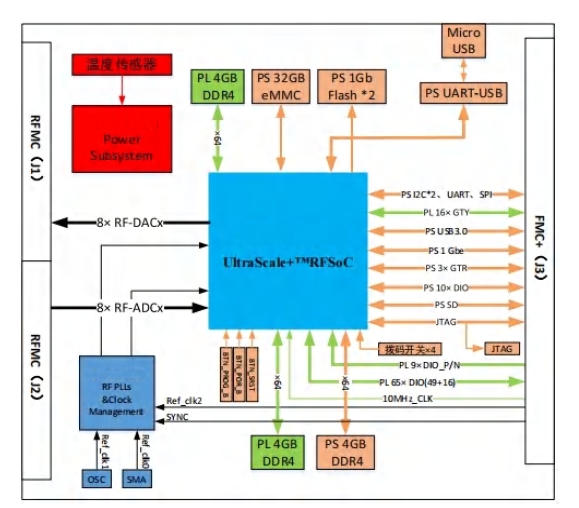

采用FDW复旦微电子FMZQ28DR- RFSoC处理器,兼容Gen1 ZU28/27、Gen3 ZU48/47DR RFSoC,拥有8个RF-ADC、8个RF-DAC通道。提供完整的应用示例源代码和性能分析工具, 主要用于小尺寸、低功耗、实时处理RF系统的快速集成与应用部署,缩短产品开发周期。

主要技术指标:

核心处理器:Gen3 ZU48(47)DR- 2FSVG1517I RFSoC

8xADCs, 14-bit up to 5GSPS;

8x SD-FEC硬核(47无此硬核)8

x DACs, 14-bit up to 9.85GSPS;

RF Input Freq. Max:6GHz;

Quad-core Arm Cortex-A53 MPCore with CoreSight;

Dual-core Arm Cortex-R5F with CoreSight;

PS I/O:支持UART,CAN2.0B,USB2.0,I2C,GigeE10/100/1000,SDIO,SPI 协议;

4x PS-GTR:支持PCIe Gen1/2、Serial ATA 3.1、DisplayPort 1.2a、USB 3.0 和 SGMII 协议;

16x PL-GTY:PCIe Gen4、100G Ethernet、150G Interlaken 等协议;

72x PL-GPIO:用户自定义 IO;

调试接口:JTAG、usb2UART、PMBus;

适配 Gen1 ZU28(27)DR RFSoC 芯片时,变化参数如下:

8x ADCs, 12-bit up to 4.096GSPS

8x DACs, 14-bit up to 6.554GSPS

RF Input Freq. Max:4GHz

8x SD-FEC 硬核(27无此硬核)

16x PL-GTY:支持PCIe Gen3、100G Ethernet、150G Interlaken 等协议

板载存储:

2 组 4GB 64bit DDR4 @ Programmable Logic

32GB eMMC Persistent Storage

4GB 64bit DDR4 @ Processor Subsystem

1Gb QSPI Boot Storage

独立时钟管理网络

超低抖动可编程时钟网络:外部或板载参考 100MHz(可更换)可选;

支持板间时钟同步;

33.33MHz@PS、200MHz@PL 独立工作时钟;

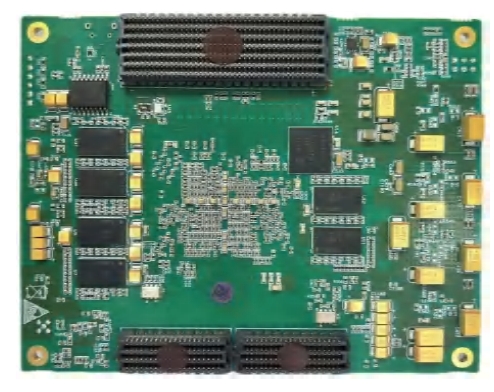

机械结构与供电

12V 供电,过压、过流、超温监测与管理;

机械尺寸:127.0mm * 101.6mm(老款),77.1mm*101.6mm(新款);

信号接口:2xRFMC,FMC+

配套明细

参考例程:ADC/DAC 例程;PL 例程;PS 例程;OS 镜像;时钟管理例程;

RF Analyzer(ADC 性能评估软件);

PCIE 规范标准测试用底板(选配)

应用领域

相控阵雷达

5G大规模MIMO

混合波束成形

卫星通信

空间信号检测与干扰

多通道射频仪表

宽域频谱监测与射电天文

审核编辑 黄宇

-

jf_88141582

2025-04-01

0 回复 举报非常不错,可与UD PCIe-403协同使用 收起回复

jf_88141582

2025-04-01

0 回复 举报非常不错,可与UD PCIe-403协同使用 收起回复

-

创龙科技DR1M90工业评估板的关键优势2025-08-18 1669

-

米尔国产FPGA SoC芯选择,安路飞龙DR1M90核心板重磅发布2025-01-10 2763

-

基于RFSOC 27或47DR 8路ADC + 8路DA 6U VPX板卡2024-10-10 2460

-

如何利用PCIE在d2000开发平台和28dr上进行数据交互?2024-02-27 8544

-

Xilinx ZYNQ UltraScale+RFSoCZU27DR 开源RFSOC算法验证评估板2023-08-25 2159

-

XilinxZYNQUltraScale+RFSoCZU27DR开源RFSOC算法-ZXB-27DR-8T8R验证评估板2023-06-12 3443

-

RTKA223012DR0010BU、RTKA223012DR0020BU演示板说明书2023-01-30 416

-

与静态DR相比,动态DR有哪些优势?2022-08-03 3299

-

U臂DR是什么,动态U臂DR的优势特点是什么2022-04-21 2516

-

动态DR是什么,动态DR临床应用优势的解析2021-12-08 4017

-

移动DR相比其他类型DR 它具备哪些优势2021-11-17 1914

-

移动DR的用途及特点2021-07-09 7306

-

动态DR是什么,有哪些应用2021-06-24 4622

-

悬吊DR的优势介绍2021-05-10 3767

全部0条评论

快来发表一下你的评论吧 !