资料下载

×

CMOS光电二极管有源像素传感器研究

消耗积分:0 |

格式:rar |

大小:0.17 MB |

2017-09-01

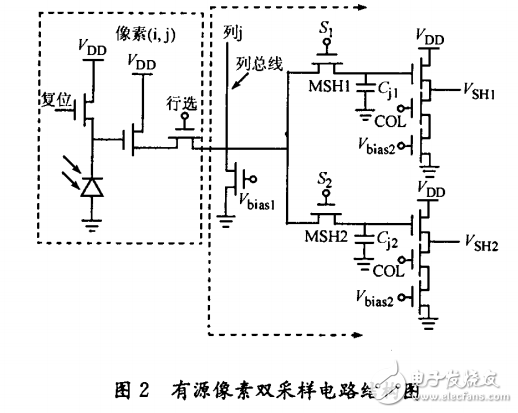

双采样技术使用图2所示的结构实现,每列共用两个采样保持(S&H),两个NMOS缓冲放大器,和一个全差分放大器(如果帧频要求较低,整个芯片可以采用一个全差分放大器)。像素工作时序如图3所示。当某一行被选中时,该行中每个像素的输出被采样并且保持到S&H电路(每列包含两个)中。然后该行复位,每个像素的输出被采样保持到另外一个S&H电路中。当读信号到来时,(COL变为高),信号输出和复位输出同时被读出到差分放大器,这样就可以消除失调FPN以及列FPN。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章