瀚海微SD NAND存储功能描述(22)Timing Values

电子说

描述

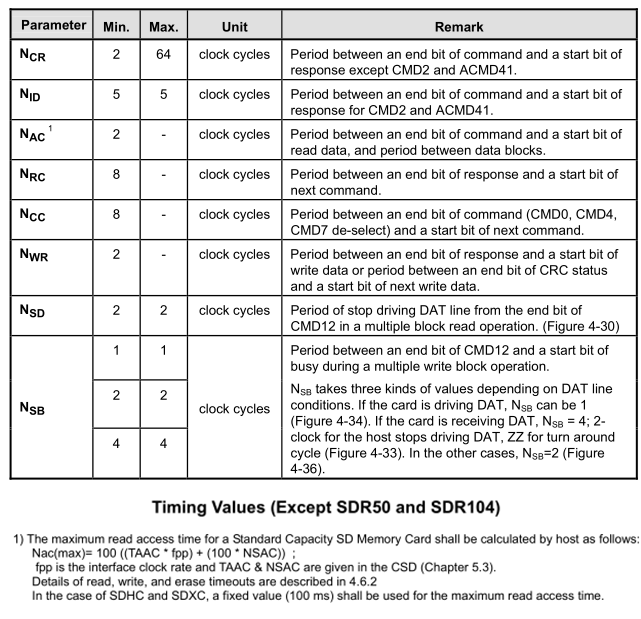

Timing Values

块读取Gap

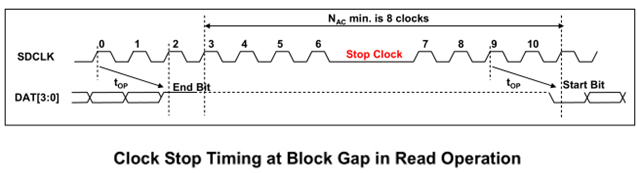

在读取操作过程中,由于主机缓冲区已满,主机需要通过停止SDCLK来停止从卡中读取数据的输出。考虑到使用采样时钟调优方法,主机需要在块间隙停止SDCLK,而不是在数据传输过程中停止SDCLK。

由于数据的变化,DAT[3:0]应该被认为是与SDCLK异步的。因此,通过检测数据块的结束位来停止SDCLK需要很少的时钟,因为需要同步。最小块间隙时钟(Nac)定义为8,以便主机可以在卡开始输出下一个数据块之前停止SDcLK。

下图给出了在块间隙处停止SDCLK的时序示例。它显示了top大于1UI的情况。时钟位置0是触发点,输出数据块的结束位。cardl开始通过SDCLK从时钟位置0开始计算内部计数器。SDCLK上面显示的数字就是这个计数器的值。卡至少要等到时钟9才能输出下一个数据块。l然后主机需要在时钟9之前停止SDCLK。NAc(min.)=8提供了足够的时间来停止SDCLK。

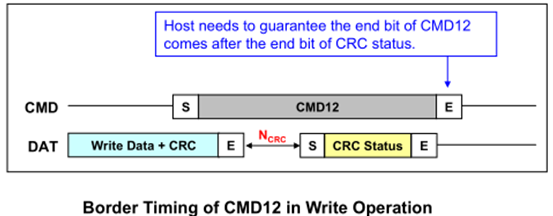

CMD12写操作定时

修改由于从卡到主机的输出延迟可能超过1个时钟,因此需要更改CMD和Data之间的关系。适用于写操作中CMD12与CRC Status的关系。珍贵写块写入成功的边界时序如下图所示。主机接收到CRC Status结束位后,需要输出CMD12结束位。如果CMD12发布时间早于下图,则数据块是否写入不确定。将CMD12的结束位调整为CRC状态需要特定的硬件。主机可以采用另一种方法停止多块写操作,如在接收到最后一个数据块的CRC状态后发出CMD12。

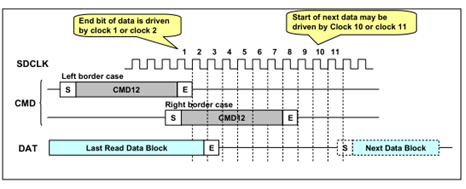

CMD12读操作定时

修改读操作边界计时如下图所示。最小块间隙长度Nac为8时钟。CMD12在时钟1(数据块结束位之前2个时钟)的结束位位于左侧边框,使卡能够成功输出最后一次读取的数据块。如果在此时间之前发出CMD12,则读取的数据块可能会被销毁(例如,未指示数据块的结束位)。

时钟8时CMD12的结束位是右侧边界,不输出下一个数据块,这意味着CMD12的结束至少在下一个块的开始位之前3个时钟。如果在此时间之后发出CMD12,则可能输出next数据的一部分。调整CMD12的结束位来读取数据块需要特定的硬件。

主机可以采用另一种方法停止多块读取操作,如在接收到最后一个数据块后发出CMD12。通过这种方法,下一个数据块可以开始输出并被CMD12终止。最后读取的块表示超出范围错误。

审核编辑 黄宇

-

国产安路FPGA SD NAND FLASH 初步描述2024-10-16 1388

-

瀚海微SD NAND应用之SD协议存储功能描述2 初始化命令2024-07-22 1297

-

瀚海微SD NAND存储功能描述(9)切换功能2024-08-09 786

-

瀚海微SD NAND存储功能描述(11)命令系统CMD82024-08-12 1285

-

瀚海微SD NAND存储功能描述(14)命令类a2024-08-19 871

-

瀚海微SD NAND存储功能描述(18)命令类e2024-08-26 1040

-

瀚海微SD NAND存储功能描述(25)SD Registers2024-09-14 1026

-

瀚海微SD NAND存储功能描述(26)CSD Registers2024-09-18 1698

-

瀚海微SD NAND存储功能描述(28)RCA Registers2024-09-23 1011

-

瀚海微SD NAND/TF卡——数据世界的全能搭档2025-10-13 571

-

瀚海微SD NAND/TF卡:赋能全场景数据存储,定义高效安全新基准2025-10-14 433

-

瀚海微SD NAND/TF卡数据读写超时(Data Transfer Timeout)问题深度解析2025-11-17 1143

-

瀚海微SD NAND TF卡硬件识别与初始化类问题探讨2025-11-18 775

-

解决SD NAND CRC校验失败的综合指南:瀚海微存储产品的可靠性保障2025-11-21 640

-

瀚海微SD NAND/TF卡数据损坏与校验错误(含CRC错误、数据比对失败)问题解析2025-11-30 1104

全部0条评论

快来发表一下你的评论吧 !