英特尔Mark Bohr:拨开迷雾,看清半导体制程节点命名

工艺/制造

描述

作者:马博(Mark Bohr),英特尔高级院士、技术与制造事业部制程架构与集成总监。他于1978年加入英特尔,一直负责内存和微处理器产品的制程技术的制程集成及元件设计。目前引领英特尔7纳米逻辑技术的开发工作。

此外,Mark Bohr还是电气与电子工程师协会(IEEE)的院士,并荣获2012年IEEE的西泽润一奖和2003年IEEE的安迪·格鲁夫奖。2005年,他被选入美国国家工程学院。他拥有集成电路制程领域的73项专利,并曾撰写或合著49篇公开发表的论文。

英特尔高级院士Mark Bohr

英特尔联合创始人戈登·摩尔在半世纪前提出的摩尔定律,是指每代制程工艺都要让芯片上的晶体管数量翻一番。纵观芯片每代创新历史,业界一直遵循这一定律,并按前一代制程工艺缩小约 0.7倍来对新制程节点命名,这种线性微缩意味着晶体管密度翻番。因此,出现了90纳米、65纳米、45纳米、32纳米——每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。

但是最近,也许是因为制程进一步的微缩越来越难,一些公司背离了摩尔定律的法则。即使晶体管密度增加很少,或者根本没有增加,但他们仍继续为制程工艺节点命新名。结果导致这些新的制节点名称根本无法体现位于摩尔定律曲线的正确位置。

行业亟需一种标准化的晶体管密度指标,以便给客户一个正确的选择。客户应能够随时比较芯片制造商不同的制程,以及各个芯片制造商的“同代”产品。但半导体制程以及各种设计日益复杂使标准化更具挑战性。

如果要标准化,有一种简单的计算公式就是用栅极距(栅极宽度再加上晶体管栅极之间的间距)乘以最小金属距(互连线宽度加上线间距),但是这并不包含逻辑单元设计,而逻辑单元设计才会影响真正的晶体管密度。另一种计算公式——栅极距乘以逻辑单元高度——是纠正上述缺失朝着正确方向的一步。但是这两种计算公式,都没有充分考虑到一些二阶设计规则。它们都不能真正衡量实际实现的晶体管密度,因为它们都没有试图说明设计库中不同类型的逻辑单元及这些指标量化相对于上一代的相对密度。行业真正需要的是给定面积(每平方毫米)内的晶体管绝对数量。另一种极端的公式,简单地用一个芯片的总晶体管数除以面积是毫无意义的,因为大量设计决策都会对它产生影响——例如缓存大小和性能目标等因素,都会导致这个值发生巨大变化。

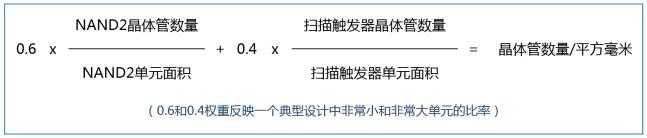

此时是让我们重新启用曾经流行但一度“失宠”的一个计算公式了,它基于标准逻辑单元的晶体管密度,并包含决定典型设计的多个权重因素。尽管任何设计库中都有很多标准单元的选择,但是我们可以拿出一个普及的、非常简单的单元——2输入 NAND单元(4个晶体管),以及一个比较复杂、但也非常常见的单元:扫描触发器(SFF)。这能够推导出之前被接受的晶体管密度测量公式。

每个芯片制造商在提到制程节点时,都应披露用这个简单公式所测算出的MTr/mm2 (每平方毫米晶体管数量(单位:百万))单位中逻辑晶体管密度。逆向工程公司可随时验证这个数据。

但还有一个重要的指标也不能忽略:SRAM单元尺寸。由于不同的芯片中有各种SRAM到逻辑的比率,最好在NAND+SFF密度指标旁边,分别标注SRAM单元尺寸。

通过采用这个计算公式,行业可以厘清制程节点命名的混乱状况,从而专心致志推动摩尔定律向前发展。

-

英特尔基于Intel 18A制程节点处理器样片成功出厂2024-08-07 1353

-

英特尔开启新时代:Intel 3制程节点引领性能与能效飞跃2024-06-14 1699

-

英特尔CEO:“四年五个制程节点”进展正在得到第三方肯定2023-11-10 954

-

英特尔和新思科技深化合作,提供基于英特尔先进制程节点的领先IP2023-08-26 1418

-

英特尔重新思考解决芯片短缺的常用基板2022-06-20 6930

-

英特尔正在考虑重新设定其制程节点的命名规则2021-04-13 3000

-

2020年半导体制造工艺技术前瞻2020-07-07 3549

-

英特尔半导体制程的节点命名2019-07-17 3599

-

半导体制程2018-11-08 5552

-

英特尔10纳米处理器一度跳票遭质疑,被指英特尔正收缩其半导体制造业务2018-08-03 3872

-

英特尔处境再陷尴尬,或抛弃半导体制造业务2018-07-06 1612

-

英特尔高级院士Mark Bohr:10年内看不到摩尔定律终点2017-09-23 1673

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 3201

-

英特尔:无晶圆厂经营模式快不行了2012-04-26 742

全部0条评论

快来发表一下你的评论吧 !