并行比较型AD转换器的工作原理和优点

描述

一、并行比较型AD转换器的工作原理

并行比较型AD转换器是模数转换器(ADC)中速度最快的一种类型。其工作原理基于并行处理技术,通过多个比较器同时工作,将输入的模拟信号与多个参考电压进行比较,从而一次性完成所有位的转换。

具体来说,并行比较型AD转换器内部包含一组精密的分压电阻网络,用于产生一系列阶梯状的参考电压。这些参考电压均匀分布在输入模拟信号的范围内。当输入信号被送入转换器时,它会同时与所有参考电压进行比较。每个比较器都连接到一个编码器,当输入信号大于或等于某个参考电压时,对应的比较器输出高电平(或低电平,取决于电路设计),否则输出低电平(或高电平)。编码器根据所有比较器的输出,一次性生成与输入模拟信号相对应的数字代码。

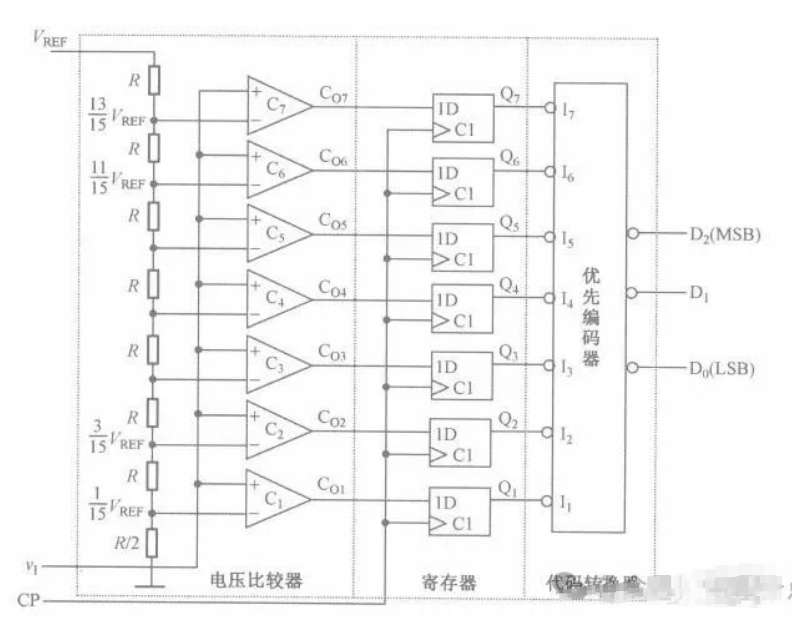

三位并行比较型A/D转换原理电路如图所示,它由电压比较器、寄存器和代码转换器三部分组成。电压比较器中量化电平的划分采用上一期中量化和编码中的图(b)所示的方式,用电阻链把参考电压D2VREF压,得到从1/15VREF ~ 13/15VREF之间7个比较电平,量化单位为2/15VREF。然后,把这7个比较电平分别接到7个比较器C1~C7,的输入端作为比较基准。同时将要输入的模拟电压同时加到每个比较器的另一个输入端上,与这7个比较基准进行比较。

二、并行比较型AD转换器的组成

并行比较型AD转换器主要由以下几个部分组成:

- 精密分压电阻网络 :用于产生一系列阶梯状的参考电压,这些电压覆盖了输入模拟信号的整个范围。分压电阻的精度和稳定性对转换器的性能有重要影响。

- 比较器阵列 :由多个高速比较器组成,每个比较器都与一个参考电压相连。比较器阵列并行工作,将输入信号与所有参考电压进行比较,并输出比较结果。

- 编码器 :接收比较器阵列的输出信号,并将其转换为与输入模拟信号相对应的数字代码。编码器通常采用高速逻辑电路实现,以确保转换速度。

- 时钟电路 :虽然并行比较型AD转换器在转换过程中不需要多个时钟周期来逐位转换,但时钟电路仍然用于控制转换过程的开始和结束,以及可能的其他时序功能。

- 控制电路 :用于管理整个转换过程,包括启动转换、读取转换结果等。控制电路还可以提供与其他数字电路的接口,如微处理器或数字信号处理器(DSP)。

三、并行比较型AD转换器的优点

并行比较型AD转换器因其独特的工作原理和组成结构,具有以下几个显著的优点:

- 转换速度快 :

- 由于采用了并行处理技术,所有位的转换同时完成,因此转换速度非常快。对于高速应用场合,如视频信号处理、高速数据采集等,并行比较型AD转换器是理想的选择。

- 转换速率通常可以达到纳秒级甚至更高,远高于其他类型的ADC。

- 精度高 :

- 由于使用了精密的分压电阻网络和高速比较器,并行比较型AD转换器能够实现较高的转换精度。虽然分辨率受到比较器数量和电路设计的限制,但在一定范围内仍然可以满足高精度应用的需求。

- 易于实现高速数据传输 :

- 并行比较型AD转换器的输出是并行数字信号,可以直接与高速数字接口相连,实现高速数据传输。这对于需要实时处理大量数据的应用场合尤为重要。

- 灵活性高 :

- 可以通过调整分压电阻的数量和比较器的位数来灵活配置转换器的分辨率和速度。这使得并行比较型AD转换器能够适应不同应用场合的需求。

- 抗干扰能力强 :

- 由于采用了并行处理技术,每个比较器都独立工作,因此局部干扰对整体转换结果的影响较小。此外,通过合理设计电路布局和采取适当的屏蔽措施,可以进一步提高转换器的抗干扰能力。

然而,值得注意的是,并行比较型AD转换器也存在一些缺点。例如,随着分辨率的提高,比较器的数量急剧增加,导致电路规模庞大、功耗增加、成本上升。此外,由于所有比较器都需要同时工作,因此对时钟信号的稳定性和精度要求较高。在实际应用中,需要根据具体需求权衡这些优缺点来选择合适的ADC类型。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

不同类型AD转换器的比较2024-10-05 9377

-

光电型波长转换器和全光型波长转换器的区别2024-08-09 2492

-

升压转换器的工作原理、优点和应用2024-02-01 5311

-

DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理2024-01-19 5745

-

DC-DC转换器工作原理是什么?2023-08-18 6347

-

#硬声创作季 11.6.1 Video 1106 并行比较型AD转换器Mr_haohao 2022-09-02

-

144. 并行比较型AD转换器#AD转换器电路设计快学 2022-07-29

-

A/D转换器的分类及简介2021-12-10 2572

-

最常用的A/D转换器有哪几种类型?2021-03-15 7194

-

AD转换中参考电压的作用2018-10-18 2753

-

DA转换器工作原理2012-08-20 3396

-

AD转换器的分类2012-08-11 4891

-

AD转换器 DA转换器的分类与指标简介2011-10-31 19313

-

AD转换器的种类介绍2011-03-11 4240

全部0条评论

快来发表一下你的评论吧 !