【GD32 MCU入门教程】GD32 MCU GPIO 结构与使用注意事项

描述

1.前言

本文是专门为基于GD32 MCU开发的工程设计人员提供,主要介绍了GPIO的功能配置、内部结构以及在不同场景使用时的注意事项,旨在帮助GD32 MCU开发者优化对通用型输入输出端口(GPIO)的使用,正确快速的使用GD32 MCU进行产品开发。

GPIO,通用型输入输出端口的简称,可以通过软件配置其输出或者输入,GD32 的 GPIO 引脚与外部设备连接,从而实现与外部通信,控制以及信号输入的功能,是 GD32 MCU 中很常见,使用最广泛的模块。

每个 GPIO 引脚可以由软件配置为输出(推挽或开漏)、输入、外设备用功能或者模拟模式。

每个 GPIO 引脚都可以配置为上拉、下拉或浮空模式或无上拉/下拉。

GD32 MCU GPIO 主要特征有:

◼ 输入/输出方向控制;

◼ 施密特触发器输入功能;

◼ 每个引脚都具有弱上拉/下拉功能;

◼ 推挽/开漏输出使能控制;

◼ 置位/复位输出使能;

◼ 可编程触发沿的外部中断—使用EXTI配置寄存器;

◼ 模拟输入/输出配置;

◼ 备用功能输入/输出配置;

◼ 端口锁定配置。

对于 GD32 某些系列 MCU 的 GPIO 可能具有更多功能,如时钟、I2C、SPI、CAN、USART、USB、ADC、DAC 等,在进行电路板设计前应查看该系列的数据手册与用户手册,对比所使用的 GPIO 是否满足需求。

2.GPIO 结构

在 GD32 MCU 中,通常有两种类型的 GPIO,非 5V 耐受 IO 以及 5V 耐受 IO(部分 MCU 没有 5VT 引脚,如 GD32A503xx 系列),两种类型的 IO 在结构上略有区别。如图 2-1. 标准 IO基本结构图所示为一个标准 IO 口的基本结构图:

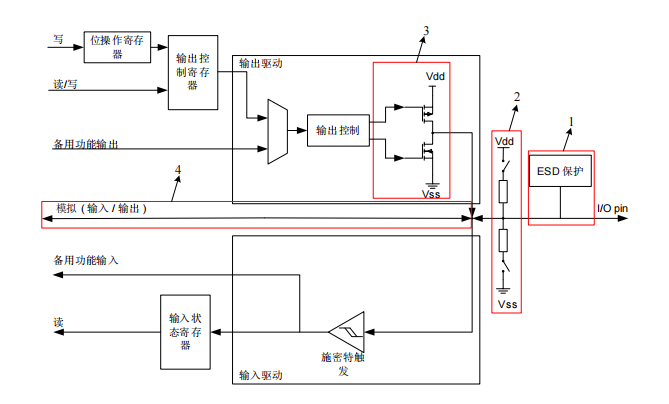

图 2-1. 标准 IO 基本结构图

I/O pin 表示的芯片的 I/O pad,与外部电路相连接,其他部分电路都是芯片的内部电路。其中框图的上半部分表示 IO 的输出部分电路,当 IO 使用其备用功能连接内部其他外设时,也会共用相关功率输出部分电路。框图的下半部分表示 IO 的输入电路部分,作为备用功能连接内部其他外设时,同样也会共用输入部分电路,如施密特触发器。

框图的中间部分如红框 4 内的电路表示模拟输入输出通道,模拟通道输出时(如 DAC 输出)不经过功率输出电路,输入时也不经过施密特输入电路,直接将外部电路通过 IO pin 与内部的模拟外设直接连接。

红框 3 表示的是 IO 输出时的主要功率电路,配置相关的控制寄存器,可以控制上、下两个 MOS 管导通以实现推挽输出或者是开漏输出。

红框 2 表示 IO 口的内部上拉或者下拉电路,通过相关寄存器的配置可以实现输入口的内部上拉或者内部下拉,上拉/下拉电阻的阻值可以参考数据手册,典型值为 40kΩ,少数引脚上下拉电阻非 40 kΩ,如 GD32F425xx 的 PA10 引脚上下拉电阻为 10 kΩ,详细数据可查看数据手册中 GPIO characteristic 章节。

红框 1 中表示的 ESD 保护电路。

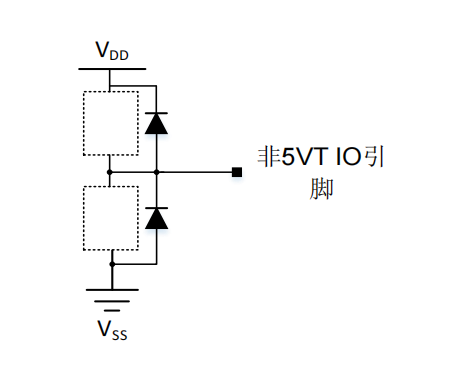

非 5VT IO 的 ESD 保护电路如图 2-2. 非 5VT IO 引脚基本结构图所示,ESD 保护电路在 IO对 VDD 和 VSS 分别形成两个二极管,显然,如果 IO 上的电压比 VDD 的电压大于二极管的正向导通压降,或者 IO 上电压比 VSS 电位低,且压差大于二极管的正向导通电压,则会产生从 IO到 VDD,或者从 VSS 到 IO 的电流。

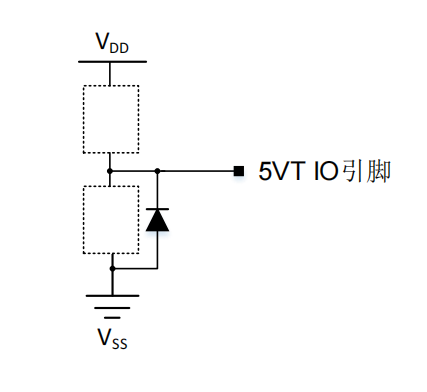

5VT IO 的 ESD 保护电路如图 2-3. 5VT IO 引脚基本结构图所示,5VT IO 引脚没有连接到电源(VDD)的内部保护二极管。

因此,在实际使用中若存在引脚先上电,MCU 后上电的情况,优先选择使用 5VT 的引脚作为与外部连接先上电引脚,避免由于引脚漏电造成 IO 引脚拉低;若必须选择标准 IO 引脚,需采用比如三极管等隔离措施,防止引脚漏电。

图 2-2. 非 5VT IO 引脚基本结构图

图 2-3. 5VT IO 引脚基本结构图

注意:5VT IO 与非 5VT IO 内部结构有部分区别。

3.典型应用场景与注意事项

不同类型的 IO 在使用时有一些注意事项,接下来分别从输入与输出两个角度来描绘下不同类型 IO 的典型应用场景与特性以及注意事项。

3.1.IO 输入

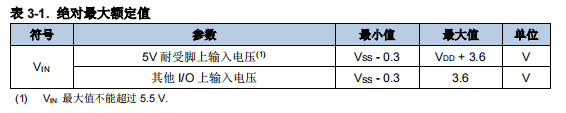

首先是 IO 口的输入电压范围,输入耐压值表示 IO 口所能容忍的输入电压范围,部分 GD32MCU 含有 5VT IO 与非 5VT IO,5VT IO 与非 5VT IO 有着不同的特性,如用户手册中的表 3-1.绝对最大额定值所示。

针对 IO 口的输入场景,我们有几点需要注意:

1. 对于 5VT IO,当 VDD=0 时(即 MCU 未上电时),其引脚输入电压不能超过 3.6V;

2. 我们需要根据 IO 口外部输入信号的电压值范围来慎重选择 5VT IO 还是非 5VT IO,如果输入信号已经大于 5.5V 了,就要将信号调理成适宜的范围再送到 MCU 的 IO 口;

3. GPIO 输入低电平判定范围为≤0.3 VDD ,GPIO 输入高电平判定范围为≥0.7VDD ;

4. 根据前面描述不同类型 IO 口的典型结构,如果非 5VT IO 上的电压比 VDD 电压大 0.3V 以上,则会可能使 ESD 保护电路中 IO 对 VDD 的二极管导通造成漏电,尤其是在 MCU 未上电,而 IO 口就已经有电平时的情景,此时,如果选择 5VT IO 可以有效规避从 IO 向 VDD漏电的情况;典型的,如果 IO 接入的是 I2C 总线,我们就需要选择 5VT 引脚;

5. MCU 所有的 IO 在上电完成还未进行其他配置时,均默认工作在浮空输入模式,其中调试口为上拉或下拉模式,具体的上拉还是下拉请参照用户手册。因此,在一些需要产生固定电平的场景中,如果 MCU 从待机模式复位,则需要考虑这些 IO 口的默认输入上下拉状态,且在程序重新配置这些 IO 的状态之前,默认状态不会变化;

6. 为了获得更低的功耗水平,尤其是在睡眠模式和深度睡眠模式中,需要将未使用的 IO 配置成模拟输入,或者配置为浮空输入状态的同时外部加上下拉,或者设置为内部上拉或下拉。需注意设置内部上拉时,外部不可再硬件下拉,避免额外功耗,同理,内部下拉时,外部不可硬件上拉(这里未使用的 IO 也包括在本封装上未引出来的 IO)。对于 GD32 低功耗 MCU 产品,在运行模式下,如前描述的设置也会获得最好的功耗表现;

7. 5VT IO 只有在输入模式下才可输入最大 5.5V 电压。当输出模式被启用时,5VT IO 不再可以承受 5.5V 电压。有关 I/O 输入电压的详细信息,请参阅数据表通用操作条件表中的 VIN参数;

8. 只有在引脚上没有启用模拟功能时,5VT IO 才可输入最大 5.5V 电压。如果在 5VT IO 上启用了一些模拟输入功能(ADC 输入有源,COMP 输入,OPAMP 输入),那么引脚上的最大工作电压不能超过 min(VDDA, VREFP) + 0.3 V。

3.2.IO 输出

在 IO 输出的场景我们也有一些要点需要注意,

1. 开漏输出电压与输出带载电流有非常显著的关系,通常 IO 在输出高时,如果所带负载越大,则输出的高电平就会被往下拉的越低,同理,如果 IO 在输出低时,流进 IO 的电流越大,则 IO 输出的低电平就会被往上拉的越高;

2. 对于 MCU 中存在备份域的型号,其中有部分 IO 是工作在备份域电源中的,这些 IO 的带载能力有限,建议这些 IO 的 IO speed 参数设置为最低速度(一般为 2MHz)。如 GD32F4xx系列中的 PC13、PC14、PC15、PI8 四个引脚,不同系列驱动能力较弱的引脚不同,详细信息可在该系列数据手册中查询;

3. GPIO 可通过电流与 IO 配置速度有关,目前所有 GD32 MCU IO 最大可通过电流均为 25mA(工作在备份域的引脚除外),GPIO 拉电流以及灌电流均不可超过 25 mA。当 GPIO速度配置较低时,其拉电流与灌电流能力可能达不到 25 mA;

4. 部分 GD32 MCU 包含 I/O 补偿单元,如 E50x 系列。默认情况下,I/O 补偿单元是不使用的,当 I/O 端口输出速度大于 50MHz 时,建议使用 I/O 补偿单元对 I/O 端口进行斜率控制,从而降低 I/O 端口噪声对工作电源的影响;

5. IO 在高低电平转换时过冲会随着 IO 口速度增大而增大,可通过降低 IO 口速度来减少过冲;

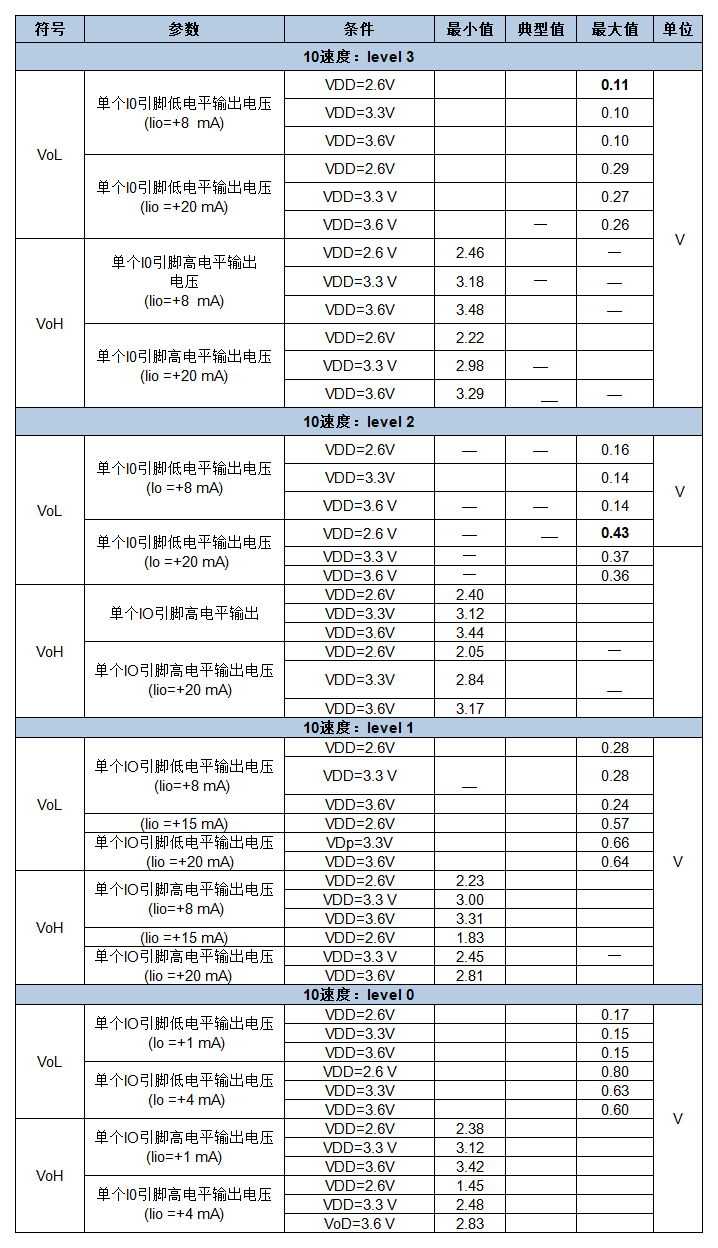

6. GPIO 输出的高低电平并非绝对的零或者 VDD,而会随着 IO 配置的速度、VDD 电压、输出电流的大小而变化。如表 3-2. GD32F425xx GPIO DC 特性所示为 GD32F425xx GPIO 输出高低电平随这些变量变化的数据表。

3.3.其他注意事项

为了更好的提升 GD32 MCU 在一些典型应用场景下的性能,在使用 GD32 MCU 的 GPIO 时还需注意以下事项:

1. 部分系列 GD32 MCU ADC 输入引脚为标准 IO 引脚,需注意避免 ADC 输入电压超过VDD+0.3V 的情况,否则可能由于漏电造成 ADC 采样异常;在使用 ADC 模块时,所有ADC 引脚均不可引入负电压,否则将导致 ADC 采样不准;

2. VBAT 引脚允许从外部电压源(电池或电容)为 GD32 备份域供电。当 GD32 微控制器仅通过VBAT 引脚供电时,只有在备份域里的 GPIO 才能工作。备份域的 GPIO 驱动能力较弱,且不同系列的备份域 GPIO 不同,可在该系列的用户手册中查看。对于没有外部电池的应用,建议将 VBAT 引脚通过 100nF 的外部陶瓷去耦电容接地后连接到 VDD 引脚上;

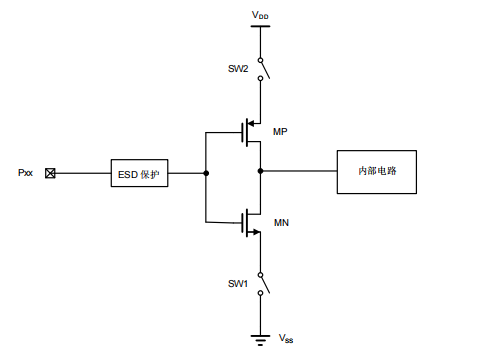

3. 为提高 EMC 性能以及避免浮空输入 IO 漏电风险,未使用的 IO 口引脚建议硬件上拉或者是下拉。IO 的输入电路可以简化为图 3-1. IO 输入电路简化图,Pxx 表示 MCU 的某一个引脚。当IO 配置为浮空输入模式时,SW1 和 SW2 导通。如果 Pxx 没有外部电压驱动,则 Pxx 的电压为 VSS~VDD 之间的任意电压值。假设图 3-1. IO 输入电路简化图中 MN 的阈值电压是VTHN,MP 的阈值电压是 VTHP,当 Pxx 的电压处在 VTHN~(VDD-VTHP)时,MN 和 MP 同时开启,VDD 到 VSS 之间可能会有非常大的漏电。

当 IO 配置为上拉模式、下拉模式或模拟模式时,MP 和 MN 不会同时导通,VDD 到 VSS之间不会有漏电。

图 3-1. IO 输入电路简化图

4. 多组中同一标号 PIN 仅可配置一个 IO 口为外部中断,例:PA0、PB0、PC0 仅支持三个中的其中一个 IO 口产生外部中断,不支持三个同为外部中断模式;

本教程由GD32 MCU方案商聚沃科技原创发布,了解更多GD32 MCU教程,关注聚沃科技官网

-

GD32单片机GPIO结构及注意事项2025-02-07 925

-

【GD32 MCU 入门教程】GD32 MCU FPU 使用方法2024-08-25 2681

-

【GD32 MCU 入门教程】GD32 MCU 常见外设介绍(14)RTC 模块介绍2024-08-23 2832

-

GD32 MCU 入门教程】GD32 MCU 常见外设介绍(12)FMC 模块介绍2024-08-21 4007

-

【GD32 MCU 入门教程】一、GD32 MCU 开发环境搭建(1)使用Keil开发GD322024-08-08 5391

-

GD32 MCU如何将烧录口配置为GPIO使用?2024-02-20 3802

-

不同型号的GD32 MCU如何区分?2024-01-27 2673

-

GD32 MCU的选项字节是什么?2024-01-17 3427

-

AN092GD32MCU GPIO结构与使用注意事项2023-03-01 682

-

兆易创新GD32 MCU选型手册,适用于GD32全系列MCU2022-10-19 2692

-

GD32与STM32的异同点2022-02-21 1833

-

GD32大容量产品软件的移植注意事项2019-11-14 1826

全部0条评论

快来发表一下你的评论吧 !