数据中心加速器就看GRVI Phalanx FPGA加速器

电子说

描述

背景

数据中心采用FPGA做加速器已经成为主流,像MS的Catapult,Amazon基于Xilinx FPGA的AWS F1,Intel的Altera,Baidu公司等。数据中心具有大规模并行数据处理,高数据吞吐量,低延时,能效高等特点。但是存在两个问题,第一个是软件的问题,软件移植和保证一定加速的工作负荷;第二个是硬件的问题,配备众核处理器,25-100G的网络接口卡,一些DRAM/HBM通道,容易时序收敛等。

现介绍一种GRVI Phalanx FPGA加速器结构。其中,GRVI是一种基于FPGA的有效的RISC-V运算单元,即RISC-V RV321软处理器核;Phalanx是一种并行FPGA加速器框架,由PE集群,SRAM,加速器,DRAM,I/O控制器等组成,减少在开发和管理FPGA加速器时所需付出的消耗和努力;还需要Hoplite NoC,它是一种基于FPGA优化的定向2D环形片上网络系统,用到的技术还有局部内存共享和全局信息流通等。

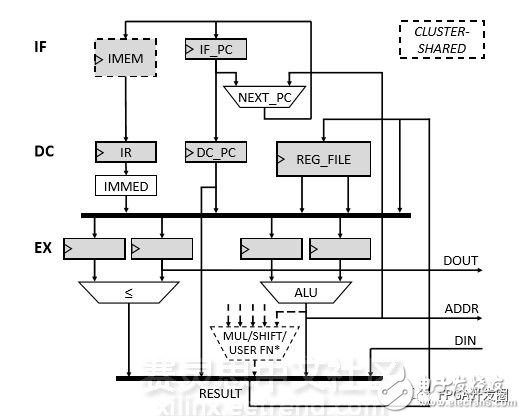

图.1 GRVI运行单元

先看一下GRVI Phalanx的1680个核的运算单元,运算单元是基于32位的RISCV微处理器架构,在一个多核心的芯片中,去掉了每一个核心中的不必要的资源,目的是减小每一个单元的芯片面积。因此,每一个GRVI处理单元都是三级流水的,采用用户模式下的RV321核心,减掉了部分不必要的位和其他模块,具体结构如图.1所示。每个GRVI运行单元需要320个LUT,而且能够跑在375MHz的频率下,看到博主Jan Gray所设计的众核处理器芯片(详情见“GRVI Phalanx: A Massively Parallel RISC-V FPGA Accelerator Framework: A 1680-core, 26 MB SRAM Parallel Processor Overlay on Xilinx UltraScale+ VU9P”),其特点是每一个GRVI运行单元都是手动排布的,将单个处理器单元在Xilinx FPGA的UltraScale+的架构下重复1680次,并将生成的文件下载到板卡Xilinx VCU118 Eval Kit上的Virtex UltraScale+VU9P FPGA芯片中。

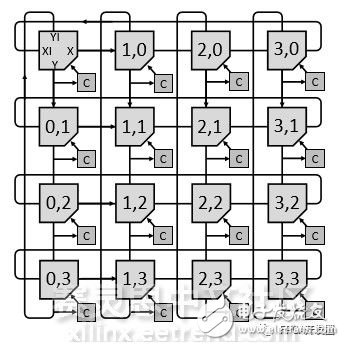

将一大堆的处理器核心一股脑的扔进Xilinx 的Virtex UltraScale+ VU9P FPGA芯片中听起来很有趣,但是如果不给每一个核心都匹配一些内存的话,也不能给这么多核心的处理器核心委以重任。因此,每一个在集群中的GRVI处理器单元都会配备8个RISCV处理器核心和32到128 Kbyte的RAM,以及另外的一些加速器。整个加速芯片的功耗为31-40W,单个核心的功耗为24mW,最大的吞吐量是0.4TIPS,内存带宽能够达到2.5TB/s。同一个芯片中的核心集群之间都会相互连接,芯片和外部的I/O端口的通信是通过HOPLITE路由连接到一个NOC(片上网络)来实现的,NOC节点之间的数据通信速度可达100Gbps,HOPLITE路由是一个经过FPGA优化的定向路由,是专门为2D环形网络所设计的,如图2所示。

图.2 一个400MHz的4*6*256 Hoplite NoC,100 Gb/s links

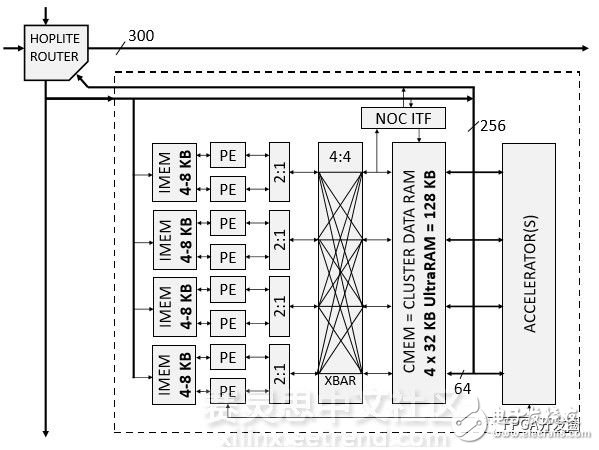

GRVI Phalanx集群单元如图3所示,软件部分需要有多线程的C++的编译器,信息传递的执行时间在RISC-V的RV321MA GCC编译器中分层排布,为的是在将来的计划中支持像OpenCL,P4和其他的一些编程工具。

图.3 GRVI Phalanx集群

还有其他的案例,拥有80个核心的GRVI Phalanx被实例化到可编程的Zynq Z-7020 SOC中,此案例是在Digilent PYNQ-Z1开发板中作为教学所用的一种。

更令人惊喜的是,硬件开发云端的出现,让硬件设计人员不用买昂贵的开发板也可以进行开发工作,只需要动动自己触手可及的鼠标和键盘,通过亚马逊的平台:Amazon AWS EC2 F1.2XL and F1.16XL instances,找到相关的Verilog芯片开发代码就可以进行自己的创作了。

总结

数据中心的加速器要从软件和硬件上同时进行,软件是要有加速算法,需要考虑算法的可移植性和稳定性;硬件方面可以使用文中分析的多核处理器的解决方案,当然要考虑软件移植性、编译工具的易用性、硬件本身的设计困难和硬件的性能、功耗、易维护性等方面。Xilinx的FPGA在数据中心的并行运算中扮演着一个重要的角色。

-

数据中心中的FPGA硬件加速器2025-01-14 1602

-

粒子加速器的加速原理是啥呢?2023-12-18 4933

-

Alveo数据中心加速器卡入门指南2023-09-15 702

-

Alveo U30数据中心加速器卡数据手册2023-09-13 536

-

数据中心 AI 加速器:当前一代和下一代2023-07-14 525

-

#硬声创作季 电子制作:磁性加速器Mr_haohao 2022-10-19

-

AI加速器能不能实现绿色数据中心2020-11-26 958

-

FPGA预计是数据中心加速器市场中年均增长率最高的细分市场2020-07-14 1213

-

数据中心加速器也许会是FPGA最高的细分市场2019-11-08 1509

-

GRVI Phalanx实现千核处理器2017-02-15 4866

全部0条评论

快来发表一下你的评论吧 !