同步开关噪声产生的原因和影响

描述

电源完整性的隐性杀手

在现代高速电子设计中,电源完整性(Power Integrity,PI)问题已成为影响系统性能的关键因素之一。在电源完整性问题中,同步开关噪声(Simultaneous Switching Noise,SSN)是一个经常被提及但又容易被忽视的重要概念。 同步开关噪声(SSN),又被称为地弹(Ground Bounce)或数字噪声(Digital Noise),是指在数字电路中,当大量输出驱动器同时切换状态时产生的电源噪声。这个现象主要发生在集成电路的电源与地平面之间,通常在高速数字电路和系统中尤为明显。

同步开关噪声产生的原因

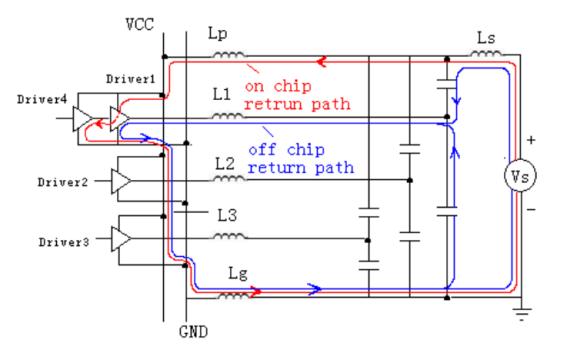

大量的芯片同步切换时,产生的瞬态电流在电源或地平面上产生大量噪声,因此 SSN 也被称为 Δi 噪声。当信号从低电平切换到高电平时,需要从电源模块吸收能量,电流开始流动,但因为我们的互连设计不是理想的,电源走线上会有阻抗,阻挡电流立刻到达芯片引脚。另外寄生电感也会使电路在开关电流的存在下带来电压波动,形成电压噪声。I/O 开关速度越快,瞬时电流变化越快,在电流回路上产生的噪声越大。这种噪声会通过电源系统传播,带来的电源完整性问题影响整个系统的性能。

同步开关噪声的影响

· 信号完整性:SSN 会对信号完整性产生严重影响,导致信号过冲、下冲、抖动等问题,甚至可能引发误码。

· 电源完整性:SSN 会在电源系统中引起瞬态电压跌落,导致电源不稳定,影响敏感的模拟和数字电路的正常工作。

· 电磁干扰(EMI):由于 SSN 会在电源平面上产生高频噪声,这种噪声很容易通过 PCB 板的走线或电缆辐射出去,增加系统的电磁辐射水平。

如何减少同步开关噪声的负面影响

· 增加电源与地平面的耦合,减小寄生电感。

· 使用多层板设计,将电源与地平面相互叠加,提高电源平面的平滑性。

· 在关键位置放置去耦电容,尤其是靠近驱动器或IC的电源引脚处,提供局部电源。

· 采用星形拓扑结构,将电源从电源输入端到各个负载分配得当,减少电流突变对其他电路的影响。

· 采用电源完整性仿真工具进行预先评估和优化设计。

如何使用仿真工具优化设计

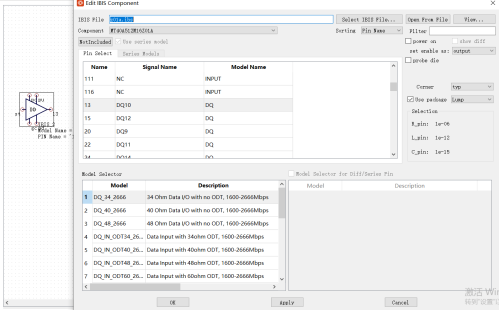

使用巨霖 SIDesigner,可以对 IBIS 模型开放供电接口,引入 SSN 的分析。

在 SIDesigner 的 IBIS 模型“IC”中,导入 IBIS 文件和模型,去勾选 power on,即可用外接供电。

结合设计师的电源电路设计,搭配 SIDesigner 内嵌的高精度硅验证 TJSPICE 仿真引擎对高速电路进行预仿真,通过波形结果观察并测量 SSN 情况,进行设计迭代优化。

欢迎从官网申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

-

开关电源纹波噪声产生原因,开关电源纹波噪声怎么解决2024-06-09 2864

-

开关电源的纹波和噪声产生的原因2023-08-29 2233

-

开关电源谐波电流产生的原因2023-08-18 3398

-

EMC基础:开关电源产生的噪声2023-02-15 1547

-

开关电源的噪声是如何产生的2023-01-07 1927

-

开关电源产生噪声的原因2021-12-30 898

-

电源完整性之同步开关噪声SSN2021-10-21 2020

-

纹波和噪声产生的原因2021-07-29 2355

-

开关电源噪声产生的原因2021-03-11 10093

-

开关电源产生的噪声的原因与解决方案2019-02-28 17289

-

开关电源产生的噪声2018-11-29 2567

-

开关电源噪声的产生原因及抑制方法2017-09-11 1104

-

开关电源特点及噪声产生原因2011-07-11 4988

-

开关电源产生纹波和噪声的原因和测量方法2010-12-21 8606

全部0条评论

快来发表一下你的评论吧 !