关于DS1302典型应用原理图

接口/时钟/PLL

描述

DS1302是DALLAS(达拉斯)公司出的一款涓流充电时钟芯片,2001年DALLAS被MAXIM(美信)收购,因此我们看到的DS1302的数据手册既有DALLAS的标志,又有MAXIM的标志。

DS1302特性:

--秒分时日日期月年的信息

--每月的天数和闰年的天数可自动调整

--可通过AM/PM 指示决定采用24 或12 小时格式

--保持数据和时钟信息时功率小于1mW

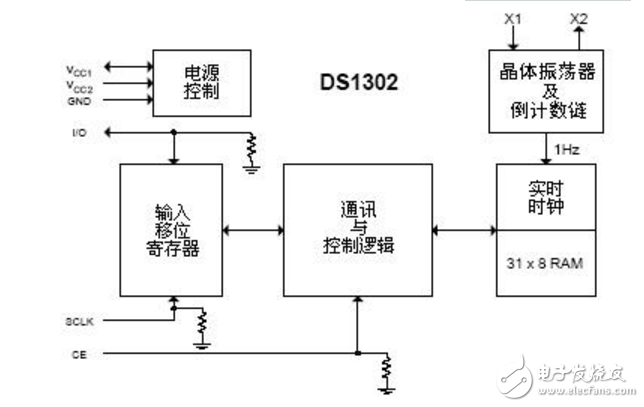

DS1302的内部结构:

DS1302的内部结构如下图所示,主要组成部分为:移位寄存器、控制逻辑、振荡器、实 时时钟以及RAM。虽然数据分成两种,但是对单片机的程序而言,其实是一样的,就是对特定的地址进行读写操作。

DS1302含充电电路,可以对作为后备电源的可充电电池充电,并可选择充电使能和串入的二极管数目,以调节电池充电电压。不过对我们目前而言,最需要熟悉的是和时钟相关部分的功能,对于其它参数请参阅数据手册。

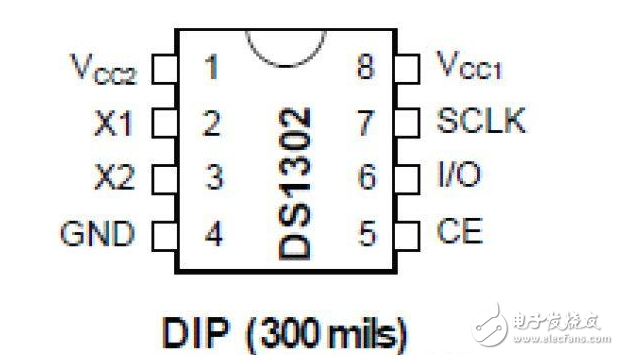

DS1302的引脚功能及结构:

图中DS1302的引脚排列,其中Vcc1为后备电源,VCC2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。

RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端(双向),后面有详细说明。SCLK始终是输入端。

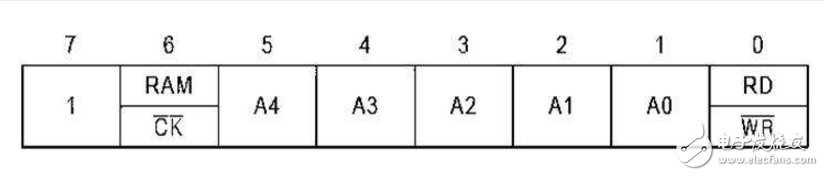

DS1302控制字节:

控制字节DS1302 的控制字符表示。控制字节的最高有效位(位7)必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;最低有效位(位0)如为0表示要进行写操作,为1表示进行读操作,控制字节总是从最低位开始输出。

输入输出在控制指令字输入后的下一个SCLK时钟的上升沿时,数据被写入DS1302,数据输入从低位即位0开始。同样,在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,读出数据时从低位0位到高位7。

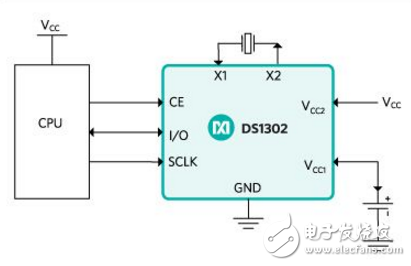

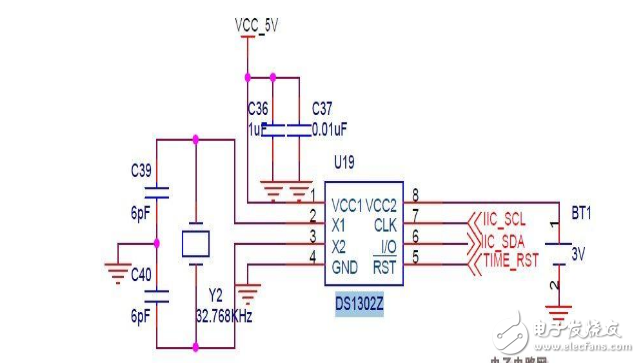

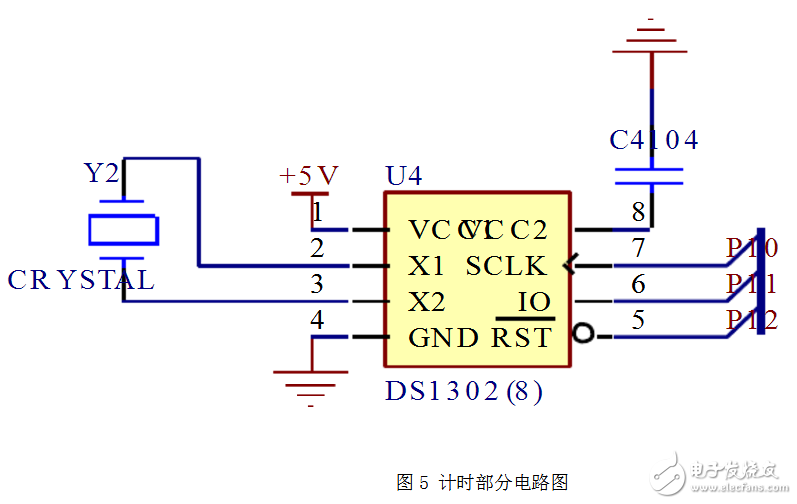

DS1302典型应用原理图

DS1302与单片机的连接也仅需要3条线:CE引脚、SCLK串行时钟 引脚、I/O串行数据引脚,Vcc2为备用电源,外接32.768kHz晶振, 为芯片提供计时脉冲。

实际电路:

DS1302典型应用原理图

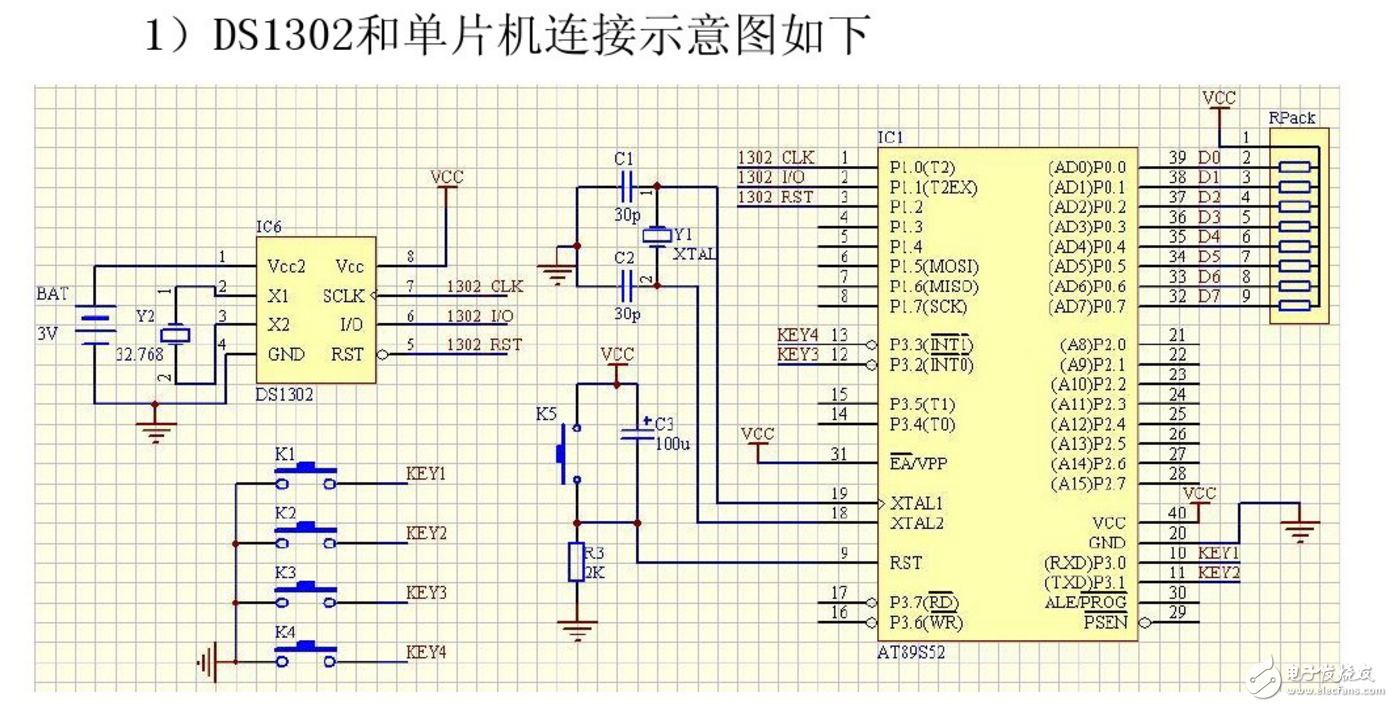

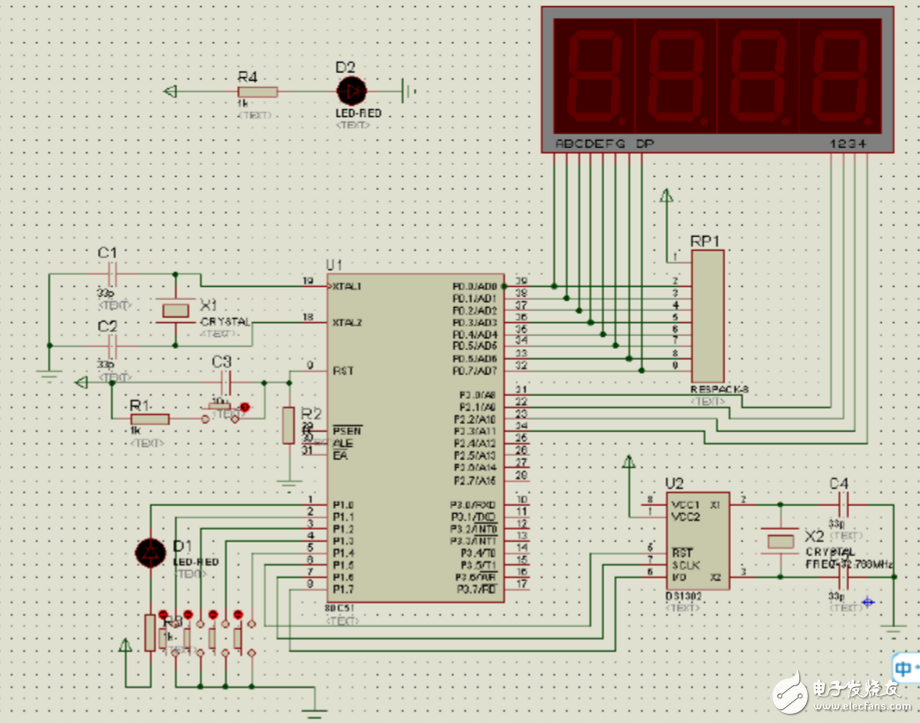

基于DS1302的数码管显示数字钟电路图

时钟芯片DS1302与外围电路的连接:与MCS-51单片机的接口是由3条线来完成的,MCS-51单片机的P1.0与时钟芯片的数据传输端I/O相连,P1.1用来作为DS1302输入时钟SCLK控制端,P1.2控制DS1302的复位输入端RST。DS1302的X1和X2管脚外接标DS1302的复位引脚通过把RST输入驱动置高电平来启动所有的数据传送。 RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供了终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中置RST为低电平,则会终止此次数据传送,并且I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。

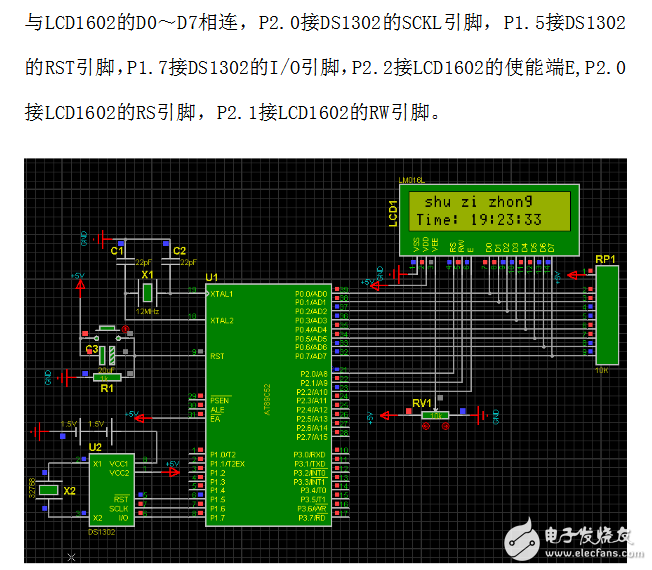

DS1302 数字钟设计原理图

-

DS1302时钟芯片原理2021-12-07 1460

-

设计LCD12864显示DS1302模拟表盘时钟的原理图与PCB图免费下载2020-01-02 1932

-

请教关于ds1302的问题2019-10-16 2262

-

DS1302 RTC电路原理图的资料免费下载2019-01-08 2366

-

DS1302元器件原理图和PCB封装的资料免费下载2018-11-28 3137

-

Arduino控制DS1302时钟芯片(ds1302引脚图及功能和应用电路)2018-05-14 56857

-

DS1302实时时钟模块原理图2017-02-14 2531

-

DS1302时钟模块原理图2016-04-06 1473

-

DS1302源程序_原理图_PCB2016-02-15 1003

-

ds1302原理图+pcb制作2015-12-31 2130

-

DS1302原理图2012-11-20 1

-

DS1302时钟原理图2012-11-19 8

-

DS1302与CPU连接的电路原理图2009-05-17 3989

-

ds1302 pdf2008-01-14 1549

全部0条评论

快来发表一下你的评论吧 !