s3c2440如何设置fclk

嵌入式软件/开发板

描述

1设置LockTime变频锁定时间

2设置FCLK与晶振输入频率(Fin)的倍数

3设置FCLK,HCLK,PCLK三者之间的比例

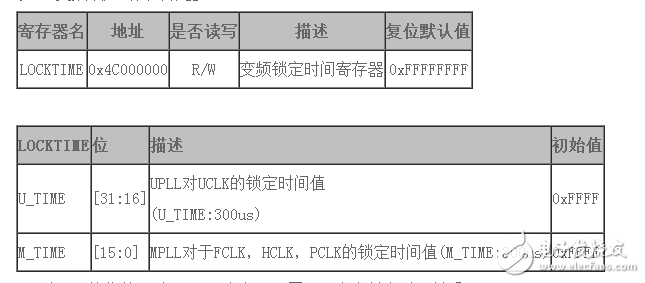

LockTime 变频锁定时间由LOCKTIME寄存器(见下表)来设置,由于变频后开发板所有依赖时钟工作的硬件都需要一小段调整时间,该时间计数通过设置 LOCKTIME寄存器[31:16]来设置UPLL(USB时钟锁相环)调整时间,通过设置LOCKTIME寄存器 [15:0]设置MPLL调整时间,这两个调整时间数值一般用其默认值即可。

表2-8变频锁定时间寄存器(LOCKTIME)

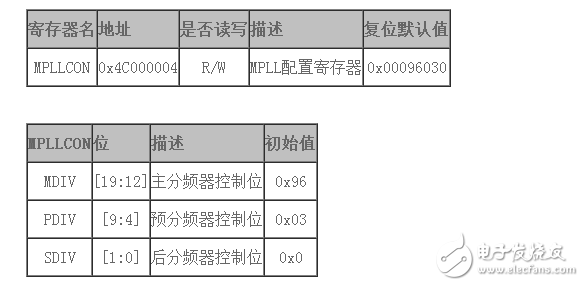

FCLK与Fin的倍数通过MPLLCON寄存器设置,三者之前有以下关系:

MPLL(FCLK) = (2*m*Fin)/(p*2^s)

其中:m = MDIV + 8, p = PDIV + 2, s = SDIV

当设置完MPLL之后,就会自动进入LockTime变频锁定期间,LockTime之后,MPLL输出稳定时钟频率。

表2-9 MPLL配置寄存器(MPLLCON)

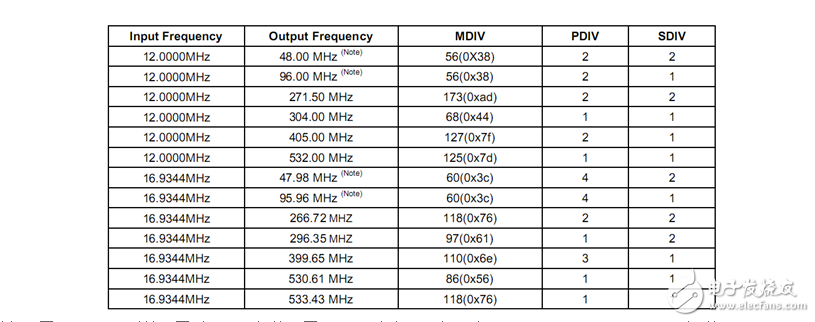

通过上述算法比较难以找到合适的PLL值,下表给出了官方推荐的一些MPLL参考设置:

表2-10 官方推荐MPLL

MPLL(FCLK) = (2*(MDIV+8) * Fin) / ((PDIV+2) * 2^(SDIV))。

确定时钟频率最关键的代码:

ChangeMPllValue((mpll_val》》12)&0xff, (mpll_val》》4)&0x3f, mpll_val&3);

上面调函数实现了MDIV=92 PDIV=1 SDIV=1从而计算MPLL和UPLL的值。

m=(MDIV+8)=100, p=(PDIV+2)=3,s=SDIV=1.

ChangeClockDivider(key, 12);

再找出函数的原型分析下,

//*************************[ MPLL ]*******************************

下面这个函数就是确定MPLLCON寄存器的值也就是确定MDIV、PDIV、SDIV的值。

void ChangeMPllValue(int mdiv,int pdiv,int sdiv)

{

rMPLLCON = (mdiv《《12) | (pdiv《《4) | sdiv;

}

上面已经计算出来m=(MDIV+8)=100, p=(PDIV+2)=3,s=SDIV=1.

m p s 的值,从而可以得出 MPLL=(2*100*12)/(3*1)=400MHZ

m=77+8=85,p=5,s=0

UPLL=(85*12)/(5*1)=97/5=

FCLK=400MHZ

又因为FCLK:HCLK:PCLK的分频比为1:4:8,从而得到HCLK的值为100MHZ,PCLK的值为50MHZ。

-

教你如何设置S3C2440时钟2013-11-12 3608

-

S3C2440时钟体系结构2018-05-08 5114

-

ARM S3C2440时钟的使用2022-04-26 2183

-

s3c2440 pdf datasheet2008-07-10 1685

-

S3C2440应用电路图2009-09-14 1229

-

基于S3C2440的无线物流终端机的设计与应用2010-01-07 570

-

s3c2440整套中文手册 datasheet2010-03-02 782

-

S3C2440中文手册2010-07-30 928

-

s3c2440 mmc和camera的linux驱动2011-05-25 850

-

s3c2440全套中文手册2017-03-19 1272

-

裸机学习s3c24402017-10-13 1028

-

s3c2440用户资料手册2017-10-16 1293

-

(1)电源管理-S3C2440芯片电源管理模块解析2022-01-05 1161

-

S3C2440如何设置系统时钟2023-09-02 1717

-

基于S3C2440的裂纹实时测量系统的设计2023-10-11 430

全部0条评论

快来发表一下你的评论吧 !