74ls374引脚图及功能真值表

接口定义

119人已加入

描述

74ls374引脚图及功能真值表八上升沿D触发器(3S,时钟输入有回环特性)简要说明:374为具有三态输出的八D边沿触发器,共有54/74S374和54/74LS374两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号fmPD54S374/74S374100MHz450mW54LS374/74LS37450MHz135mW374的输出端O0~O7可直接与总线相连。当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。当OE为高电平时,O0~O7呈高阻态,即不驱动。

简要说明:

74ls374为具有三态输出的八 D 边沿触发器,共有 54/74S374 和 54/74LS374 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号 fm PD

54S374/74S374 100MHz 450mW

54LS374/74LS374 50MHz 135mW

374 的输出端 O0~O7 可直接与总线相连。当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当时钟端 CP 脉冲上升沿的作用下,O 随数据 D 而变。由于 CP 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

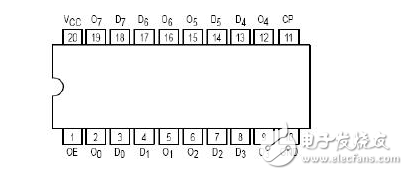

引出端符号:

D0~D7 数据输入端

OE 三态允许控制端(低电平有效)

CP 时钟输入端

O0~O7 输出端

74ls374引脚管腿图:

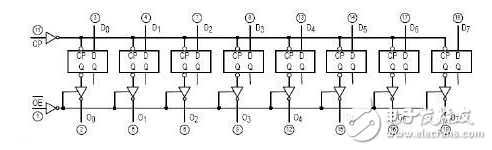

74ls374逻辑图:

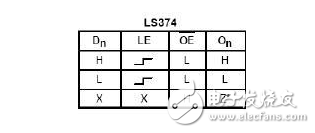

74ls374功能真值表:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 74LS14

-

74ls160引脚图及功能真值表介绍2022-05-25 178712

-

74ls00引脚图及功能真值表和特性参数2021-06-16 204833

-

74ls374中文资料汇总(74ls374引脚图及功能_工作原理及应用电路)2018-05-28 50533

-

74ls374中文资料汇总(74ls374引脚图及功能_真值表及特性)2018-05-09 31543

-

74ls125中文资料(74ls125引脚图及功能_真值表)2018-05-04 111845

-

74ls09引脚图及功能表_真值表和特性参数2018-04-09 33648

-

74ls93引脚图管脚图及功能真值表2008-12-01 23355

-

74ls11引脚图及管脚功能真值表2008-06-08 53033

-

74ls374引脚图及功能真值表2008-04-01 34689

-

74ls160引脚图管脚图及功能真值表2008-01-06 132493

-

74ls04引脚图 引脚功能2007-11-29 76555

全部0条评论

快来发表一下你的评论吧 !