msp430f5529定时器

嵌入式软件/开发板

描述

MSP430F5529是最新一代的具有集成USB的超低功耗单片机,可以应用于能量收集、无线传感以及自动抄表等场合,是最低工作功耗的单片机之一。MSP430F5529开发板( MSP-EXP430F5529)是MSP430F5529单片机的开发平台,由电源选择开关、RF射频接口、 microSD card插槽、MSP430F5529芯片及引出引脚、USB接口、JTAG仿真接口、齿轮电位计、电容触摸按键、LED、按钮、 EZ-FET内置仿真器、102x64点阵LCD和三坐标轴加速度计组成。该开发板将I/O引脚接出来,方便用户进行实验操作,既可用于科研开发,又适合实验教学、课程设计、毕业设计等,为广大高校师生提供了良好的实验开发环境,同时也是广大电子爱好者学习、开发MSP430系列单片机的良好平台。

MSP430F5529共有两类共4个定时器,分别是Timer_A定时器3个和Timer_B定时器1个,按照每个寄存器配备的捕获/比较器的个数分别命名为Timer0_A(内有5个捕获比较器)、Timer1_A(3个)、Timer2_A(3个)、Timer0_B(7个)。

Timer_A定时器3个

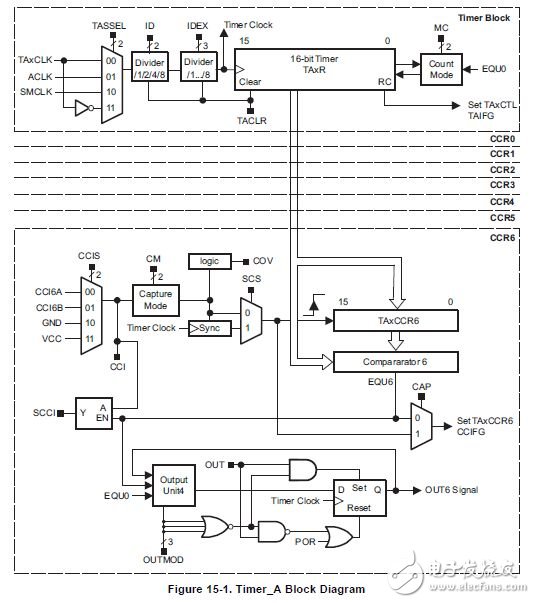

定时器A是一个复合了捕获/比较寄存器的十六位的定时(加减)计数器。定时器A支持多重捕获/比较,PWM输出和内部定时,具有扩展中断功能,中断可以由定时器溢出产生或由捕获/比较寄存器产生。

特征简介:

1、四种运行模式的异步16位定时/计数器

2、自身时钟源可选择配置

3、最多达5个可配置的捕获/比较寄存器(CCR)

4、可配置的PWM输出

5、异步输入和输出锁存

6、对所有Timer_A中断快速响应的中断向量寄存器

TASSELx :时钟源选择。尽量不要选TASSEL0-TACLK外部时钟源,因为如果TACLK和CPU时钟不同步,很容易出问题。(TA0CLK接P1.0引脚)

00 TACLK 01 ACLK 10 SMCLK 11 ~TACLK

IDx:第一次分频控制。ID0-1分频;ID1-2分频;ID2-4分频;ID3-8分频

MC:工作模式控制。(建议在修改定时器运行模式前先停止定时器(中断使能、中断标志、TACLR例外),以避免产生未知的误操作。)

00 停止模式:定时器停止 01 增模式: 定时器计数到TACCR0 10 连续模式,定时器计数到0FFFH 11增减模式:定时器加计数到TACCR0然后减计数到0000H

TACLR:定时器清零位。该位置位会复位TA寄存器,时钟分频和计数方向。TACLR位会自动复位并置0

TAIE:定时器中断使能 0:中断禁止 1:中断允许

TAIFG:中断标志位 0:没有中断发生 1:有中断挂起

计数值存放寄存器TAR

1、显然,最大存放计数值为0xFFFFh;

2、(类似51单片机)可以被用来存放一个初值,然后选用连续模式。这样不断计满再手动填充,从而达到精确计时的效果;

3、默认为0,且对该寄存器可以直接赋值;

扩展寄存器TAEX0

很简单,这个寄存器就是为了控制时钟源的二次分频。

该寄存器的低3为定义为TAIDEX:000-111分别表示1-8分频

捕获/比较寄存器TACCR0-TACCR4(共5个)

比较模式下,用来设定计数终值;

捕获模式下用来将捕获的TAR值存放进TACCRx中。

MC控制的四种工作模式的详细讲解

MC=0停止模式

这是系统默认的模式,定时计数器禁止工作。

MC=1增模式

1、此模式下严禁从0xffff开始计数;

2、注意从0计到TACCR0,实际上记了TACCR0+1个数;

3、计到TACCR0后,会回到0重新开始计数;

4、如果TAR的值大于TACCR0,这时候会立即从0开始计数;

5、当定时器计数到TACCR0的值时,中断标志CCIFG位(之后会讲到)置位。当定时器由TACCR0返回0时,TAIFG中断标志置位;

6、在定时器运行时修改TACCR0,如果新的周期值大于或等于旧的周期值,或大于当前的定时器计数值,那么定时器立刻开始执行新周期计数。如果新周期小于当前的计数值,那么定时器回到0。但是,在回到0之前会多一个额外的计数。

MC=2连续模式

在连续模式中,定时器重复计数到0FFFFH,然后重新从0开始增计数(除非每次重装计数初值)。当定时器从0FFFFH到0时,TAIFG中断标志置位。

应用:连续模式下利用捕获/比较器产生需要的时间间隔。原理是:计数在一直进行,捕获器TACCRX中存有第一个计数终值,每次捕获器计到TACCRX时,会产生中断标志,我们可以在中断服务函数中写入一个计算好的下一个的计数终值,这样无限计算和中断下去,那么该捕获器就会产生一个稳定的时间间隔序列。(其实吧,不明白也没关系。就算明白了,也不好用,因为计算起来很麻烦而且也不好用)

MC=3增减模式(常用于生成PWM波)

1、该模式下,计数方向是固定的,即让定时器停止后再重新启动定时器,它就沿着停止时的计数方向和数值开始计数。如果不希望这样,就需要将TACLR置位来清除方向。TACLR位也会清除TAR的值和定时器的时钟分频。

2、当定时器运行时,改变TACCR0的值,如果正处于减计数的情况,定时器会继续减到0,新的周期在减到0后开始。 如果正处于增计数状态,新周期大于等于原来的周期,或比当前计数值要大,定时器会增计数到新的周期;如果新周期小于原来的周期,定时器立刻开始减计数,但是,在定时器开始减计数之前会多计一个数。

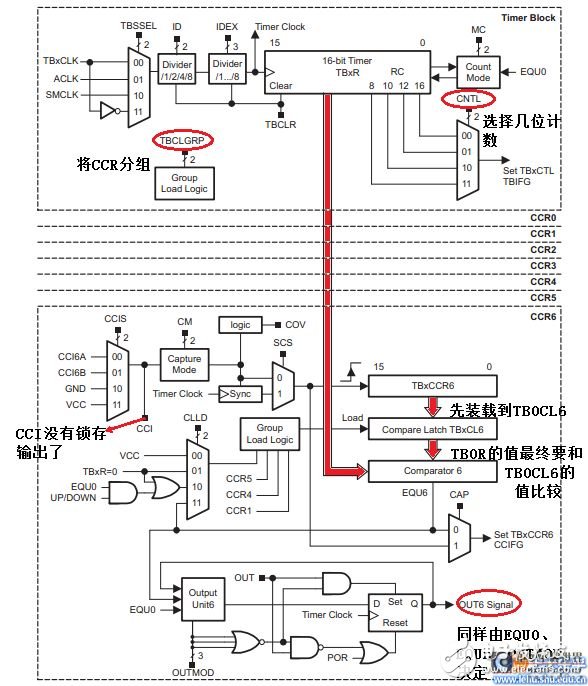

Timer_B定时器1个

定时器B的简介

Timer_B定时器特性:

(1) 16位同步定时/计数,4种工作模式可选、4中长度可选;

(2) 可选可配置时钟源;

(3) 高达7个捕获/比较寄存器;

(4) 可配置PWM输出;

(5) 带有同步装载的双缓冲比较寄存器;

与定时器A的比较(相同点与不同点)

(1) TB的计数长度可以选择(8、10、12、16BITS),而TA只有16位;

(2) TB0CCRn寄存器是双缓冲的,且可以分组;

(3) 所有的TB输出可以被设为高阻状态;

(4) TB没有SCCI,即捕获器输入信号CCI没有被锁存;

(6) 快速解码的中断向量;

Timer0_B寄存器介绍及设置

声明:所有寄存器同样支持字和字节操作

所有寄存器初始化都为0x0000

TB控制寄存器TB0CTL(最常用最基本)(和TA有一点不同)

rw-(0)表示默认读写均为0

TBCLGGRP:TB0CLn分组控制

00:每个TB0CLn独立使用

01:TB0CL1+TB0CL2作为一组(TB0CCR1的CLLD位控制整组数据更新)

TB0CL3+TB0CL4作为一组(TB0CCR3的CLLD位控制整组数据更新)

TB0CL5+TB0CL6作为一组(TB0CCR5的CLLD位控制整组数据更新)

10:TB0CL1、2、3一组,(TB0CCR1的CLLD位控制整组数据更新)

TB0CL4、5、6一组,(TB0CCR4的CLLD位控制整组数据更新)

11:TB0CL0、1、2、3、4、5、6整合为一组,

(TB0CCR1的CLLD位控制整组数据更新)

CNTL:计数器长度控制

00 16位,即最大可以计到0FFFFh

01 12位,即最大可以计到0FFFh

10 10位,即最大可以计到03FFh

11 8位,即最大可以计到0FFh

TBSSEL :时钟源选择。尽量不要选TACLK外部时钟源,因为如果TACLK和CPU时钟不同步,很容易出问题。(TB0CLK接P7.7引脚)

00 TBCLK

01 ACLK

10 SMCLK

11 ~TBCLK

ID:第一次分频控制。ID0-1分频;ID1-2分频;ID2-4分频;ID3-8分频

MC:工作模式控制。(建议在修改定时器运行模式前先停止定时器(中断使能、中断标志、TACLR例外),以避免产生未知的误操作。)(和TA一样)

00 停止模式:定时器停止

01 增模式: 定时器计数到TB0CCR0

10 连续模式,定时器计数到0FFFH(16位)…12位、10位…

11增减模式:定时器加计数到TB0CCR0然后减计数到0000H

TBCLR:定时器清零位。该位置位会复位TA寄存器,时钟分频和计数方向。

TACLR位会自动复位并置0

TBIE:定时器中断使能

0:中断禁止

1:中断允许

TBIFG:中断标志位

0:没有中断发生

1:有中断挂起

计数值存放寄存器TB0R

扩展寄存器TBEX0

很简单,这个寄存器就是为了控制时钟源的二次分频。

该寄存器的低3为定义为TBIDEX:000-111分别表示1-8分频

捕获/比较寄存器TBCCR0-TBCCR6(共7个)

比较模式下,用来设定计数终值;

捕获模式下用来将捕获的TBR值存放进TBCCRx中。

捕获/比较控制寄存器TB0CCTL0-TB0CCTL6:

CM:捕获模式设定 00 不捕获

01 上升沿捕获

10 下降沿捕获

11上升和下降沿都捕获

CCIS:捕获源的选择 00 CCIxA

01 CCIxB

10 GND

11 VCC

SCS:同步捕获源,设定是否与时钟同步

0 异步捕获

1 同步捕获

CLLD:比较寄存器缓冲装载模式选择。

00 TB0CCRn的值(改变时)立即装载到TB0CLn

01 当TB0R的值计到0时,进行装载

10 增模式或者连续模式下,TBR0值计到0时,进行装载 ;

增减模式下,TBR0计数到TBCL0时,开始装载;

11 TBR0计数到TBCL0时,开始装载;

CAP: 0-比较模式 1-捕获模式

OUTMOD:输出模式控制位。同TA一模一样

CCIE:中断使能,该位允许相应的CCIFG标志中断请求 。

0-中断禁止 1 -中断允许

CCI :捕获比较输入,所选择的输入信号可以通过该位读取

OUT : 对于输出模式0,该位直接控制输出状态 。

0-输出低电平 1-输出高电平

COV:捕获溢出位。该位表示一个捕获溢出发出,COV必须由软件复位。

0-没有捕获溢出发生 1-有捕获溢出发生

CCIFG:捕获比较中断标志位。

0-没有中断挂起 1-有中断挂起

中断向量寄存器TB0IV

同TAIV一样,里面存放一个数字编号。

TB和TA的不同之处

没有再把CCI信号锁存了

TA作捕获器的时候,CCI为捕获信号,然后CCI被锁存输出 为SCCI;

但是,TB没有锁存。也就是说只能从CCI位查看输入信 号了。

计数值位数可调了(其实无所谓,都可以16位那干嘛不用)

TA的计数值寄存器TAR只能是16位(0XFFFFh);

TB的计数值寄存器TBR可以选择是16、12、10、8位;

两级缓冲比较器(比较模式下)

TA里面,我们在TACCRn中写入要比较的数值,然后让TAR中的计数值和TACCRn比较,如果相等了,相应的标志位就会置位;

TB里面,不仅有TB0CCRn,还多了一个二级缓存器TB0CLn。TB0CLn不能被直接进行操作,它的值只能来源于TB0CCRn。计数的时候,TB0R中的计数值不和TB0CCRn比较,而是和TB0CLn进行比较。

二级缓冲是为了防止我们在修改TB0CCRn的值的时候,对计数产生影响。因为计数器不直接和TB0CCRn比较,而是TB0CCRn把值赋给TB0CLn,由TB0CLn去和TB0R进行比较。所以也就有了CLLD位控制比较寄存器缓冲装载模式:(当向TB0CCRn中重新写数时)

00 TB0CCRn的值立即装载到TB0CLn

01 当TB0R的值计到0时,进行装载

10 增模式或者连续模式下,TBR0值计到0时,进行装载 ;

增减模式下,TBR0计数到TBCL0时,开始装载;

11 TBR0计数到TBCL0时,开始装载;

比较器可以被分组

TA没有二级缓冲寄存器,而且本来的TACCRn也只能被单 独使用。

对于TB:

TBCLGGRP:TB0CLn二级缓冲寄存器分组控制

00:每个TB0CLn独立使用

01:TB0CL1+TB0CL2作为一组(TB0CCR1的CLLD位控制整组数据更新)

TB0CL3+TB0CL4作为一组(TB0CCR3的CLLD位控制整组数据更新)

TB0CL5+TB0CL6作为一组(TB0CCR5的CLLD位控制整组数据更新)

10:TB0CL1、2、3一组,(TB0CCR1的CLLD位控制整组数据更新)

TB0CL4、5、6一组,(TB0CCR4的CLLD位控制整组数据更新)

11:TB0CL0、1、2、3、4、5、6整合为一组,

(TB0CCR1的CLLD位控制整组数据更新)

所谓的分组,就是该组的数据要同时更新。

以10模式下的TB0CL1、2、3这组为例:

TB0CCTL1中的CLLD设置为01,即TB0R计数到0时,TB0CCR1就会把值装载(更新)到TB0CL2中,同时TB0CCR2就会把值装载(更新)到TB0CL2中,同时TB0CCR3也会把值装载(更新)到TB0CL3中。无论TB0CCRn中的值有几个发生了变化,但它们都只会同时更新TB0CLn。

- 相关推荐

- 热点推荐

- 定时器

- MSP430F5529

-

MSP430F5529 DriverLib 库函数学习笔记(七)定时器B2021-12-04 1294

-

MSP430F5529常用定时器寄存器有哪些呢2021-11-29 869

-

MSP430F5529驱动0.96寸OLED显示2021-11-20 1339

-

MSP430F5529常用定时器2021-11-19 888

-

MSP430F5529程序整理(串口、AD、定时器等)2019-11-25 2998

-

MSP430F5529 Device Erratasheet2017-12-08 1290

-

msp430f5529原理图2017-10-23 34532

-

msp430f5529数据手册2016-02-16 1688

-

msp430f5529例程2016-01-19 2304

全部0条评论

快来发表一下你的评论吧 !