常用时序约束使用说明-v1

描述

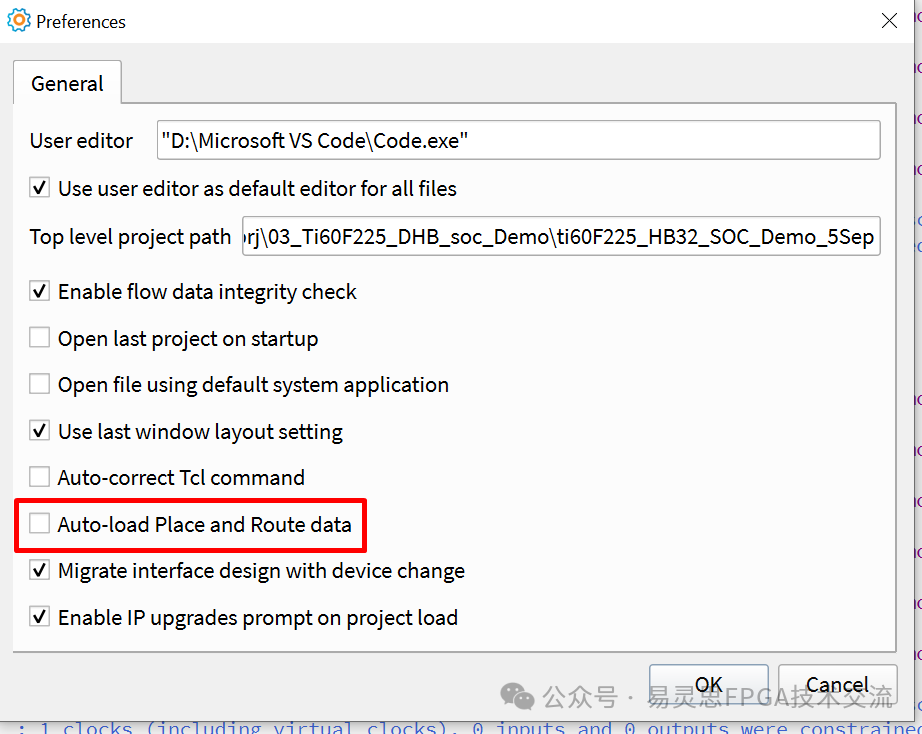

为了节省每层导入网表的时间,在设置中我们通常不会勾选Aoto Load place and route Data 前面的勾选框。这样每次编译完成之后Show/Hide Tcl Command Console菜单项是灰色的。

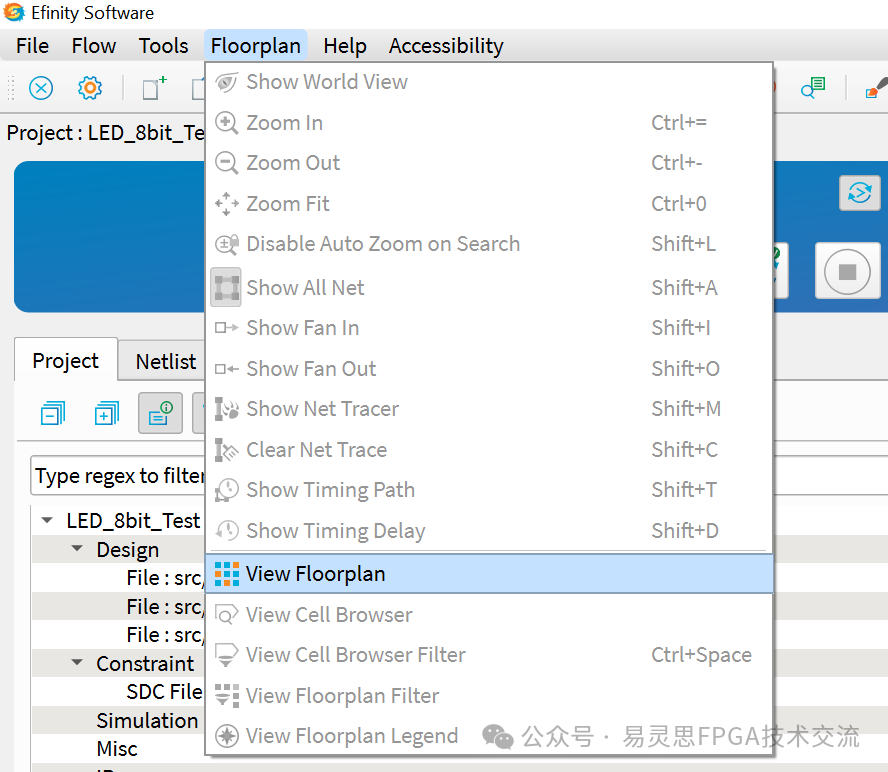

第一步要先加载见表数据。Floorplan-->View Floorplan。

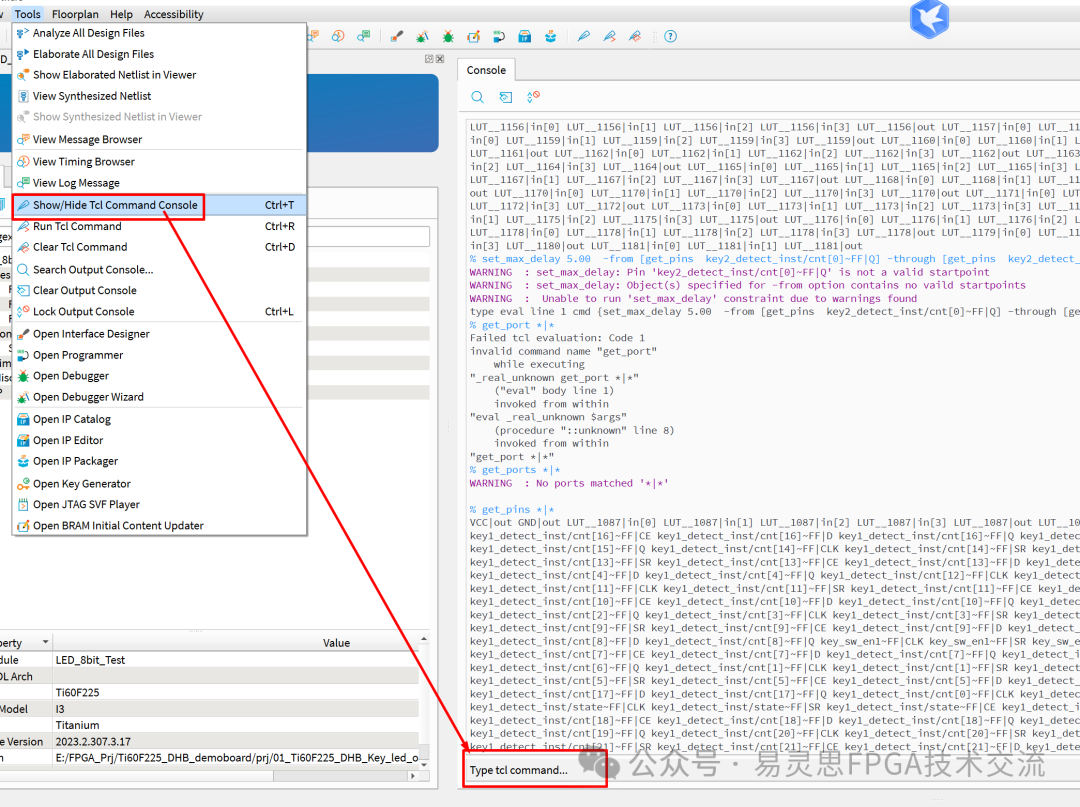

这时再次打开Tools--> Show/Hide Tcl Command Console,在Console最下面就会出现命令输入框。

TCL操作命名

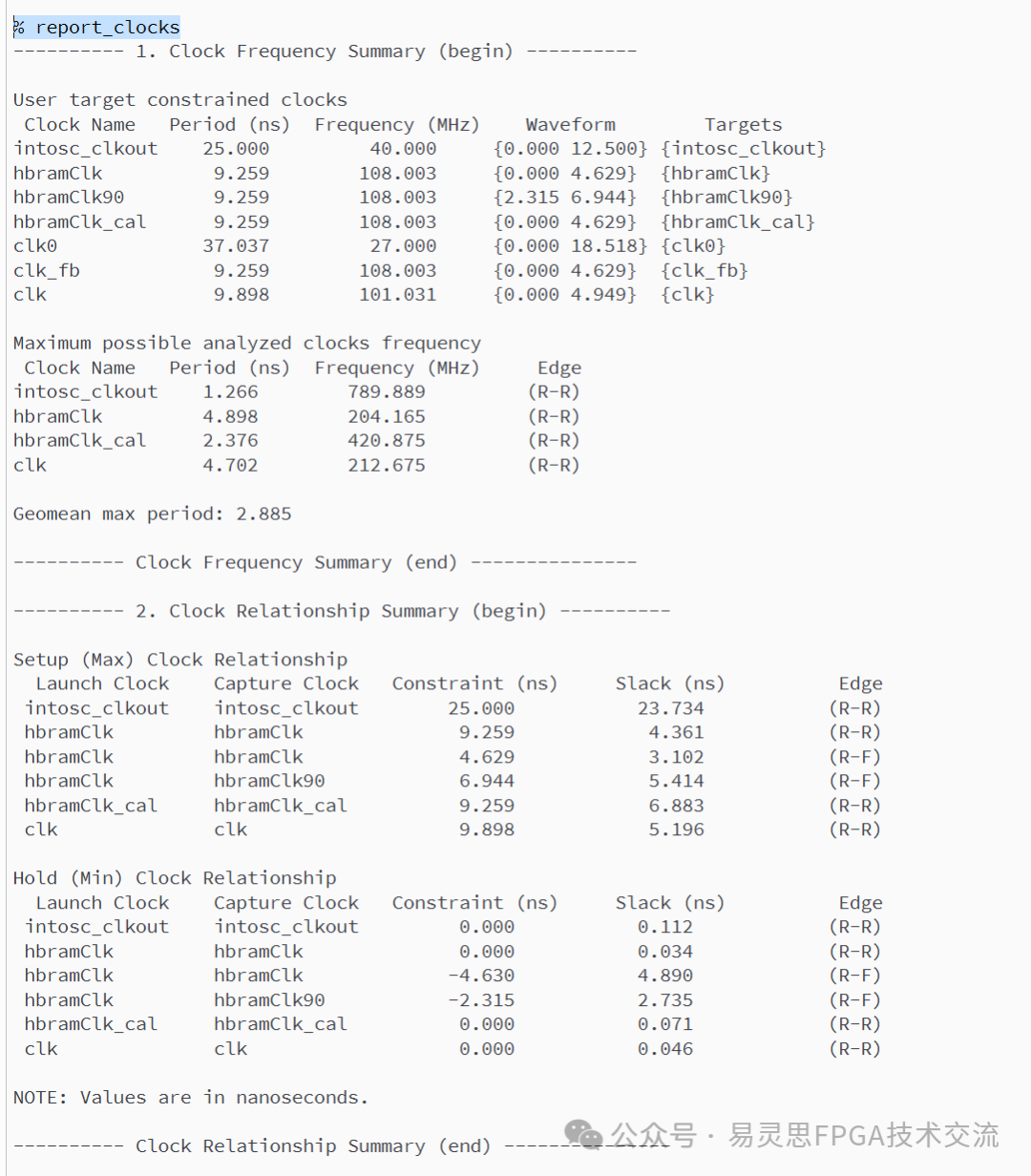

report_clocks会报告所有的时钟关系

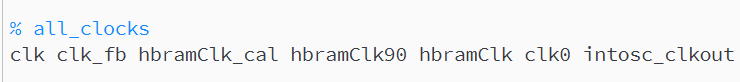

all_clocks 把系统使用的时钟报告出来

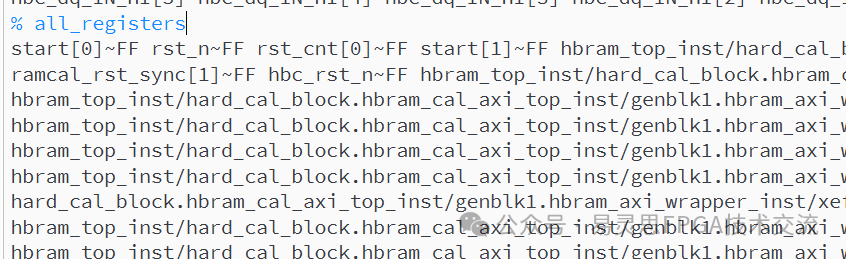

all_registers可以查看所有的寄存器的完整路径

all_inputs/all_outputs 可以查看输入输出端口

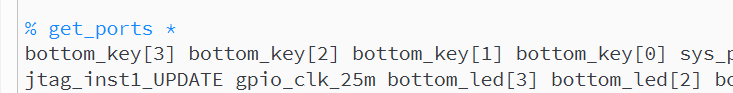

get_ports *

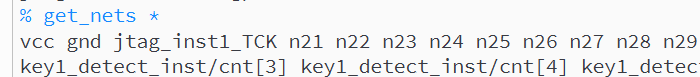

get_nets *

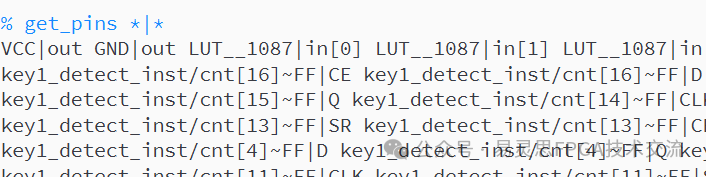

get_pins *|*

get cells *

===========================================

set_max_delay(set_min_delay)

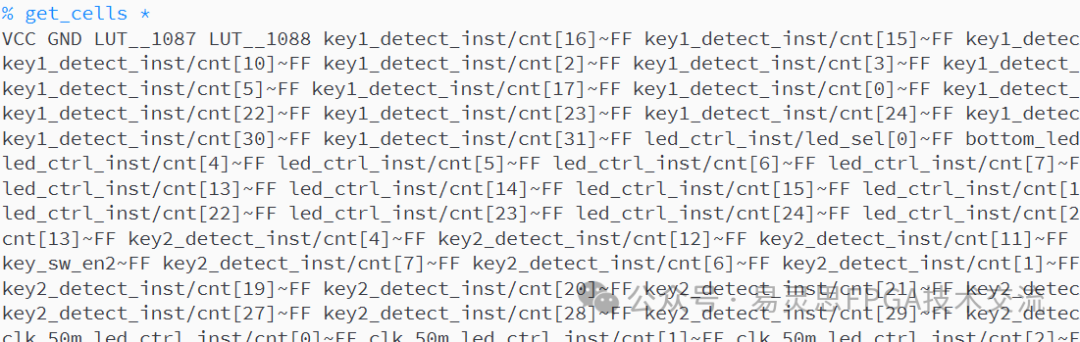

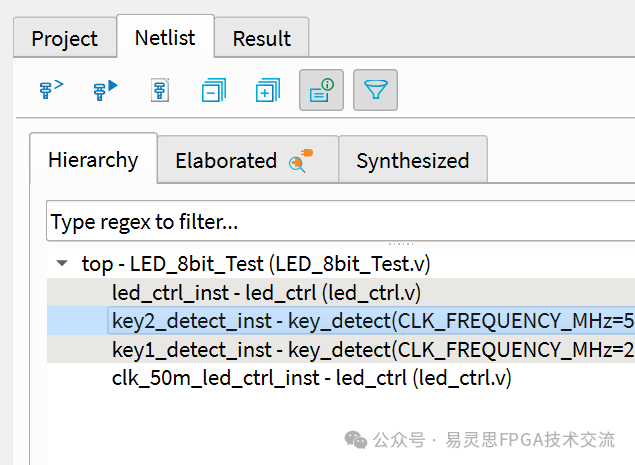

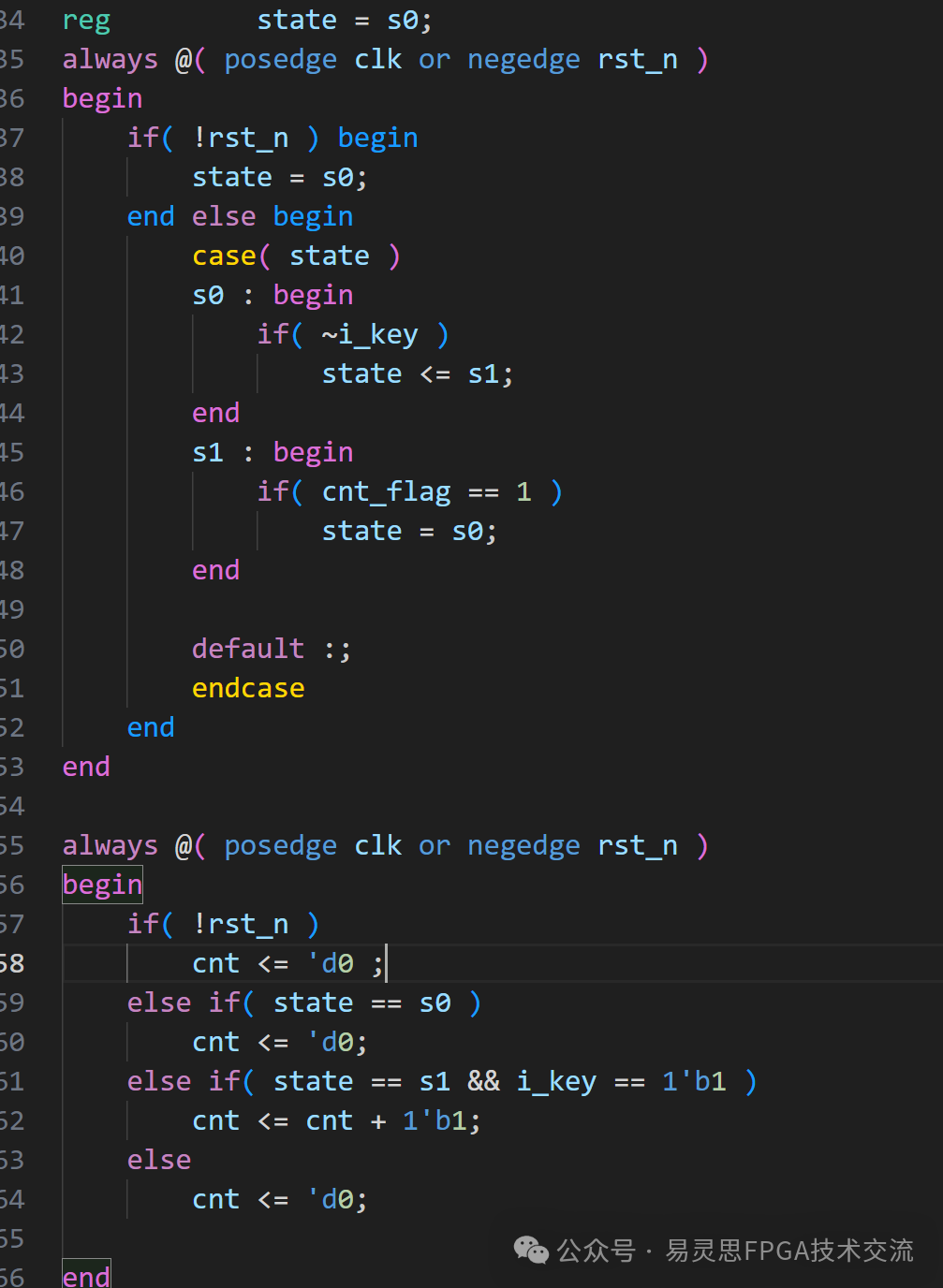

首先看到文件的层次结构是下面的

路径在key2_detect_isnt中。代码如下,如果我们想看state到cnt的路径

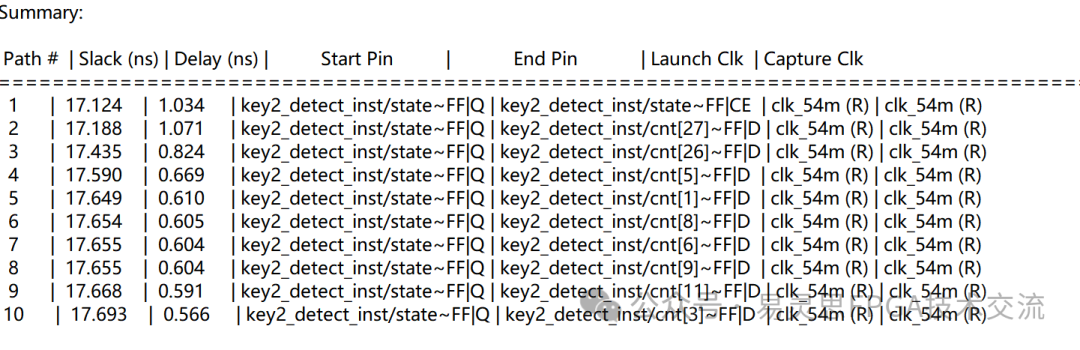

打印10条路径,以第一条为例

report_timing -from key2_detect_inst/state* -file timing_test.txt -npaths 10

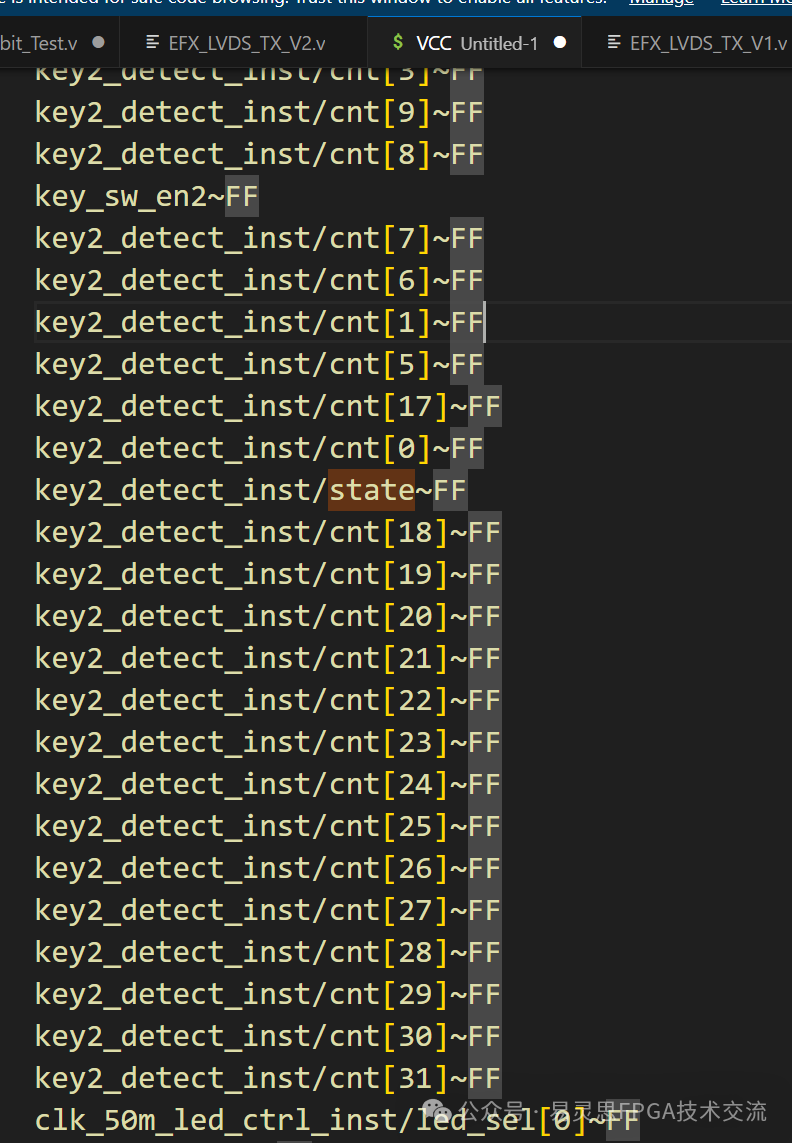

通过get_cells打印所有的cells,并通过空格转回车清晰显示。

% get_cells key2_detect_inst/state~FF

key2_detect_inst/state~FF

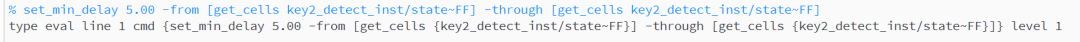

为了防止约束失败,我们在Tcl输入框中验证,没有告警或者错误说明约束的写法是正确的

set_max_delay 5.00 -from [get_cells key2_detect_inst/state~FF] -through [get_cells key2_detect_inst/state~FF]

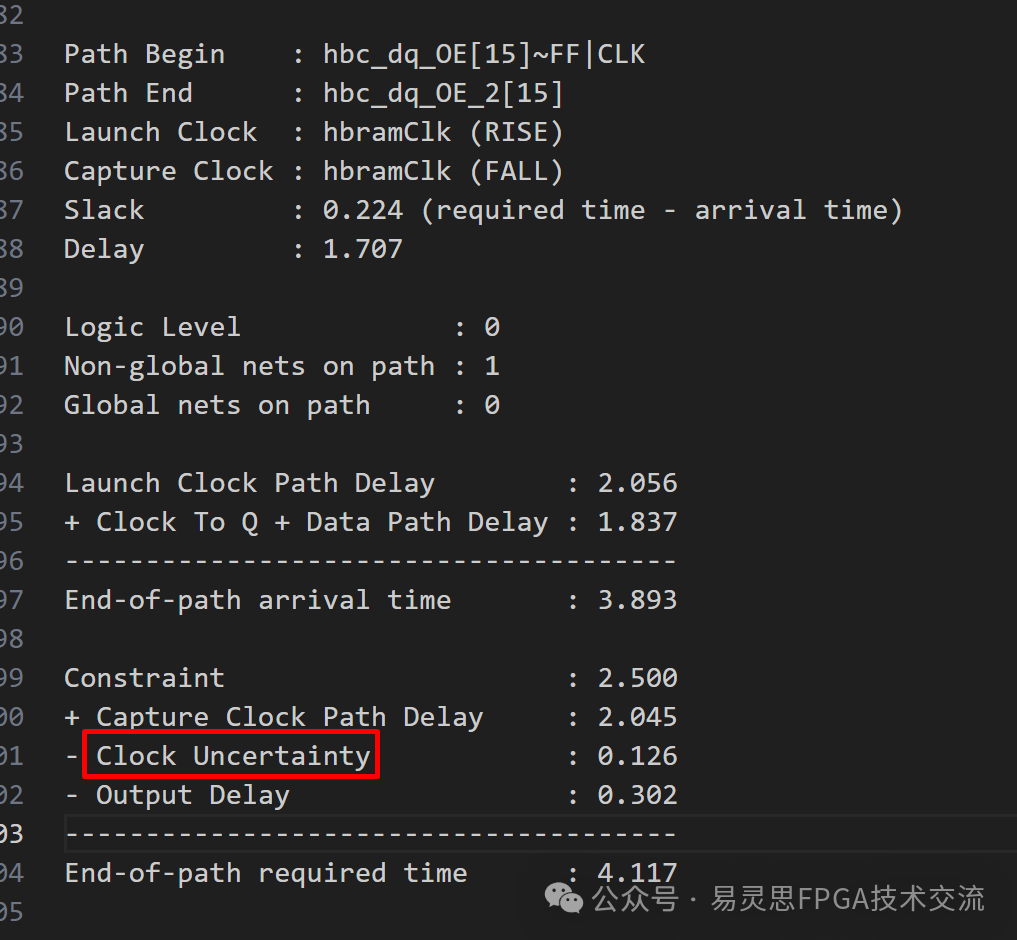

Set Clock Uncertainty

器件本身对Uncertainty是有默认的约束值的。打开timing.rpt文件就可以看到相应的约束值。

我们可以通过set_clock_uncertainty加大约束值,以上面为例,默认是120ps的uncertainty,通过下面的约束之后变成了180ps。

set_clock_uncertainty -to clk -setup 0.06

原文标题:常用时序约束使用说明-v1

文章出处:【微信公众号:易灵思FPGA技术交流】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

vivado中常用时序约束指令介绍2026-01-20 636

-

WTN6系列语音芯片使用说明书V12025-03-06 569

-

Xilinx FPGA编程技巧之常用时序约束详解2024-04-12 2202

-

常用时序约束介绍之基于ISE的UCF文件语法2022-12-28 5591

-

航芯通用处理器BOOT下载工具使用说明_v12022-09-02 762

-

Xilinx的时序设计与约束资料详细说明2021-01-14 1732

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2885

-

如何使用时序约束向导2018-11-29 3683

-

Xilinx FPGA编程技巧常用时序约束介绍2018-07-14 5485

-

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果2017-11-24 6124

-

nikon相机使用说明(Nikon 1 V1)2012-05-08 3273

-

步步高数码随身听V1型使用说明书2010-12-30 2194

-

时序约束与时序分析 ppt教程2010-05-17 947

全部0条评论

快来发表一下你的评论吧 !