88e6060引脚数据

通信芯片

描述

88e6060简介

Marvell®88 e6060单个芯片上集成一个完整的6-port快速以太网交换机支持一个CPU连接。它包含五10 base - t / 100 base-tx收发器(物理),两个可以用来支持100 base-fx;六个独立的快速以太网介质访问控制(mac)、高速非阻塞开关结构,高性能地址查找引擎和1/2 m帧缓冲mem-ory。它是专为厂商低端口计数开关系统和防火墙的路由器。

PHY收发器的设计和Marvell Vir-tual电缆测试仪™(VCT™)技术先进的电缆诊断。VCT使IT经理可以很容易确定布线问题到一米的位置,减少网络安装和支持成本。

Marvell 88E6060被设计成在所有环境下工作,在PHYs的自动跨界、自动极性和自动谈判中支持真插即用,以及桥环路的预防(使用跨越树支持的端口状态)。基于共享的基于内存的交换结构采用了最晚的Marvell switch架构,在所有的交通环境中提供非阻塞的切换性能。

第6个端口,是RMII / MII / MII / MII / SNI接口的接口,可以直接连接到管理或路由器cpu,它可以在RMII模式,MII - phy,MII - mac模式或者是MII - mac模式,或者是MII - mac模式,或者是MII - mac模式,这些接口和BPDU的操作,可以编程的每个端口VLAN配置,和端口状态,支持生成树,真正隔离的WAN和局域网的防火墙应用程序。

在Marvell 88E6060中,使用Marvell先进的混合信号处理技术,实现了自适应均衡和时钟数据恢复的数字实现,采用了特殊的电源管理技术,实现了低功耗和高端口计数的集成,在Marvell 88E6060中,PHY和MAC单元都充分利用了IEEE 802.3、IEEE 802.3 u和IEEE 802. 3x标准的相关部分。

Marvell 88E6060的许多操作模式可以使用SMI(串行管理接口- MDC/ MDIO)和/或低成本串行EEPROM(93C46,C56或C66)配置。

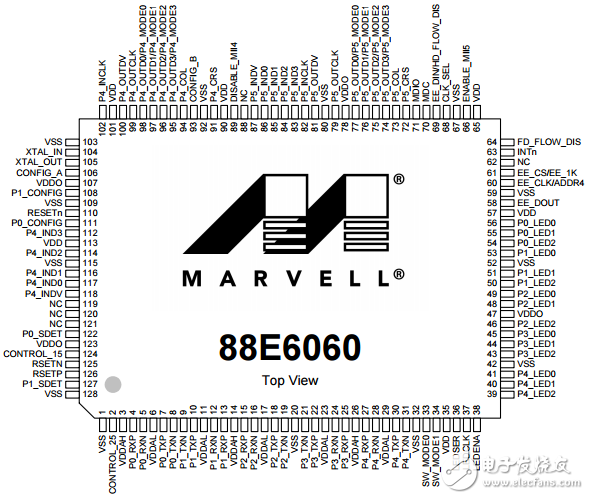

88e6060引脚图

88e6060引脚说明

P[4:0]_RXP:通常输入,在交叉模式是输出。

接受输入的正极,

P[4:0]_RXN:通常输入,在交叉模式是输出。

接受输入的负极,

P[4:0]_TXP:通常输出,在交叉模式是输入。

接受输入的正极,

P[4:0]_TXN:通常输出,在交叉模式是输入。

接受输入的负极,

P[1::0]_SDET:输入

信号检测输入,如果端口0和/或1被配置为100BASE-FX模式,SDET表示光纤收发器的信号是否被检测到,正电平表示的信号被检测到。

如果配置端口0和/或1个10/100BASE-T模式,SDET没有被使用,但不能悬空,因为这些引脚不包含内部电阻器,必须连接到VSS或VDD直接通过一个4.7K的电阻

P[1:0]_CONFIG:输入

端口0和1的配置。CONFIG引脚用于设置端口0和1的默认配置,这些引脚连接到其他设备引脚如下:

VSS =启用自动协商功能 - 默认

P0_LED1=强制10BASE-T半双工

P0_LED2=强制10BASE-T 全双工

P1_LED0=强制100BASE-TX半双工

P1_LED1=强制100BASE-TX全双工

P1_LED2=强制100BASE-FX半双工

VDDO=强制100BASE-FX全双工

端口2,3和4的默认配置是自动协商功能。

CONFIG引脚复位后配置,包含内部下拉电阻,使他们可以悬空来选择自动协商。

CONFIG_A: 输入 悬空的话内部上拉电阻设置为模式3

全局配置引脚:全局配置用于设置默认的LED模式和远端故障指示(FEFI)在100BASE-FX模式下,这些引脚连接到其他设备引脚如下:

VSS= LED模式0,FEFI禁用

P0_LED0= LED模式0,FEFI

P0_LED1= LED模式1,FEFI禁用

P0_LED2= LED模式1,FEFI

P1_LED0= LED模式2,FEFI禁用

P1_LED1= LED模式2,FEFI

P1_LED2= LED模式3,FEFI禁用

VDDO= LED模式3, 默认FEFI启用

CONFIG_A引脚配置复位后,包含内部上拉电阻。

CONFIG_B: 输入

全局配置B,全局配置引脚用于设置的默认自动交叉模式为; VDDO=自动交叉,B类驱动,默认启用能量检测

复位后被配置,内部有一个上拉电阻。

稳压器和参考:

RSETP,RSETN:参考电阻。2kΩ(1%)的电阻器被放置之间的RSETP和RSETN。此电阻器是用来设置一个内部偏置基准电流。

CONTROL_15:

外部1.5V稳压器的电压控制。这一信号控制外部PNP晶体管,以产生1.5V电源为的VDD和VDDAL的引脚。 CONTROL_25:

外部的2.5V稳压器的电压控制。这个信号产生2.5V电源为VDDAH引脚控制一个外部PNP晶体管。

系统:

XTAL_IN:输入 25M晶振

25M或者50M系统参考时钟输入;这个时钟输入频率由CLK_SEL选定。

时钟源可以来自晶体的频率(25 MHz)或振荡发生器(25或50 MHz)。这是唯一的需要,因为它是用于在交换机和PHY的时钟。

XTAL_OUT:输出 25M晶振

系统基准时钟输出。此输出只能被用来驱动一个外部晶体的频率(25 MHz)。它不能被用于驱动外部逻辑。如果振荡器连接到XTAL_IN该引脚应悬空。

CLK_SEL:输出 接VSS

时钟频率选择,该引脚连接到VSS如果XTAL_IN为25 MHz。如果XTAL_IN为50 MHz该引脚连接到VDDO或将其悬空。该引脚必须是稳定的在复位之后。

CLK_SEL是通过一个内部电阻拉高。

RESETn:输入 复位低电平有效

硬件复位。低电平有效。复位时配置的88E6060;

当RESETN为低时,所有的引脚被配置输入和这些引脚上的值在RESETN上升沿或一段时间后的被锁存。

寄存器访问接口:

MDC:管理数据的参考时钟为串行管理接口(SMI)。

预计不会是一个连续的时钟流,支持的最高频率为8.3兆赫。

SMI是用于访问物理层(PHY)和在交换机中的寄存器假如串行EEPROM不能访问寄存器。它可以在所有组合中的SW_MODE[1:0]。

MDC是通过一个内部上拉电阻拉高。

MDIO:输入;

为SMI管理数据输入/输出的。

MDIO是用来传输的管理数据输入和输出与MDC同步;

该引脚需要一个外部上拉电阻,范围在4.7kΩ到10kΩ的范围内。

88E6060设备使用16的32种可能的SMI端口地址。

这个16使用可以选择EE_CLK/ADDR4引脚。

MDIO是通过一个内部上拉电阻拉高。

INTn:开漏极输出;

INTn是一个低电平有效,漏极开路输出引脚, 表示非屏蔽中断事件发生。

当这个信号是无效的,需要一个外部上拉电阻,实现了逻辑高电平。

串行EEPROM接口:

EE_CS/EE_1K:I/O 口, 串行EEPROM芯片选择

EE_CS是通过一个内部上拉电阻拉高。使用一个4.7kΩ电阻到VSS的配置低

EE_CLK/ADDR4 :I/O, 串行EEPROM时钟

EE_CLK是通过一个内部上拉电阻拉高。使用一个4.7kΩ电阻到VSS的配置低。

EE_DIN/HD_FLOW_DIS:通常是输入,

EE_DIN是一个多功能引脚,在硬件复位时用于配置88E6060。当芯片复位时引脚状态被确定,芯片复位时EE_DIN成为输入和配置禁用半双工的流量控制,它的值被锁存于复位的上升沿;

低=使能所有半双工端口的流量控制

高=禁止所有半双工端口的流量控制

EE_DIN是通过一个内部电阻拉高。使用一个4.7kΩ电阻到VSS的配置低。

HD_FLOW_DIS用于选择全双工端口的流量控制

EE_DOUT:输入

串行EEPROM数据从EEPROM器件。

EE_DOUT是串行EEPROM的数据,参考EE_CLK用于接收EEPROM的配置数据从外部串行EEPROM(如果有的话)。

EE_DOUT是通过一个内部电阻拉高

端口5使能:

ENABLE_MII5:输入;

使能端口5MII模式,高电平时使能,低电平禁止,内部上拉电阻拉高;

端口5在MII模式工作:

P5_INCLK:通用I/O口:工作在MAC模式

输入时钟,这个时钟是参考P5_INDV和P5_IND[3:0],P5_INCLK的方向与频率在复位结束后由P5_MODE[3:0]确定; 如果该端口PHY模式,P5_INCLK输出。在100BASE-X模式下的时钟频率为25 MHz, 如果该端口是在10BASE-T模式和50MHz RMII模式时钟频率2.5 MHz。

如果该端口的MAC模式,P5_INCLK是一个输入。在这种模式下的时钟频率可以在任何地方从0Hz到25 MHz的,尽管它应该是为25 MHz100BASE-X模式下和2.5 MHz的10BASE-T模式。

P5_INCLK是在复位期间三态,它有一个内部电阻拉高。

P5_IND[3:0] 输入;

输入数据。P5_IND[3:0]接收的数据半字节被发送到交换机用来选择100BASE-X和10BASE-T模式;

P5_IND[3:0]是同步的P5_INCLK。

这些引脚的输入来自于端口的模式(即模式PHY或MAC模式)。

P5_IND0 SNI模式被选择时使用。

P5_IND[1:0] RMII模式被选择时使用。

P5_IND[3:0]内部上拉电阻高通过。

P5_INDV:输入

输入数据有效。

当P5_INDV被置为高电平,数据P5_IND[3:0]到交换机接受。P5_INDV必须是同步P5_INCLK SNI和MII模式,它必须是同步到P5_OUTCLK或P5_INCLK在RMII模式。

P5_INDV通过内部拉低电阻。

P5_OUTCLK:通用I/O

输入时钟,这个时钟是参考P5_OUTDV和P5_IOUTD[3:0],P5_OUTCLK的方向与频率在复位结束后由P5_MODE[3:0]确定;

如果该端口PHY模式,P5_OUTCLK输出。在100BASE-X模式下的时钟频率为25 MHz,如果该端口是在10BASE-T模式和50MHz RMII模式时钟频率2.5 MHz。

如果该端口的MAC模式,P5_OUTCLK是一个输入。在这种模式下的时钟频率可以在任何地方从0Hz到25 MHz的,尽管它应该是为25 MHz100BASE-X模式下和2.5 MHz的10BASE-T模式。

P5_OUTCLK是在复位期间三态,它有一个内部电阻拉高。

P5_OUTD[3:0]/P5_MODE[3:0]: 通常是输出,仅仅在复位的时候是输入;

输出数据。和交换机传输的数据;

P5_OUTD[3:0]引脚同步到P5_OUT_CLK。

这些引脚是输出端口的模式(即PHY或MAC模式)。

只有P5_OUTD0包含有意义的数据在SNI模式

P5_OUTD[1:0]选择RMII模式1时。

在复位时,引脚的值被锁定来确定工作模式,内部电阻拉高;

P5_OUTDV:输出

输出数据有效。

当P5_OUTDV被置为高电平,数据P5OUTD[3:0]到交换机接受。

P5_OUTDV必须是同步P5_INCLK 在MII模式,在RMII模式下应该同步与P5_INCLK或P5_OUTCLK在;

P5_INDV在复位时是三态模式,通过内部拉高电阻。

P5_CRS:通用I/O

载波侦听。复位后,如果此端口PHY模式选择,P5_CRS的成为输出。

它仍然是输入,如果MAC模式选择。

P5_CRS将置1(或预期置1)当接收数据路径的非空闲。

在半双工模式的传输过程中P5_CRS也被置1(或预计置1)。

P5_CRS是异步到P5_OUTCLK和P5_INCLK的。

P5_CRS是在复位期间三态,它在内部被拉低,因此该引脚果不使用可以悬空

P5_COL:通用I/O

碰撞。复位后,P5_COL的PHY 模式变为输出,如果在MAC模式选择选择此端口。它仍然是输入;

在PHY模式,P5_COL的置1当发送和接收路径是在两个半和全双工模式下非空闲; 在半双工的MAC模式下,P5_COL的将置1非空闲时发送和接收路径。

全双工MAC模式下,P5_COL被忽略。

P5_COL是异步与P5_OUTCLK和P5_INCLK的。

P5_COL是在复位期间三态,它是内部拉低。

端口4使能:输入;

DISABLE_MII4:

禁用端口4,高电平时使能PHY禁止MII,低电平时禁止PHY使能MII;

内部上拉电阻

交换机配置端口:

SW_MODE[1:0] 输出;

开关模式。这些引脚用来复位后配置88E6060。切换模式引脚的工作方式如下:

0 0 CPU连接模式,端口来已禁用

0 1 保留

1 0 单机模式 - 忽略EEPROM

1 1 EEPROM连接的模式2

EEPROM的连接模式(SW_MODE[1:0] =[1,1])可以使用一个CPU。但在所有的独立模式中,INTn脚发出低电平有效在EEPROM初始化内部寄存器完成后,(即停止命令已被执行);

SW_MODE[1:0]的上升沿不锁存的复位和正确的设备操作必须保持静态。他们是通过内部上拉电阻拉高。

FD_FLOW_DIS 输入

全双工流量控制禁用。

高=禁用所有全双工端口的流量控制

低=启用IEEE802.3x暂停的流量控制在所有支持全双工端口

FD_FLOW_DIS到所有端口的PHY寄存器复位的上升沿被锁存。它是通过一个电阻拉高。

EE_DIN/ HD_FLOW_DIS多功能引脚选择半双工端口的流量控制

端口状态灯:

P[4:0]_LED2 输出

每个端口并联LED的输出,低电平有效LED引脚直接驱动的LED在并联LED模式。它 可以被配置为显示多个选项。

P [4:0]_LED2低电平有效无论RESETN是否置1。

P[4:0]_LED1 输出

每个端口并联LED的输出,低电平有效LED引脚直接驱动的LED在并联LED模式。它 可以被配置为显示多个选项。

P [4:0]_LED1低电平有效无论RESETN是否置1。

P[4:0]_LED0 输出

每个端口并联LED的输出,低电平有效LED引脚直接驱动的LED在并联LED模式。它 可以被配置为显示多个选项。

P [4:0]_LED0低电平有效无论RESETN是否置1。

LEDSER:

LEDSER输出串行状态位被移入移位寄存器,可以通过LED显示。LEDSER是的同步输出LEDCLK。

LEDENA:

LEDENA置1不管LEDSER被存储到移位寄存是否具有有效的状态;LEDENA同步于LEDCLK;

LEDCLK:

LEDCLK是LED的串行信号的参考时钟。

- 相关推荐

- 88E6060

-

tda2616引脚功能2007-11-19 4313

-

74ls04引脚图 引脚功能2007-11-29 74196

-

8051引脚图2007-11-29 2515

-

TL082引脚功能2008-03-10 19732

-

62256引脚图2008-04-01 23422

-

62128引脚图2008-04-01 9700

-

7905引脚图2008-05-13 29807

-

cd4051引脚图2008-06-06 9682

-

76810引脚功能2009-04-29 3383

-

Xilinx Spartan 3e cp132引脚说明2016-06-03 1276

-

88E6060原理图_英文资料数据手册pdf下载2016-09-06 4680

-

88E6060原理图数据手册资料2016-09-06 3283

-

88e6060是什么芯片2017-10-24 8253

-

88e6060原理图_88e6060电路图2017-10-24 8219

-

sp3232引脚及功能2023-12-19 11354

全部0条评论

快来发表一下你的评论吧 !