74hc573锁存器怎么用?

电子常识

描述

74HC573是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS器件。

锁存器的最主要作用:

1:缓存、

2:完成高速的控制其与慢速的外设的不同步问题、

3:是解决驱动的问题(提供的电流比51IO口输出电流大)

4:拓展I/O口(可以很猥琐的用锁存器幂叠加方法,即锁存器的Q再接锁存器~ 实现IO口的无限拓展)

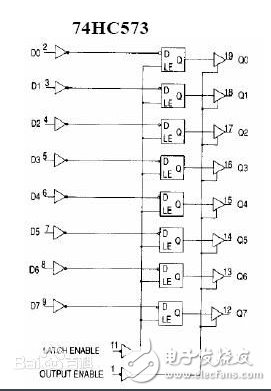

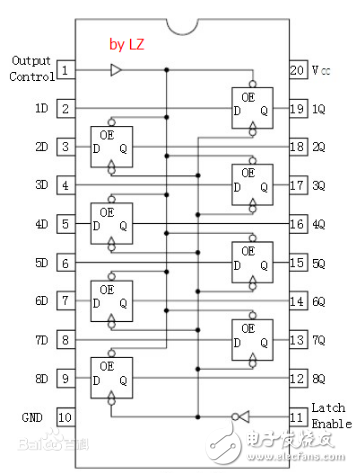

74HC573原理说明:

M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。当使能为低时,输出将锁存在已建立的数据电平上。输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

74HC573锁存器:

输入是和标准 CMOS 输出兼容的;加上拉电阻,他们能和 LS/ALSTTL 输出兼容。

当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

·I/O输出能直接接到 CMOS,NMOS 和 TTL 接口上·

工作电压范围:2.0V~6.0V·

最低输入电流:1.0uA·器件的高噪声抵抗特性·

三态总线驱动输出

·置数全并行存取

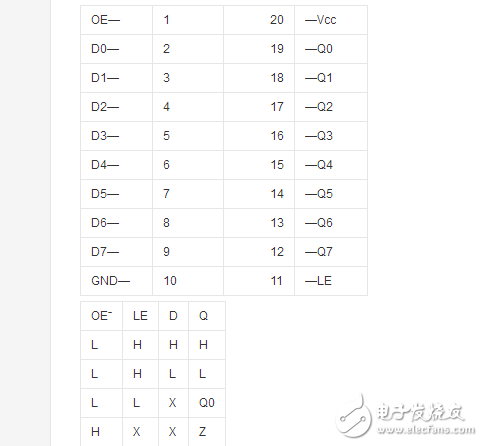

74HC573数据锁存使用:

由上边这个真值表可以看出:OE为高时,输出始终为高阻态,此时芯片处于不可控制状态,所以在一般应用中,我们必须将OE接低电平。

LE则是输出端状态改变使能端,当LE为低电平,输出端Q始终保持上一次存储的信号(从D端输入),当LE为高电平时,Q紧随D的状态变化,并将D的状态锁存。也就是说当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

另外:对锁存器的输入是和标准 CMOS 输出兼容的;若再加上上拉电阻,他们能和 LS/ALSTTL 输出兼容。

-

74HC573锁存器如何控制数码管静态显示?2021-09-29 2106

-

74HC573锁存器简介2021-11-22 32571

-

74HC573锁存器的相关资料推荐2021-11-23 1092

-

74HC573锁存器OE和LE分别是什么?2021-12-07 2416

-

74HC573锁存器相关资料下载2021-12-15 1533

-

简单了解一下74HC573锁存器2022-01-12 1999

-

74HC573锁存器点亮LED2022-01-17 1550

-

74HC573锁存器2015-12-31 1325

-

74hc573芯片是什么类型的芯片?有什么用2017-11-09 198401

-

74hc573是什么_74hc573封装2017-11-27 15643

-

74hc573使用方法(74hc573引脚图及功能_工作原理_封装尺寸及应用电路)2017-12-08 331982

-

74hc573怎么使用 74hc573可以仿真吗2018-07-26 18163

-

74HC573锁存器的中文数据手册免费下载2020-07-16 2202

-

电子器件系列23:74HC573锁存器2021-11-24 1009

-

74HC573:8位D型透明锁存器的详细解析2026-03-13 739

全部0条评论

快来发表一下你的评论吧 !