在IC版图设计中dummy的作用

EDA/IC设计

描述

在IC版图设计中除了要体现电路的逻辑或功能确保LVS验证正确外,还要增加一些与LVS(电路匹配)无关的图形,以减小中间过程中的偏差,我们通常称这些图形为dummy layer。

dummy layer的用途:

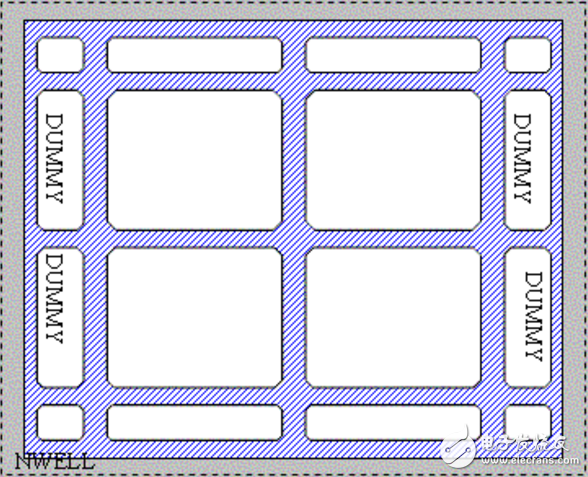

1、保证可制造性,防止芯片在制造过程中由于曝光过渡或不足而导致的蚀刻失败:如在tapeout的时候会检查芯片的density,插入dummy metal、dummy poly、dummy diff等;

2、避免由于光刻过程中光的反射与衍射而影响到关键元器件物理图形的精度进又而影响其size:如在模拟电路的电阻、电容阵列外围加上dummy res和dummy cap等,以及关键MOS附近加dummy MOS等;

3、避免芯片中的noise对关键信号的影响,在关键信号的周围加上dummy routing layer后者dummy元器件:如对于某些易受干扰的信号线除了尽量减小其走线长度外,还应该在其走线的左右和上下都加上dummy metal/poly并接地,保证其不受noise的影响。在cap外围加dummy cap也有类似的作用。

CMOS器件版图中的dummy 图形:

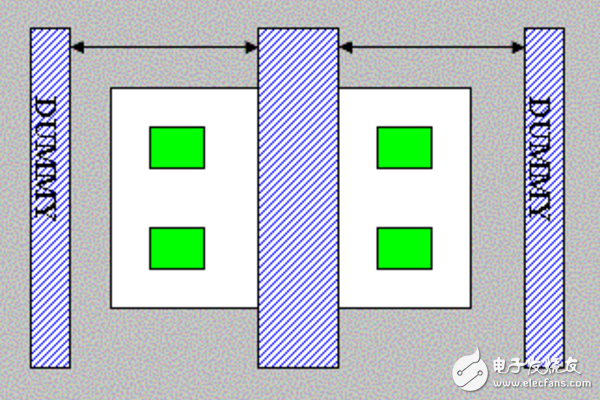

1、MOS dummy

在MOS 两侧增加dummy poly,避免Length受到影响。对NMOS先加P type guard ring 连接VSS,接着加N type guard ring 连接VDD。对PMOS先加N type 连接VDD,接着加P type连接VSS。拆分MOS应为偶数根,Source端与四周guar ring就近连接。比如拆分NMOS为偶数根, 连接VSS的端在外侧并直接与四周guard ring相连。

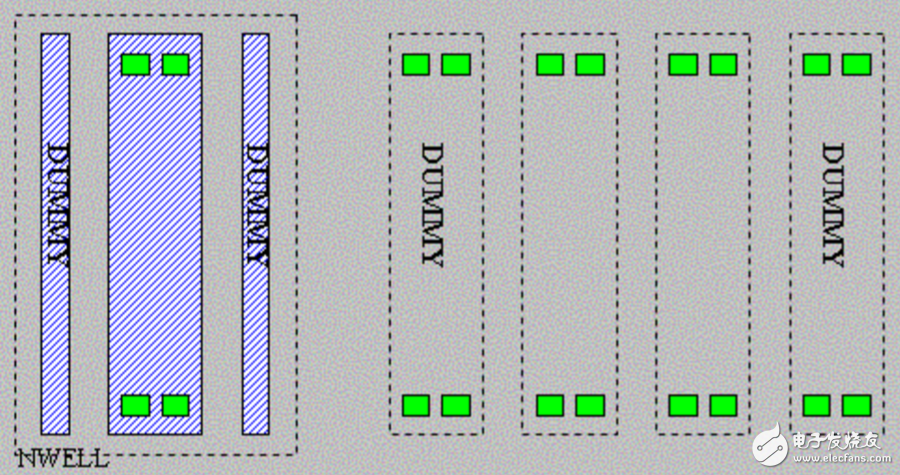

2、RES dummy

类似于MOS dummy方法增加dummy, 有时会在四周都加上。在poly/diff 电阻下面增加nwell 减轻noise 对电阻的影响,nwell连接高电位与sub反偏。Nwell电阻四周加sub cont 连接VSS。Nwell电阻为了降低光照使电阻阻值下降的影响,在上面覆盖metal并连接高电位。其次为给nwell电阻足够的margin 通常nwell宽度5-6um。

3、 CAP dummy

增加dummy方法类似,用Nwell阻挡相自于substrate的noise,Nwell接高电位与sub 反偏。

4、 关键走线与左右或上下走线的屏蔽采用相同层或中间层连接VSS来处理。

-

在模拟版图设计中堆叠MOSFET2021-10-12 2136

-

模拟版图设计和模拟ic设计的区别2020-04-21 10407

-

IC版图设计和PCB版图设计有什么区别详细资料说明2019-03-21 14135

-

请问CSM解密过程中的伪读(dummy read)有什么作用?2018-09-04 5113

-

IC设计的版图绘制、版图验证及版图后仿真的详细资料概述2018-08-07 3538

-

IC工艺和版图设计的电容版图设计的详细中文资料概述2018-06-15 2692

-

浅谈IC设计中的slot和 density2018-06-01 11501

-

C语言中的dummy函数2017-10-24 15600

-

西安急招:模拟IC设计 数字IC设计 版图设计2017-07-13 3853

-

数字IC版图设计公开课2016-06-14 6051

-

IC版图设计工程师-合肥 深圳2015-11-18 3373

-

在cadence ic版图设计中tsmc.18,宽长比4/0.18的mosfet怎么画?2014-10-06 4603

-

江苏招IC版图设计项目经理2012-05-16 2430

-

IC版图设计苏州的有么2012-04-06 2897

全部0条评论

快来发表一下你的评论吧 !