cpld的基本工作原理

简单PLD

6人已加入

描述

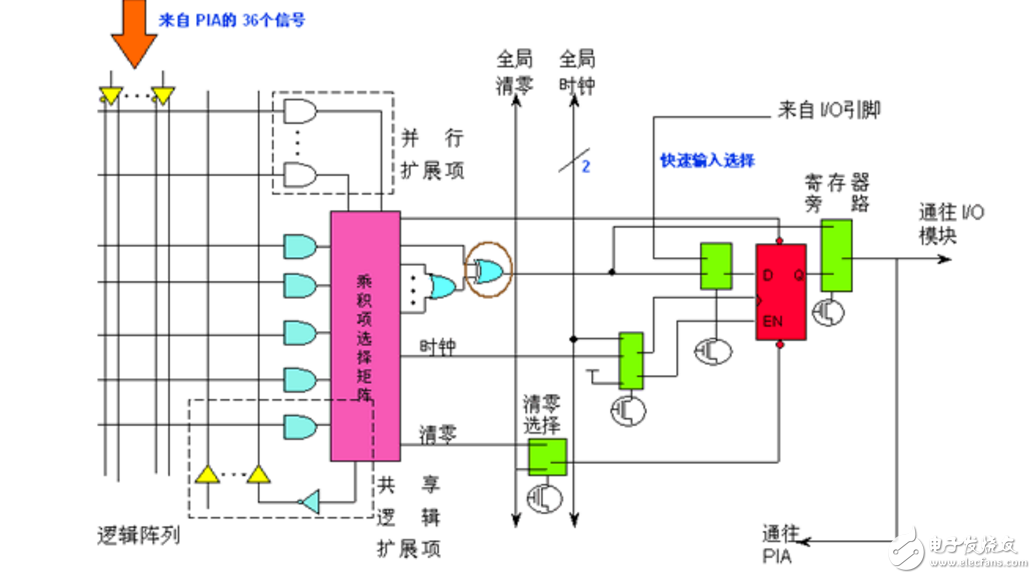

复杂的可编程逻辑器件CPLD( Complex Programmable Logic Device) 规模大,结构复杂,属于大规模集成电路范围。CPLD 由五个主要部分: 逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和I/O控制块。

CPLD器件特点:

它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

CPLD结构与工作原理图:

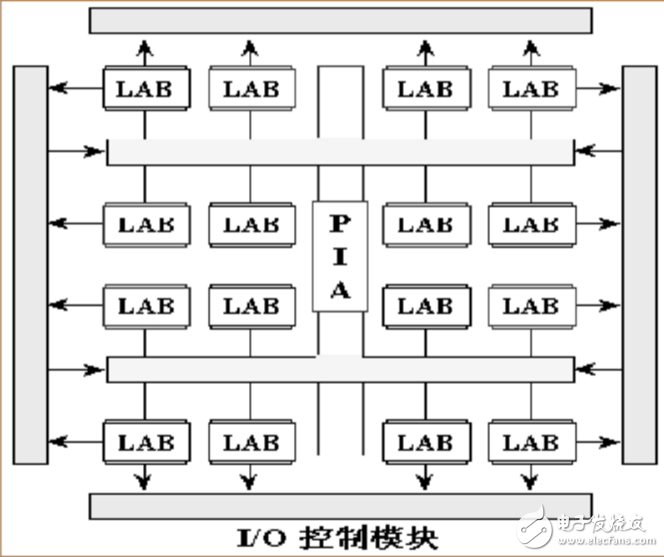

MAX7128S的结构图:

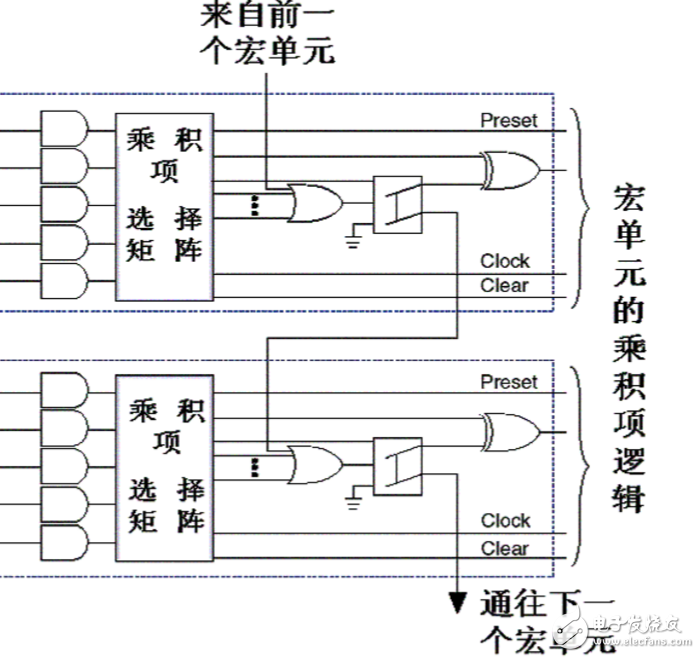

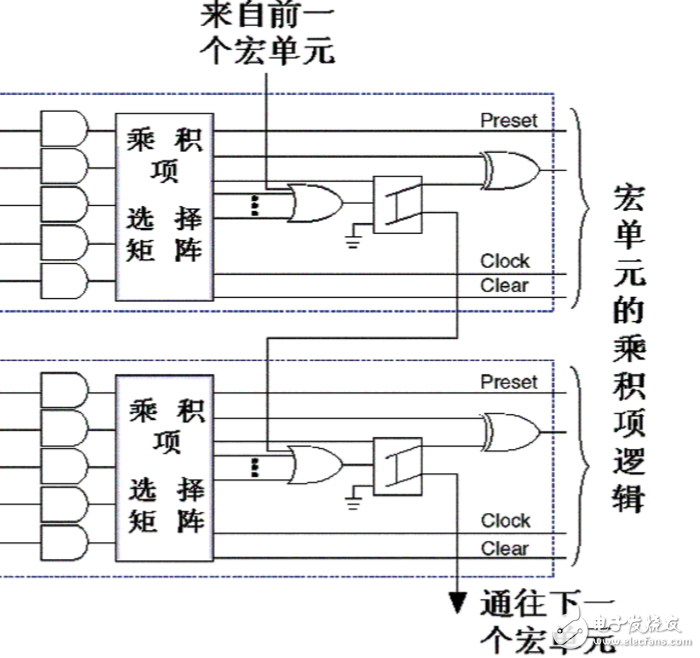

共享扩展乘积项结构图:

并联扩展项馈送方式:

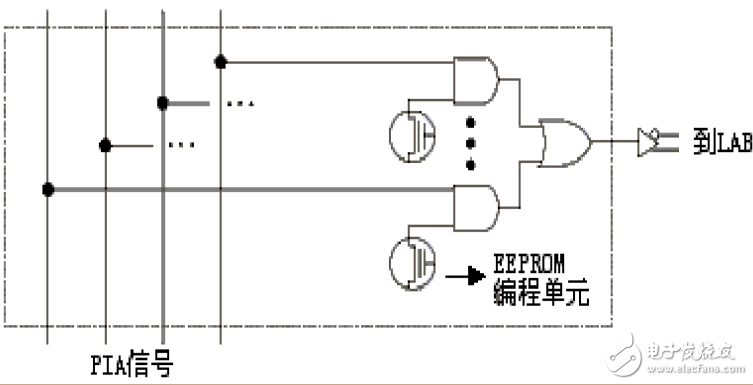

PIA信号布线到LAB的方式:

EPM7128S器件的I/O控制块:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA、CPLD工作原理与简介2022-10-24 2610

-

感光太阳能灯工作原理。#工作原理大揭秘jf_24750660 2022-11-07

-

FPGA、CPLD的工作原理2013-05-08 2855

-

【下载】《从零开始学CPLD和Verilog HDL编程技术》2018-03-30 18142

-

FPGA与CPLD怎么区分2019-07-01 2614

-

FPGA与CPLD该怎么区分?2019-08-08 2047

-

请问如何利用CPLD实现智能数字电压表的设计?2021-04-13 1480

-

LED点阵显示控制系统结构及工作原理是什么2021-04-30 2954

-

三相PFC矩阵变换器电路拓扑及工作原理是什么2021-05-10 4146

-

FPGA与CPLD的辨别和分类2010-10-18 1089

-

基于ARM的嵌入式系统CF卡与CPLD连接技术详解2018-09-18 2338

-

浅析CPLD的工作原理2019-07-12 9406

-

根据结构特点和工作原理来辨别FPGA与CPLD的区别2020-03-24 6302

-

可编程逻辑器件的发展历史,CPLD工作原理与简介2022-12-26 5136

全部0条评论

快来发表一下你的评论吧 !