单总线结构

接口/总线/驱动

描述

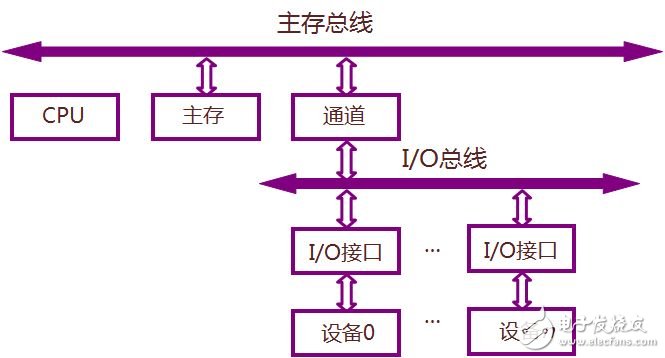

在许多单处理器的计算机中,使用一条单一的系统总线来连接CPU、主存和I/0设备,叫做单总线结构。此时要求连接到总线上的逻辑部件必须高速运行以便在某些设备需要使用总线时能迅速获得总线控制权;而当不再使用总线时,能迅速放弃总线控制权。

单总线结构

单总线主机或从机设备通过一个漏极开路或三态端口连接至该数据线,这样允许设备在不发送数据时释放数据总线,以允许设备在不发送数据时能够释放总线,而让其他设备使用总线。

单总线要求外接一个约5 k的上拉电阻.这样,当单总线在闲置时,状态为高电平。如果传输过程需要暂时挂起,且要求传输过程还能够继续,则总线必须处于空闲状态。

传输之间的恢复时间没有限制,只要总线在恢复期间处于空闲状态(高电平)。如果总线保持低电平超过480 us,总线上的所有器件将复位。另外,在寄生方式供电时,为了保证单总线器件在某些工作状态下(如:温度转换器件、EEPROM写入等)具有足够的电源电流,必须在总线上提供强上拉。

单总线流程:

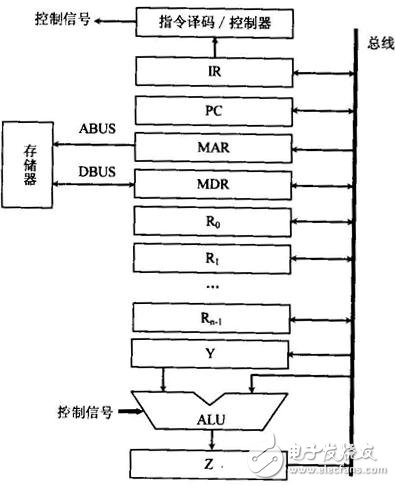

(1)取指令:当CPU取一条指令时,首先把程序计数器PC中的地址同控制信息一起送至总线上。在“取指令”情况下的地址是主存地址,此时该地址所指定的主存单元的内容一定是一条指令,而且将被传送给CPU。

(2)传送数据:取出指令之后,CPU将检查操作码。操作码规定了对数据要执行什么操作,以及数据是流进CPU还是流出CPU。

(3)I/0操作:如果该指令地址字段对应的是外围设备地址,则外围设备译码器予以响应,从而在CPU和与该地址相对应的外围设备之间发生数据传送,而数据传送的方向由指令操作码决定。

(4)DMA操作:某些外围设备也可以指定地址。如果一个由外围设备指定的地址对应于一个主存单元,则主存子以响应,于是在主存和外设间将进行直接存储器传送(DMA)。

(5)单总线结构容易扩展成多CPU系统:这只要在系统总线上挂接多个CPU即可。

- 相关推荐

- 热点推荐

- 单总线

-

一文详解单总线通信技术2022-07-29 10569

-

《计算机组成原理》第三章:系统总线【知识点总结】精选资料分享2021-07-29 1284

-

总线的基本概念及其分类简析2022-02-16 1585

-

Avlon总线规范参考手册2010-02-09 1029

-

Avalon总线规范(中文版)2010-07-09 827

-

avalon总线框架2017-11-21 4940

-

系统总线三种结构的优缺点2020-03-15 32073

-

C51模拟单总线接口的教程详细说明2020-03-25 1499

-

C51模拟单总线接口的详细资料说明2020-03-27 2023

-

[计组原理篇]系统总线2021-12-17 886

-

1553B总线常见三种组网方式2025-06-21 2431

全部0条评论

快来发表一下你的评论吧 !