一文读懂DC/AC SCAN测试技术

AC-DC/DC-DC转换

描述

本文将会根据DC/AC SCAN的概念展开描述,并将他们进行区别对比,让你更加全面的了解DC/AC SCAN测试技术。

SCAN技术,也就是ATPG技术-- 测试std-logic, 主要实现工具是:产生ATPG使用Mentor的 TestKompress和synopsys TetraMAX;插入scan chain主要使用synopsys 的DFT compiler 通常,我们所说的DCSCAN就是normal scan test 即慢速测试,测试频率是10M-30M ,AC SCAN 也就是at-speed scan 即实速测试,测试频率与芯片真实工作频率是一样的。

70年代到1995年这段时间里,由于芯片的工作频率很低只有20-100M,scan测试只有DC SCAN,我们就能捕捉到所有std-logic的制造缺陷。但是1995年以后,测试科学家和工程师发现通过DC SCAN测试没有缺陷的芯片在高工作频率下使用会有问题。其根本原因是随着制造工艺向深亚微米迈进,芯片的工作频率也提高到200M-1G,原来的SCAN测试方法和模型不再能捕捉到所有的std-logic的制造缺陷。大家的一致想法就是-“奔跑吧,SCAN” ,把SCAN的频率增加到与芯片的真实工作频率一致,同时使用新的Transition atpg model来产生测试pattern.

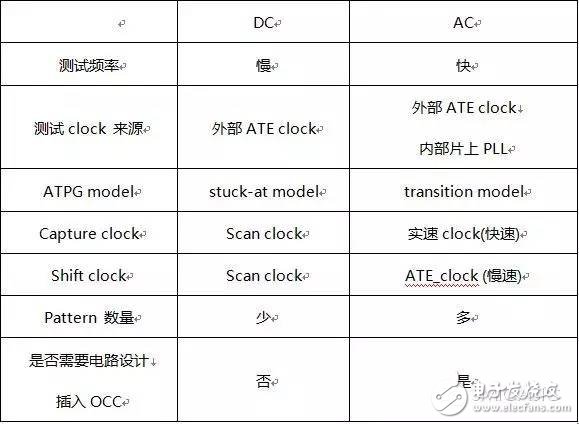

下面我们介绍DC SCAN与AC SCAN的异同

现在的工业量产的高速芯片都会要求能做DC SCAN测试和AC SCAN测试,所以DFT工程师也要同时插入两种测试电路,产生两套测试patterns。

具体实现流程如下

1 读入没有插入scan的网表

2 使用Design compiler 插入scan chain和OCC (on chipclocking)模块,同时插入mux, fix DRC

3 使用Testcompress 实现EDT压缩scan chain

4 使用Testcompress 产生测试DC/ACpattern,同时产生测试验证的Testbench

5 验证DC/AC patterns的正确性和电路的正确性

6 使用SDF,验证DC/ACpatterns相关电路的时序是否满足要求

7 使用DC/AC patterns (wgl文件)转换成ATE所需格式,在ATE上调试和使用

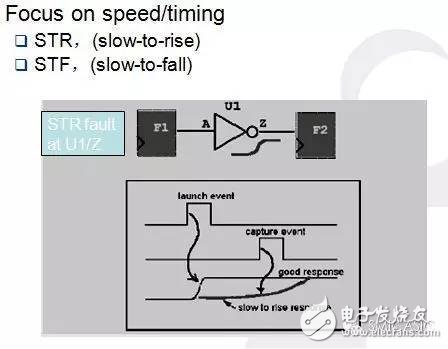

ATPG工具使用的Transition faultmodel如下图

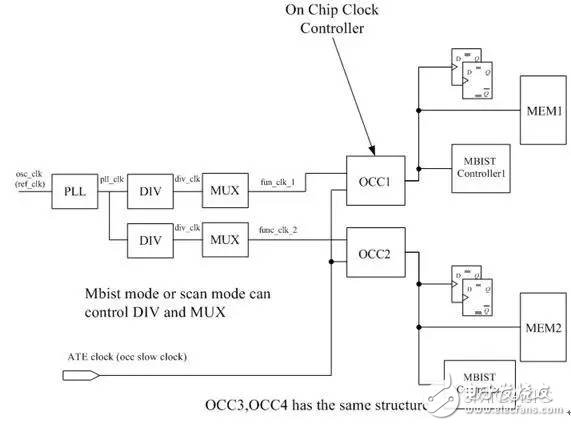

常用的OCC电路结构如下

我们典型的插入OCC以后的电路如下图

-

一文详解AC/DC和DC/DC转换器2022-10-17 3130

-

一文详解AC/DC、DC/DC转换器2023-07-23 2276

-

求助一份AC/DC电源测试解决方案2021-04-13 2161

-

一文读懂接口模块的组合应用有哪些?2021-05-17 2434

-

一文读懂如何去优化AC耦合电容?2021-06-08 3676

-

一文读懂什么是NEC协议2021-10-15 2666

-

一文读懂中断方式和轮询操作有什么区别吗2021-12-10 2732

-

介绍一下AC/DC双向电源技术的优点2023-03-14 2503

-

一文读懂NB-IoT 的现状、挑战和前景2020-02-28 7645

-

一文读懂MCU的特点、功能及如何编写2021-12-05 1355

-

芯片设计测试中scan和bist的区别2023-10-09 6790

-

一文读懂,什么是BLE?2023-11-27 4862

-

一文读懂车规级AEC-Q认证2023-12-04 2178

-

一文读懂单灯控制器工作原理2024-11-11 2724

-

一文读懂AC/DC与DC/DC电源2025-11-17 2326

全部0条评论

快来发表一下你的评论吧 !