什么是CSP封装,CSP封装量产测试的问题及解决方案研究

封装

描述

CSP封装在日益普及的今天,其量产测试中存在的问题也将逐渐显现,其解决办法也多种多样,本文仅对目前测试的主要问题提出一种较为经济的解决方案,此方案经过实际量产测试验证,并取得良好效果,同时也可以应用于其它测试场合,具有比较普遍的实用价值和参考价值。

在当前下游整机厂家对IC封装尺寸及性能的要求日益提高的情况下,无疑,目前的CSP封装以其超小的封装尺寸、优良的散热性能以及较高的性价比,当为众多消费类芯片的封装首选,但是,采用CSP封装,尤其是目前的无铅封装,给产品的量产测试带来了一定的技术难题,本文就CSP封装量产测试的基本方法、测试中存在的问题以及简单经济的解决办法稍做阐述,并举以实例,希望能够对一些正在寻求CSP测试解决方案的工程师能有一些帮助。

1、CSP封装简介

CSP封装,即Chip Scale Package,芯片级封装;也称Chip Size Package,芯片尺寸封装,如图为一9脚的CSP封装的芯片,是最近几年才发展起来的新型集成电路封装技术。应用CSP技术封装的产品封装密度高,性能好,体积小,重量轻,与表面安装技术兼容,因此它的发展速度相当快,现已成为集成电路重要的封装技术之一。目前已开发出多种类型的CSP,品种多达100多种;另外,CSP产品的市场也是很大的,并且还在不断扩大,与其相关的测试也在迅速发展。

2、CSP封装量产测试的基本方法

CSP封装的芯片测试,由于其封装较小,采用普通的机械手测试无法实现,目前主要采用类似晶圆测试的方法,在芯片完成置球封装后,先不做划片,而直接用探针卡进行测试,测试完成后,再实行划片、分选和包装。测试时探针卡固定在探针台上,探针直接扎在CSP封装的锡球上以实现电气连接,然后测试机通过导线施加电压或波形等激励进行测试芯片的相关电气参数,以目前CSP封装应用较多的消费类芯片手机音频功放为例,作详细说明以便大家理解,其功能框图如下:

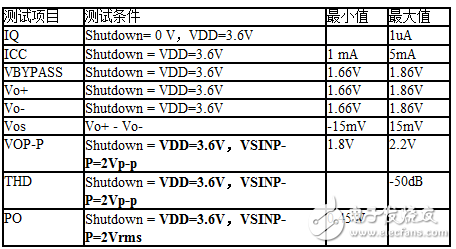

主要测试参数如下:

以上测试参数中主要分直流参数和交流参数,直流参数就是加上相应电压等待稳定后,测量相应管脚的电压、电流即可,相对比较简单,在此不多做说明,对于交流参数VOP-P、THD、PO来说,具体测试方法为:Shutdown = VDD=3.6V,从IN-(IN+端通过40k的电阻接地)端通过40k的电阻输入峰-峰值为VSINP-P=2Vp-p,频率为1KHz的正弦信号。待芯片稳定工作后,差分测量VO+、VO-两端的电压波形幅度值,即可得到波形幅值的峰-峰值VOP-P然后作快速傅立叶变换计算THD。测量PO时只需改变输入正弦信号的幅度为2Vrms,之后测量输出电压有效值U,并通过公式PO=U*U/RL(RL=8.2 Ohm)计算功率大小。针对以上测试参数可选用中低端测试机,如Eagle、ASL1000、V50等均可满足测试需求。

3、CSP封装量产测试中存在的问题

如前所述,CSP封装芯片的量产测试采用类似晶圆测试的方法进行,但是两者的区别在于:晶圆的测试,探针是扎在管芯的PAD(通常情况下为铝金属)上,而CSP封装的测试,探针是扎到CSP封装的锡球上。问题由此产生,在晶圆测试中铝质的PAD对探针污染很小,测试过程中不需要经常对探针进行清洁(一般测试几百上千颗进行在线清针一次即可),而CSP封装的锡球对探针污染非常严重,特别是在空气中放置一段时间后,加重了锡球的氧化,对探针的污染就更为严重,另外流过探针的电流大小也会直接影响探针和锡球之间的电气接触。这样对探针的抗粘粘度及抗氧化能力要求很高,对于一般的探针,测试几十颗就需要对其进行清洁,否则随着沾污越来越严重,会造成探针与锡球之间的接触电阻大到2欧姆以上(一般情况下在0.5欧姆以下),从而严重影响测试结果。

对于本文所举实例而言,在负载电阻仅为8.2欧姆的情况下,这样测试得到的VOP-P及PO值仅为真实值的8.2/(8.2+2+2),既0.672倍左右,从而导致测试的严重失效,同时也会影响到THD测试值。所以在测试过程中需要对探针进行不断的清洁动作,这样在不断的清针过程中,既浪费了测试的时间又加速了探针的老化,导致针卡寿命急剧缩短,同样也会造成测试的误判,需要通过多次的复测才能达到比较可信的测试良率。

在此针对接触电阻稍作说明:

在实际生产测试中,探针的接触电阻在很大程度上取决于PAD的材料、清洗的次数、以及探针的状况。就探针而言,目前主要有钨针和钨铼针两种,其中钨铼合金的探针接触电阻比钨稍高,抗疲劳性相似。但是,由于钨铼合金的晶格结构比钨更加紧密,其探针顶端的平面更加光滑。因此,这些探针顶端被污染的可能性更小,更容易清洁,其接触电阻也比钨更加稳定。所以一般的探针材料均选用钨铼合金。

另外影响接触电阻的关键参数为触点压力,触点压力的定义为探针顶端施加到接触区域的压力,顶端压力主要由探针台的驱动器件控制,额外的Z运动(垂直行程)会令其直线上升,一般情况下,接触电阻会随着压力的增大,探针从开始接触PAD并逐渐深入PAD氧化物,并接触到PAD金属的亚表层而减小,但当压力达到一定的程度后,接触电阻就接本保持不变,此时再增加触点压力会损伤PAD或者芯片内部结构,而导致芯片直接失效。因此,在正常的生产过程中,触点压力的大小有比较严格的控制的,一般表现为探针台设置的OVER DRIVER大小。

4、CSP封装量产测试问题的解决

由以上分析可知,问题的关键在于探针与锡球的接触电阻过大,那么如何才能减小接触电阻或者消除接触电阻的影响呢?通常,工程师们会从探针的角度出发,寻找一种抗沾污能力较强的探针,就目前来讲,这种材料的探针也确实存在,但费用极其昂贵,用其测试低附加值的消费类产品得不偿失;另外一种方法就是采用类似成品量产测试中使用的socket(测试座),这种socket是用贵金属金特殊加工的弹簧针来实现电气接触,从实际的应用的结果来说,效果相对较好,但其价格为普通探针卡的4到5倍,且寿命比一般的针卡短,因此这种方法也只能作为过度所用。

本文所提到的即经济又简单的方法为:借助kelvin的接触方式(或称四线测试方式)来消除接触电阻的影响,所谓Kelvin接触;既对于每个测试点都有一条激励线F 和一条检测线S,二者严格分开,各自构成独立回路;同时要求S 线必须接到一个有极高输入阻抗的测试回路上,使流过检测线S 的电流极小,近似为零,这样在S线上就不会有电压损失,检测出来的电压最为准确。针对本文实例具体做法也非常简单,只需要在VO+及VO-端在原来的基础上多加上一根探针作为测量用,让电流只从另外一根探针上流过,这样从这根测试用探针测试出来的电压值就是很准确的输出电压值了,具体可参考下图:

图中r1、r2、r3、r4为接触电阻,上图为采用一根探针时的测量点位置,下图为采用两根探针时的测量点位置,虽然在下图中测量点仍然存在接触电阻,但此时流过接触电阻上的电流非常小,所产生的压降几乎可以忽略不计,所以测试的输出电压更为准确。实践证明这种方案大大提高了测试准确度和测试效率,已经在不同的产品类别中展开应用。

细心的读者可能会发现本文所举的实例比较特殊,因为功放的反馈电阻,即Rf1、Rf2,是集成在芯片内部的,但如果反馈电阻不在芯片内部,而是作为外围元件,那么之前所提到的接触电阻将不会影响输出电压波形幅度的测试,也就没有必要使用两根探针,至于具体原因,读者可自行分析。另外读者可能还会考虑另外一个问题:锡球的大小能否允许同时扎两根探针?对于目前大多数CSP封装的锡球而言,其直径基本在260um左右,间距在500um左右,对于这样大小及间距的情况下,同时扎两根探针是没有问题的。另外也没有必要每个锡球上都扎两根针,而仅仅是在对接触电阻比较敏感的锡球采用此种方式即可,这样也不至于过多的使用探针而导致成本的提高。

本文所提到的CSP的双针解决方案同样可以应用于晶圆测试中,但有一个条件必须满足:那就是PAD的尺寸大小允许同时扎上两根探针,这需要在设计的时候就要考虑,也就是人们比较熟悉的DFT(design for test)了。 科学技术的研究贵在举一反三,同一种技术可以解决不同的问题,对于本文的方案也并不是一种创新的方案,只是借用了前人所提到的kelvin接触方式而已。另外在此顺便说一句:当你在测试调试中,测试的结果始终没有达到你的理想时,你要考虑一下测试原理图中不存在的,但在实际的硬件电路中又的的确确存在的东西,那就是电路中寄生的电阻、电容、电感等无形元件,本文实例中影响测试结果的只是寄生的电阻,但在其他的项目中影响结果的可能就是这几种的组合,这时就需要你扎实的电路基础来分析了。

-

详解CSP封装的类型与工艺2025-07-17 3135

-

CSP 封装布线2016-06-29 4652

-

可以解决众多封装难题的CSP-ASIP2018-11-23 2635

-

TVS新型封装CSP2020-07-30 2502

-

CSP封装内存2009-12-25 800

-

什么是CSP封装2010-03-04 15802

-

CSP封装量产测试中存在的问题2012-05-02 2000

-

倒装芯片CSP封装2017-03-31 2622

-

什么是CSP封装?CSP封装散热这个难题应该如何解决?2018-08-10 16001

-

CSP封装是什么?具有什么特点2019-06-24 21733

-

浅谈CSP封装芯片的测试方法2021-12-03 4001

-

倒装芯片 CSP 封装2022-11-14 833

-

浅析先进封装之CSP和FCCSP2023-03-28 17616

-

CSP封装芯片的测试方法2023-06-03 2488

-

BGA和CSP封装技术详解2023-09-20 4523

全部0条评论

快来发表一下你的评论吧 !