74hc138和74ls138的区别

电子常识

描述

74hc138和74ls138的区别

74hc138的逻辑功能和74ls138是一样的。74hc138是高速CMOS芯片,工作电源电压为2V - 6V,输出端驱动电流为正负25mA。74ls138是TTL芯片,工作电源电压为5V,输出驱动电流高电平-400微安,低电平8mA。从电源电压和驱动电流选的74hc138。

两者功能一样。74HC138采用高速CMOS工艺制作,自身功耗低,输出高低电平范围宽。 74LS138采用早期的双极型工艺,驱动能力相对较大些。

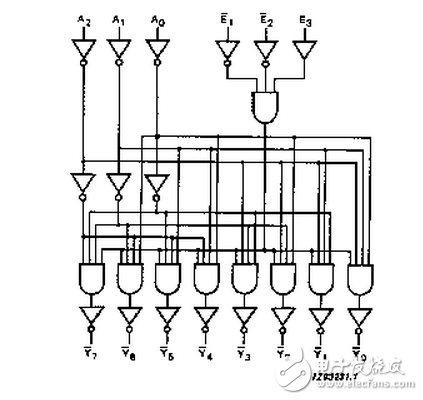

74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

复合使能输入,轻松实现扩展 兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择 低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -40~+85 ℃ -40~+125 ℃ 多路分配功能。

74hc138内部结构图

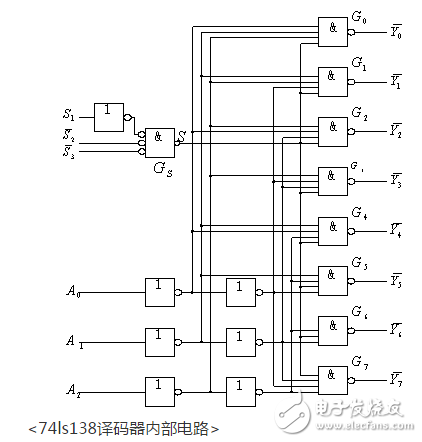

74LS138 为3 线-8线译码器,共有 54LS138和 74LS138 两种线路结构型式。54LS138为军用,74LS138为民用。

①当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

②利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

③若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

④可用在8086的译码电路中,扩展内存。

-

74HC138与74HC573的相关资料分享2021-12-07 2322

-

74hc138电路图汇总分析 74hc138在电路中的作用2018-08-07 31181

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 122455

-

74hc138中文资料详细(74hc138引脚图及功能表_封装真值表及应用电路图)2018-02-02 299732

-

基于74HC138的简单解析2018-01-12 15948

-

74ls138中文资料详解2017-11-03 70887

-

74LS1382016-04-29 4211

-

74HC138芯片资料2015-11-02 2197

-

74ls138真值表_74ls138功能表2011-03-20 10668

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 68023

-

74HC138译码器实验2008-09-22 14203

-

74ls138引脚图-74ls138管脚图及功能真值表2007-12-17 194494

全部0条评论

快来发表一下你的评论吧 !