用74ls138实现一位全减器

数字电路图

134人已加入

描述

用74ls138实现的一位全减器

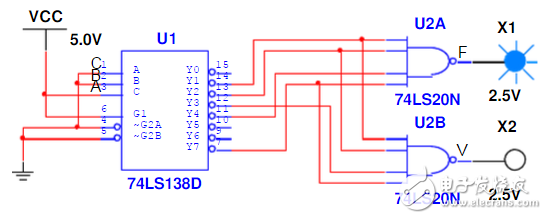

74ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。

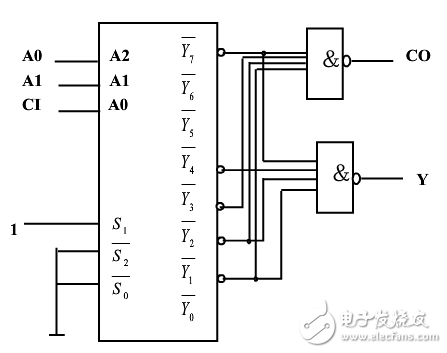

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图所示)。

CO---向高位的借位 Y---两位数之差C1---来自低位的借位

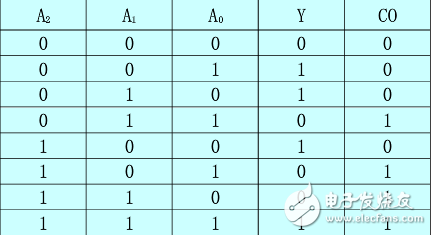

真值表如下:其中A2=A0;A1=A1;A0=C1

故:Y=m1+m2+m4+m7;CO=m3+m5+m6+m7

其逻辑图如下:

74LS138实现全减器电路图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

jf_88222656

2022-11-06

1 回复 举报不会写就不要写,全加器跟全减器都能搞混 收起回复

jf_88222656

2022-11-06

1 回复 举报不会写就不要写,全加器跟全减器都能搞混 收起回复

-

jf_26894157

2022-04-28

1 回复 举报真值表是全加器,电路图是全减器,真的醉了 收起回复

jf_26894157

2022-04-28

1 回复 举报真值表是全加器,电路图是全减器,真的醉了 收起回复

全部评论

-

基于8051的Proteus仿真-74LS138译码器应用2022-05-11 3537

-

74LS138译码器的扩展方法是什么2022-01-19 6628

-

如何对74LS138译码进行实验2021-07-14 6981

-

请问如何用74LS138和与门实现一位全减器2019-10-29 8641

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 122530

-

74ls138中文资料详解2017-11-03 70942

-

74hc138和74ls138的区别2017-10-31 50674

-

74LS138英文手册2016-11-22 1359

-

74LS138 英版数据手册2016-08-29 1570

-

74LS1382016-04-29 4241

-

74LS138 有些图片看不到,在附件中2011-05-18 12678

-

74ls138真值表_74ls138功能表2011-03-20 10683

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 68311

-

74ls138引脚图-74ls138管脚图及功能真值表2007-12-17 194777

全部0条评论

快来发表一下你的评论吧 !