mpu内存保护单元寄存器种类及相关编程

ARM

描述

一些嵌入式系统使用多任务的操作和控制。这些系统必须提供一种机制来保证正在运行的任务不破坏其他任务的操作。即要防止系统资源和其他一些任务不受非法访问。嵌入式系统有专门的硬件来检测和限制系统资源的访问。它能保证资源的所有权,任务需要遵守一组由操作环境定义的、由硬件维护的规则,在硬件级上授予监视和控制资源程序的特殊权限。受保护系统主动防止一个任务使用其他任务的资源。因此使用硬件主动监视系统比协调加强的软件历程,提供了更好的保护。

内存保护单元(MPU)是ARM中配备的有效保护系统资源硬件的一种,提供了内存区域保护功能。

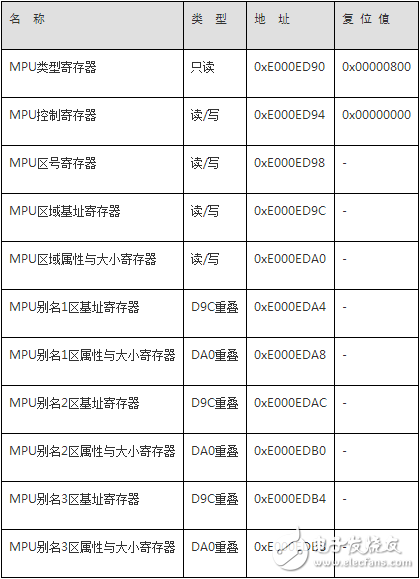

MPU寄存器

与MPU相关的协处理器寄存器主要是c2,c3,c5及c6。另外还有寄存器c1中的1到2位。

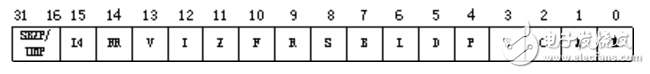

(1)c1中的MPU相关位

c1的编码格式如图所示。

M(bit[0])控制控制MPU的使能。

· M=0:禁止MPU

· M=1:使能MPU

A(bit[1])选择是否支持内存访问地址对齐检查。

· B=0:禁止地址对齐检查

· B=1:使能地址对齐检查

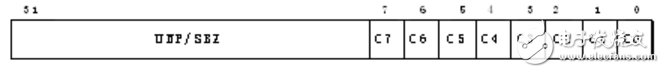

(2)c2中的MPU相关位

c2的编码格式如图所示。

寄存器位0~7分别对应域0~7的Cache属性。位8~31应该设置成0。

注意在数据和指令分离的系统中,通过MRC和MCR指令的第二个操作数《opcode2》来决定读写D-Cache和I-Cache属性。

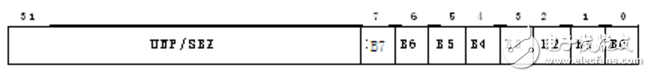

(3)c3中的MPU相关位

c3的编码格式如图所示。

寄存器位0~7分别对应域0~7的写缓存属性。位8~31应该设置成0。

当用指令MCR/MRC对c3进行读写时,第二个操作数《opcode2》将被忽略,在指令要设置成0。

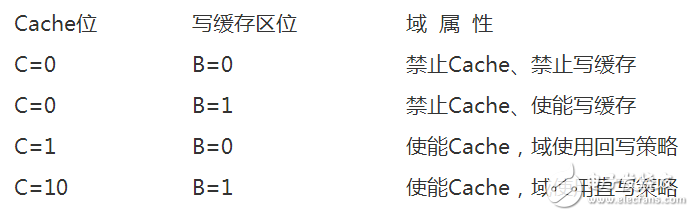

当配置数据域时,域的Cache位和写缓存区位一起决定域的访问策略。写缓存位有两个用途:使能/禁止域的写缓存和设置域的Cache写策略。域的Cache位控制写缓存位的作用。具体位分配见下表。

(4)访问权限寄存器c5

协处理器CP15的寄存器c5设置内存域的访问权限。

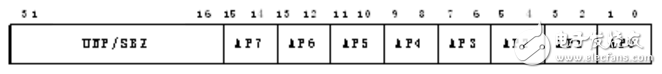

寄存器c5的编码格式如图所示。

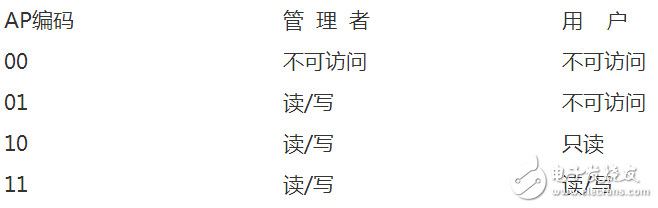

读寄存器c3的bits[15:0]存放域的AP(access permission,访问权限),其中bits[2n+1:2n]对于域n的访问权限。AP编码与访问权限的对应关系如下表所示。

对于Arm940T、Arm940T两个内核版本来说,使用MRC和MCR指令对其进行读写时,第二个协处理器寄存器《CRm》将被忽略,指令中以c0的形式出现。对于指令数据统一的域,第二操作数《opcode2》要设成0,而对于数据和指令分离的系统,如果opcode2=0,说明操作对数据域有效,如果opcode=1,说明操作对指令域有效。

注意对于Arm946E-S和Arm1026EJ-S两个内核版本,它们的访问权限机制更复杂,采用的是扩展AP,扩展组AP位域编码支持两个增强的权限域,对其进行操作的MRC和MCR指令形式更复杂,有关更详细的内容,请参加Arm公司的用户手册。

(5)域大小控制寄存器c6

Arm系统中通过写协处理器c6来定义域的大小,通过MCR指令中第二个操作寄存器赋不同的值来指示是对哪个具体域进行操作。第二个操作寄存器取值为c0~c7,分别对应域0~域7。

每个域的起始地址必须对齐到其大小的整数倍。比如,一个域的大小位64KB,其起始地址可以是0x10000的整数倍的任何数。域的大小可以是4KB~4GB的2的任意乘幂。

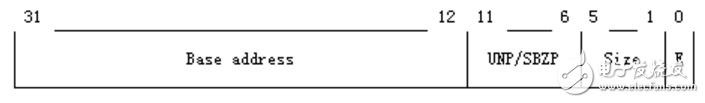

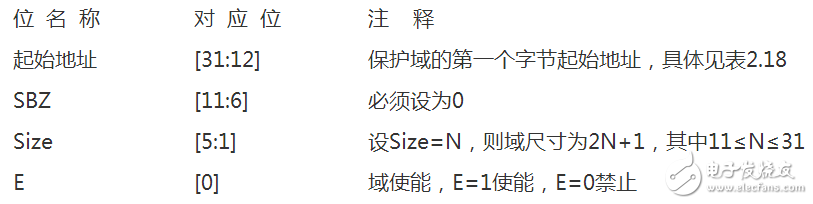

寄存器c6的编码格式如图所示。

编码含义如下表所示

关于c6中bits[31:12],因为域的起始要是域大小的整倍数,域最小为4KB,所有域起始地址的bits[11:0]通常为0,不用设置。

MPU编程

对MPU区域的编程,可通过对映射到内存的3个字寄存器的编程来实现。3个寄存器相互独立,程序可分开访问。MPU寄存器相互独立的特性,可以使用户方便地移植现有的ARMv6、ARMv7和CP15的代码,使Cortex-M3很容易地实现向后兼容。当移植ARMv6和CP15的现有代码时,只需使用LDRx和STRx操作代替MRC和MCR。

使用CP15等效代码更新MPU区域的代码实例如下:

R1 = region number

R2 = size/enable

R3 = attributes

R4 = address

MOV R0,#NVIC_BASE

ADD R0,#MPU_REG_CTRL

STR R1,[R0,#0] ;

STR R4,[R0,#4] ;

STRH R2,[R0,#8] ;

STRH R3,[R0,#10] ;

值得注意的是,如果中断在这期间可以抢占,那么它会受MPU区域的影响,即必须禁能、写然后再使能该区域。这对于上下文转换器通常没有太大用处,但是如果需要在其他地方进行更新,这就很有必要了。

MPU可以包含关键的数据,这是因为在更新时得花费一个以上的总线处理,通常是两个字,结果就不是“线程安全”了,即中断可以将两个字分离,使得区域包含不连续的信息。此时要注意以下两个问题。

(1)更新MPU通常会产生中断。这不仅是“读-修改-写”的问题,它还会对“保证中断程序不会修改相同区域”的情形造成影响。这是因为编程取决于正写入寄存器的区号,所以它知道要更新哪个区。因而这种情形下每个更新程序周围都必须禁能中断。

(2)使用域操作更新MPU会产生中断,该中断将使正在更新的区域受到影响,因为只有基址或“大小域”被更新。如果新的大小域发生了改变,但是基址没有变,那么基址 +new_size可能会在一个被另外区域正常处理的区域内重叠。

但是对于标准的OS上下文转换代码,将会改变用户区域,因为这些区域会被预设成用户特权和用户区地址,所以没有风险。也就是说即使是中断也不会产生副作用。因此不需要禁能/使能代码,也不需要禁止中断。

最普通的方法是只从两个位置对MPU进行编程:引导代码和上下文转换器。如果以唯一的两个位置进行编程,且上下文转换器仅更新用户区,那么因为上下文转换器已经是一个关键区域,且引导代码在禁能中断时运行,所以不需要禁能。

-

如何管理STM32产品中的内存保护单元(MPU)2023-09-07 656

-

Armv8-M内存模型与内存保护用户指南2023-08-02 893

-

如何管理STM32产品中的内存保护单元(MPU)2023-08-01 733

-

什么是MPU?MPU在哪些方面保护内存安全?2023-06-12 14703

-

如何为MPC5744P配置内存保护单元?2023-04-04 837

-

管理STM32 MCU中的内存保护单元2022-12-23 1672

-

应用笔记|管理STM32 MCU中的内存保护单元2022-12-21 2337

-

管理 STM32 MCU 中的内存保护单元2022-11-21 592

-

CPU、寄存器和内存单元的物理结构2022-09-05 5906

-

为什么要使用MPU?MPU如何实现内存保护?2022-07-05 7521

-

主要讲armv7-m架构下的MPU内存保护单元2022-04-08 5448

-

Cortex-M内核的MPU内存保护单元2020-03-04 4932

-

MPU6050寄存器的各种类型详细说明2019-08-08 3510

全部0条评论

快来发表一下你的评论吧 !